- •1. ИНФОРМАЦИЯ, ЕЁ СВОЙСТВА, ИЗМЕРЕНИЕ, ПРЕДСТАВЛЕНИЕ И КОДИРОВАНИЕ

- •1.1. Информатика – предмет и задачи

- •1.2. Информация, ее виды и свойства

- •1.3. Представление об информационном обществе

- •1.4. Кодирование информации

- •1.5. Практическое занятие № 1. Системы счисления. Перевод чисел из одной системы счисления в другую. Арифметические операции в позиционных системах счисления

- •1.6. Кодирование текстовых и символьных данных

- •1.7. Кодирование графических данных

- •1.8. Кодирование звуковой информации

- •1.9. Структуры данных

- •1.10. Файлы и файловая структура

- •1.11. Измерение и представление информации

- •1.12. Теоремы Шеннона

- •1.13. Математические основы информатики

- •1.13.1. Алгебра высказываний (алгебра логики)

- •1.13.2. Элементы теории множеств

- •2. ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА

- •2.1. История развития вычислительной техники

- •2.2. Классификация компьютеров по сферам применения

- •2.3. Базовая система элементов компьютерных систем

- •2.4. Функциональные узлы компьютерных систем

- •2.5. Архитектура ЭВМ

- •2.6. Совершенствование и развитие архитектуры ЭВМ

- •2.6.1. Архитектуры с фиксированным набором устройств

- •2.6.2. Открытая архитектура

- •2.6.3. Архитектура многопроцессорных вычислительных систем

- •2.7. Внутренняя структура ЭВМ

- •2.7.4. Внешние запоминающие устройства

- •2.8. Внешние устройства компьютера

- •2.8.1. Видеотерминалы

- •2.8.2. Устройства ручного ввода информации

- •2.8.3. Устройства печати

- •2.8.4. Устройства поддержки безбумажных технологий

- •2.8.5. Устройства обработки звуковой информации

- •2.8.6. Устройства для соединения компьютеров в сеть

- •3. ПРОГРАММНОЕ ОБЕСПЕЧЕНИЕ ЭВМ

- •3.1. Состав системного программного обеспечения

- •3.2. Операционные системы

- •3.3. Виды операционных систем и их базовые понятия

- •3.4. Процессы и потоки

- •3.5. Управление памятью

- •3.6 Организация ввода-вывода

- •3.7 Драйверы устройств

- •3.8 Файловые системы

- •3.9 Файловые системы Microsoft Windows

- •3.9.1. Файловая система FAT16

- •3.9.3. Файловая система NTFS

- •3.9.4. Сравнение файловых систем FAT16, FAT32 и NTFS

- •3.10 Операционная система Windows

- •3.11 Служебные программы

- •3.13 Прикладное программное обеспечение

- •3.13.1. ППО общего назначения

- •3.13.2. ППО специального назначения

- •3.17. Практическое занятие № 6. Табличный процессор Excel. Основные понятия и общие принципы работы с электронной таблицей. Создание и заполнение таблиц постоянными данными и формулами. Построение диаграмм и графиков

- •3.18. Практическое занятие № 7. Табличный процессор Excel. Сортировка и фильтрация (выборка) данных. Сводные таблицы, структурирование таблиц. Расчёты в Excel

- •4. БАЗЫ ДАННЫХ (БД) И СИСТЕМЫ УПРАВЛЕНИЯ БАЗАМИ ДАННЫХ (СУБД)

- •4.1. Базы данных в структуре информационных систем

- •4.2. Классификация баз данных и виды моделей данных

- •4.3. Нормализация отношений в реляционных базах данных

- •4.4. Проектирование баз данных

- •4.5. Этапы развития СУБД. Реляционная СУБД Microsoft Access – пример системы управления базами данных

- •4.6. Практическое занятие № 8. СУБД Access 97. Создание однотабличной базы данных. Отбор данных с помощью фильтра. Формирование запросов и отчётов для однотабличной базы данных

- •5. КОМПЬЮТЕРНЫЕ СЕТИ И ОСНОВЫ ЗАЩИТЫ ИНФОРМАЦИИ

- •5.1. Назначение и классификация компьютерных сетей

- •5.2. Режимы передачи данных в компьютерных сетях

- •5.3. Типы синхронизации данных при передаче и способы передачи информации

- •5.4. Аппаратные средства, применяемые при передаче данных

- •5.5. Архитектура и протоколы компьютерных сетей

- •5.6. Локальные вычислительные сети (ЛВС) и их топологии

- •5.7. Физическая передающая среда ЛВС и методы доступа к ней

- •5.8. Примеры сетей. Глобальная сеть Интернет

- •5.9. Службы сети Интернет

- •5.10. Поиск информации в Интернет

- •5.10.1. Поисковые машины

- •5.12. Основы и методы защиты информации

- •5.13. Политика безопасности в компьютерных сетях

- •5.14. Способы и средства нарушения конфиденциальности информации

- •5.15. Основы противодействия нарушению конфиденциальности информации

- •5.16. Криптографические методы защиты данных

- •5.17. Компьютерные вирусы и меры защиты информации от них

- •6. ОСНОВЫ АЛГОРИТМИЗАЦИИ И ТЕХНОЛОГИИ ПРОГРАММИРОВАНИЯ. МОДЕЛИ И ИНФОРМАЦИОННОЕ МОДЕЛИРОВАНИЕ

- •6.1. Алгоритм и его свойства

- •6.1.2. Графическое представление алгоритмов

- •6.2. Принципы разработки алгоритмов и программ для решения прикладных задач

- •6.2.1. Процедурное программирование

- •6.2.3. Функциональное программирование

- •6.2.4. Логическое программирование

- •6.2.5. Объектно-ориентированное программирование (ООП)

- •6.3. Методы и искусство программирования

- •6.4. Обзор языков программирования

- •6.5. Понятие о метаязыках описания языков программирования

- •6.6. Моделирование как метод решения прикладных задач

- •6.7. Основные понятия математического моделирования

- •6.8. Информационное моделирование

- •6.9. Практическое занятие № 11. Вычисления в среде Mathcad

- •6.10. Практическое занятие № 12. Вычисления в среде Matlab

- •СПИСОК ЛИТЕРАТУРЫ

- •ОГЛАВЛЕНИЕ

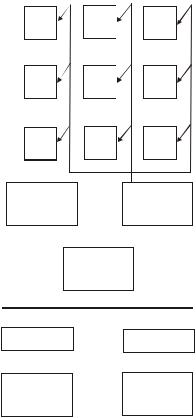

Наиболее сложную архитектуру имеют матричные вычислительные системы (см. рис.

|

|

|

Процес- |

|

|

Процес- |

|

|

Процес- |

2.10). В них используется несколько процессоров, объединён- |

||||||||||||

|

|

|

элемент |

|

|

элемент |

|

|

элемент |

ных в матрицу процессорных элементов. Каждый процессор |

||||||||||||

|

|

|

сорный |

|

|

|

|

сорный |

|

|

|

|

|

сорный |

снабжён локальной памятью и при необходимости может про- |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

изводить обмен со своими соседями или с общим запоминаю- |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Процес- |

||||

|

|

|

Процес- |

|

|

Процес- |

|

|

щим устройством. В первом случае программы и данные не- |

|||||||||||||

|

|

|

сорный |

|

|

|

|

сорный |

|

|

|

|

|

сорный |

||||||||

|

|

|

элемент |

|

|

элемент |

|

|

элемент |

скольких задач или независимых частей одной задачи загру- |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

жаются в локальную память процессоров и выполняются па- |

||

|

|

|

Процес- |

|

|

Процес- |

|

|

Процес- |

раллельно, |

во втором случае процессоры одновременно вы- |

|||||||||||

|

|

|

сорный |

|

|

|

сорный |

|

|

|

|

сорный |

полняют одну и ту же команду, но над разными данными. Об- |

|||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

элемент |

|

|

элемент |

|

|

элемент |

|||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

мен данными с периферийными устройствами выполняется |

||

|

|

|

Общее |

|

|

|

|

|

|

|

|

Устройство |

через периферийный процессор, подключённый к общему за- |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

обработки |

поминающему устройству. |

||||||||||

|

|

|

|

ЗУ |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

команд |

||||||||||

|

|

|

|

|

|

|

|

Периферий- |

|

|

|

|

|

2.7. Внутренняя структура ЭВМ |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

ный процес- |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

сор |

|

|

|

|

2.7.1. Центральный процессор. Центральный процес- |

|||||||

Шина |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

сор (CPU, Central Processing Unit) – функционально закончен- |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ное программно-управляемое устройство обработки информа- |

||

Контроллер |

|

|

|

|

|

|

|

|

Контроллер |

|||||||||||||

|

|

|

|

|

|

|

|

ции, выполненное на одной или нескольких СБИС. Централь- |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ный процессор в общем случае содержит: |

||

Устройство |

|

|

|

|

|

|

|

|

Устройство |

§ |

арифметико-логическое устройство; |

|||||||||||

|

|

|

|

|

|

|

|

§ шины данных и шины адресов; |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Рис. 2.10. Матричная архитектура ЭВМ |

§ |

регистры; |

||||||||||||||||||||

§ |

счетчики команд; |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

§кэш – очень быструю память малого объёма;

§математический сопроцессор чисел с плавающей точкой.

Современные процессоры выполняются в виде микропроцессоров. Первый микропро- цессор Intel 4004 был создан фирмой Intel в ноябре 1971 г. Он состоял из 2250 транзисторов, размещенных на кристалле размером не более шляпки гвоздя. В апреле 1974 г. компания Intel совершила новый качественный скачок: был создан первый универсальный восьмираз- рядный микропроцессор 8080 с 4500 транзисторами. С тех пор развитие микропроцессорной техники происходило поистине с фантастической скоростью: современный микропроцессор Pentium 4 содержит около 30 млн. транзисторов, т. е. является очень сложным техническим устройством.

С точки зрения потребителей, процессоры характеризуются двумя основными пара- метрами: разрядностью и быстродействием. Разрядность определяет, прежде всего, коли- чество разрядов обрабатываемых процессором данных. Быстродействие процессора зависит от ряда факторов, среди которых основными являются тактовая частота – величина, об- ратная количеству элементарных действий процессора за одну секунду, и количество тактов, затрачиваемых на выполнение одной команды.

В современных персональных компьютерах различных фирм применяются процессо- ры двух основных архитектур:

§полная система команд переменной длины – Complex Instruction Set Computer (CISC);

§сокращенный набор команд фиксированной длины – Reduced Instruction Set

Computer (RISC).

Обе архитектуры имеют свои преимущества и недостатки. CISC – процессоры имеют обширный набор команд, что позволяет программисту выбрать наиболее подходящую в дан- ном случае. Недостатком этой архитектуры является сложное внутреннее устройство про- цессоров и увеличенное время выполнения микрокоманды на микропрограммном уровне. Команды имеют разную длину и время исполнения.

68

Процессор RISC – архитектуры работает необычайно быстро и способен выполнить любую из своих немногочисленных команд за один машинный такт, в то время как обычно на выполнение простой операции требуется 4-5 тактов. Так как RISC – архитектура опериру- ет очень ограниченным набором команд, то если нужной команды не оказывается, её прихо- диться реализовывать с помощью нескольких команд из имеющегося набора, что увеличива- ет размер командного кода.

Микропроцессор осуществляет следующие основные функции:

§выборку команд из ОЗУ;

§декодирование команд, т. е. определение их назначения;

§выполнение операций, закодированных в командах;

§управление пересылкой информации между своими внутренними регистрами, оперативной памятью и внешними устройствами;

§обработку внутри процессорных и программных прерываний;

§обработку сигналов от внешних устройств и реализацию соответствующих прерываний;

§управление различными устройствами, входящими в состав компьютера.

Что же представляет собой микропроцессор с точки зрения программиста? Для про- граммиста любой процессор состоит из набора регистров памяти различного назначения, ко- торые определённым образом связаны между собой и обрабатываются в соответствии с не- которой системой правил. Наиболее важными регистрами микропроцессора являются счет-

чик адреса команд, указатель стека и регистр состояния.

Роль счетчика команд состоит в сохранении адреса очередной команды программы и автоматическом вычислении адреса следующей. В указателе стека хранится адрес начала специальным образом организуемого участка памяти. Наконец, в регистре состояния хранят-

ся сведения о текущих режимах работы процессора и информация о результатах выполнения команд. Например, равен ли результат нулю, отрицателен ли он, не возникли ли ошибки в ходе операции и т. п. Помимо рассмотренных, каждый микропроцессор имеет набор рабочих регистров, в которых хранятся текущие обрабатываемые данные или их адреса в ОЗУ. У не- которых процессоров рабочие регистры функционально равнозначны, в других назначение регистров достаточно жёстко оговаривается.

Всё адресное пространство микропроцессора состоит из множества адресов памяти ОЗУ, из которых он может брать информацию или засылать её. При обмене информацией с памятью процессор обращается к ячейкам ОЗУ по их номерам. Способы задания требуемых адресов в командах ЭВМ называются методами адресации. Если адрес находится в самой команде, то адресация называется прямой. В этом случае сильно возрастает длина команды и, чтобы избежать этого, используют метод косвенной адресации. Он состоит в том, что ад- рес памяти предварительно заносится в один из регистров микропроцессора, а в команде со- держится лишь ссылка на этот регистр.

Приведём наиболее распространённые варианты адресации:

§данные находятся в одном из регистров микропроцессора;

§данные входят непосредственно в состав команды, т. е. размещаются после ко- да операции;

§данные находятся по адресу ОЗУ, а сам этот адрес содержится в одном из ре- гистров микропроцессора;

§данные находятся по адресу, который вычисляется по формуле адрес = базо-

вый адрес + смещение.

Базовый адрес хранится в одном из регистров, а смещение может быть либо некото- рой константой, либо содержимом другого регистра. Часто такой способ доступа к ОЗУ на- зывают индексным, т. к. это похоже на нахождение элемента в одномерном массиве по его индексу.

Применяются и более экзотические методы адресации, например, сегментный и сте- ковый методы. При сегментном способе адресации адрес ОЗУ вычисляется как сумма двух

69

чисел (сегмента и смещения), причем одно из них сдвинуто влево на четыре двоичных раз- ряда. Таким способом удаётся адресовать память большего объёма, чем позволяет длина ис- пользуемого адреса. Стек – это неявный способ адресации, при котором информация запи- сывается и считывается только последовательным образом. Стек является простейшей дина- мической структурой. Добавление информации в стек и выборка из него выполняются из од- ного конца, называемого вершиной стека. Другие операции со стеком не определены. При выборке информация исключается из стека. Для работы со стеком используются две пере- менные: указатель на вершину стека и вспомогательный указатель, определяющий длину те- кущей информации в стеке. Таким образом, та информация, которая заносится в стек первой, извлекается последней, и наоборот. Стековый способ организации ОЗУ используется в вы- числительной технике очень широко.

Важную роль в работе микропроцессора играют прерывания. События, вызывающие прерывания делятся на две группы: фатальные и нефатальные. Фатальные события влекут прекращение выполнения программы, реакция не нефатальные события может быть отложе- на. Например, сложение с переполнением разрядной сетки – фатальное событие, после кото- рого остановка неизбежна; попытка вывода на принтер, не готовый к приёму информации, может быть отложена.

Основные виды прерываний – внутрипроцессорные прерывания и прерывания от внешних устройств. Первые связаны с возникновением непреодолимого препятствия при выполнении программы. Далее управление передаётся системе, обеспечивающей прохожде- ние задач (чаще всего это операционная система). Прерывания второго вида возникают по требованиям какого-либо из внешних устройств. Это вполне нормальная ситуация при рабо- те ЭВМ. При обработке такого прерывания микропроцессор обычно выполняет следующие действия:

§запоминает в стеке текущее состояние счётчика команд и содержимое регистра состояния;

§передаёт управление на программу обработки данного прерывания;

§после её выполнения восстанавливает из стека значения своих регистров и продолжает выполнение прерванной программы.

Кчислу нефатальных относятся и специальные отладочные прерывания. Такие пре-

рывания обеспечивают возможность пошагового исполнения тестируемой программы под контролем специальных программных средств. Нефатальные прерывания можно запретить.

Запрет прерывания называется маскировкой и задаётся программистом или специальной программой.

Способ обмена микропроцессора с внешними устройствами может быть одним из двух следующих:

§устройства ввода-вывода включаются в общее адресное пространство;

§устройства ввода-вывода имеют своё собственное адресное пространство.

В первом случае при обращении к определённым адресам памяти вместо обмена с ОЗУ происходит аппаратное подключение того или иного внешнего устройства. При этом для “общения” с внешними устройствами и памятью используются одни и те же команды микропроцессора. Во втором случае внешние устройства образуют отдельное адресное про- странство, обычно значительно меньшее, чем ОЗУ. Каждый адрес этого дополнительного пространства называется портом. Каждому внешнему устройству соответствует несколько портов с последовательными адресами. Различают последовательные и параллельные ком- муникационные порты. Последовательный порт обменивается данными с процессором по- байтно, а с внешними устройствами побитно. Параллельный порт получает и посылает дан- ные побайтно. Обмен процессора с организованными подобным образом устройствами осу- ществляется специальными командами ввода-вывода.

2.7.2. Оперативное запоминающее устройство. Память, в которой хранятся испол-

няемые программы и данные, называется оперативным запоминающим устройством (ОЗУ), или RAM (Random Access Memory) – памятью со свободным доступом. ОЗУ позволяет запи-

70

сывать и считывать информацию из адреса памяти, обращаясь к нему по его номеру. Адрес памяти имеет стандартное число двоичных разрядов, обычно размер ячейки ОЗУ равен од- ному байту. Информация в ОЗУ сохраняется всё время, пока на схему памяти подаётся пита- ние, т. е. она является энергозависимой.

Существуют два вида ОЗУ: динамическое ОЗУ, или DRAM (Dynamic RAM), и стати- ческое ОЗУ, или SRAM (Static RAM). Разряд динамического ОЗУ построен на одном транзи- сторе и конденсаторе и представляет информационный бит. Из-за токов утечки такие кон- денсаторы быстро разряжаются, и их периодически (примерно каждые 2 миллисекунды) подзаряжают специальные устройства. Этот процесс называется регенерацией памяти. При

записи или чтении из такого устройства требуется время для накопления или стекания заряда на конденсаторе. Поэтому быстродействие динамического ОЗУ на порядок ниже, чем у ста- тического. Статическая (или кэш-память, cache - запас) работает практически с той же ско- ростью, что и процессор. Конструктивно элемент статической памяти представляет собой триггер на четырёх или шести транзисторах. Кэш-память может быть как встроенной в про- цессор, так и отдельной от него микросхемой, устанавливаемой на системной плате. Емкость статических ОЗУ значительно меньше, чем у динамических, кроме того, они более энергоём- ки и значительно дороже. Обычно статическое ОЗУ используется в качестве небольшой бу- ферной сверхбыстродействующей памяти. В современных процессорах кэш-память делится на уровни. На кристалле самого процессора находится кэш-память первого уровня, она имеет ёмкость 16-128 Кбайт и скорость, равную скорости процессора. В корпусе процессора на от- дельном кристалле находится кэш-память второго уровня объёмом 256 Кбайт и более. Нако- нец, память третьего уровня расположена на системной плате, её ёмкость может достигать

1000 Мбайт.

В одном адресном пространстве с ОЗУ находится специальная память, предназначен- ная для постоянного хранения таких программ, как тестирование и начальная загрузка ком- пьютера, управление внешними объектами. Эта память называется постоянным запоминаю- щим устройством (ПЗУ) или ROM (Read Only Memory) и является энергонезависимой. Бы- вают два вида ПЗУ: программируемое однократно и перепрограммируемое ПЗУ. Память первого типа не позволяет изменять записанную в неё информацию, из такой памяти можно только читать. Память второго типа допускает многократную перезапись своего содержимо- го, стирание хранящейся информации осуществляется электрическим сигналом повышенной мощности.

2.7.3. Внутренние шины передачи данных. Шина – это устройство, обеспечиваю-

щее связь центрального процессора с периферийными устройствами компьютера. Сущест- вуют общая и периферийные шины. Общая шина делится на три отдельные шины по типу передаваемой информации: шину адреса, шину данных и шину управления. Каждая шина характеризуется числом параллельных проводников для передачи информации. Эта характе- ристика называется шириной шины. Другой важной характеристикой является тактовая частота шины – это частота формирования циклов передачи информации. На этой частоте работает контроллер шины.

Шина адреса предназначена для передачи адреса памяти или адреса порта ввода- вывода. Если ширина шины равна n , то количество адресуемой памяти равно 2n . Шина данных передаёт команды и данные, её ширина составляет обычно 32÷64 проводников. Ши-

рина шины управления определяется алгоритмом её работы или иначе протоколом работы шины. Примерный протокол работы шины таков. Первый такт работы инициируется процес- сором, который выставляет на шину адреса адрес внешнего порта или адрес памяти и управ- ляющие сигналы, определяющие вид обмена. На втором такте процессор ждёт от устройства сигнала о готовности к приёму или передаче информации. Второй такт может повторяться до тех пор, пока не будет получен сигнал о готовности устройства. На третьем такте процессор

выставляет на шину данных передаваемую информацию при записи или открывает шину данных для приёма информации. Наконец, на четвёртом такте происходит собственно обмен.

71