- •Раздел I. Введение. Общие сведения о цифровых автоматах Лекция 1. Основные понятия и определения.

- •Раздел 2. Синтез цифровых автоматов без памяти

- •Преобразование функции в минимальную конъюнктивную нормальную форму (кнф).

- •Раздел 3. Общая теория конечных цифровых автоматов с памятью. Лекция 4. Основные понятия и определения.

- •Элементарный автомат

- •Диаграмму Вейча

- •Граф d-триггера

- •Матрица переходов rs-триггера:

- •Матрица переходов jk-триггера:

- •Перерисованная совмещенная таблица переходов и выходов

- •Диаграммы Вейча

- •Двухступенчатый триггер

- •Раздел 4.Синтез типовых узлов эвм

- •Кодированная таблица переходов и функций возбуждения

- •Минимальные дизъюнктивные нормальные формы функций возбуждения триггеров

- •Регистр сдвига

- •Временная диаграмма

- •Асинхронный вычитающий счетчик

- •Асинхронный реверсивный счетчик

- •Диаграммы Вейча

- •Счетчик на синхронных т-триггерах

- •Счетчик со сквозным переносом

- •Организация цепей сквозного переноса

- •Диаграммы Вейча

- •Синхронный пятеричный счетчик

- •Счетчик на кольцевых сдвигающих регистрах

- •Счетчик Джонсона

- •По матрице построим схему счетчика:

- •Дешифратор с парафазными входами

- •Линейный дешифратор

- •Принцип построения пирамидального дешифратора на 16 выходов

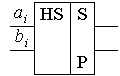

- •Полусумматор

- •Кроме сумматоров существуют полусумматоры, которые осуществляют сложение двух чисел с формированием сигналов суммы и переноса.

- •Диаграммы Вейча

- •Сумматор комбинационно-накапливающего типа

- •Последовательный сумматор

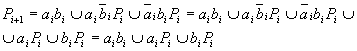

- •В свою очередь:

- •Раздел 5. Лекция 13. Абстрактный синтез конечных автоматов

- •Регулярным выражением:

- •Раздел 6. Лекция 15. Вероятностные автоматы

Полусумматор

Кроме сумматоров существуют полусумматоры, которые осуществляют сложение двух чисел с формированием сигналов суммы и переноса.

Лекция 12. Одноразрядный комбинационный сумматор

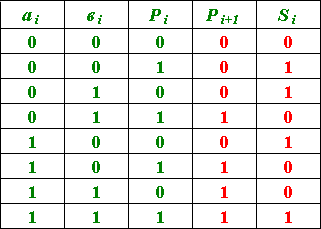

Закон функционирования такого сумматора при сложении трех цифр определяется следующей таблицей.

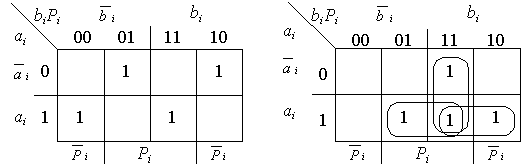

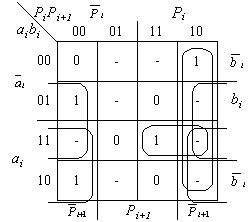

На основании таблицы строятся диаграммы Вейча и получаются минимальные ДНФ функций Si и Pi+1

Диаграммы Вейча

![]() ,

,

![]() .

.

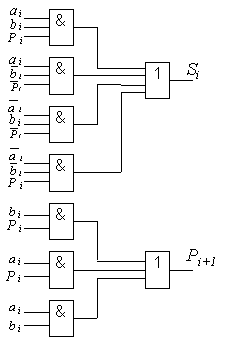

По полученным уравнениям можно построить двухуровневую схему одноразрядного комбинационного сумматора.

Полученную схему можно упростить, если рассматривать Si как функцию 4-х переменных Si=Si(аi,вi,Pi,Pi+1).

Отсюда

имеем:

![]()

![]() .

.

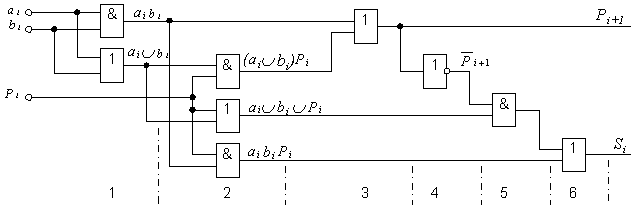

Первая схема, имеющая парафазные входы, обладает большим быстродействием, т.к. число уровней здесь r=2, суммарное число входов у логических элементов равно в1=25.

Схема с парафазными входами

Вторая схема, имеющая однофазные входы, обладает худшим быстродействием, т.к. r=6. Суммарное число входов равно здесь в2=17, т.е. последняя схема несколько проще.

Схема с однофазными входами

Схема с однофазными входами на элементах И-НЕ и ИЛИ-НЕ имеет вид:

Число уровней r=5, суммарное число входов равно в3=19, В зависимости от назначения и следует использовать ту или иную схему.

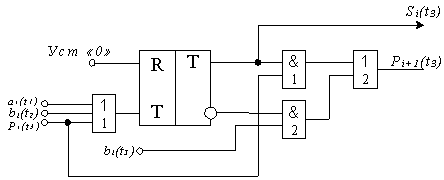

Одноразрядный накапливающий сумматор

Одноразрядным сумматором накапливающего типа является схема, суммирующая поочередно поступающие на ее вход цифры слагаемого и переноса с запоминанием результата суммирования. Для запоминания результата сложения на выходе рассмотренных комбинационных сумматоров можно установить триггеры памяти (триггера R-S и D-типов). Совместно с триггером памяти комбинационный сумматор будет выполнять функции накапливающего сумматора.

Роль накапливающего сумматора может выполнять и счетный триггер со схемой формирования переноса, на счетный вход которого все слагаемые должны подаваться последовательно во времени. Суммирование трех слагаемых будет проходить поэтому за три такта.

В

первый момент времени t1

через схему ИЛИ1

на вход Т-триггера,

который был предварительно установлен

в нулевое состояние, поступает цифра

ai

и запоминается. После завершения

переходных процессов в триггере в момент

времени t2

через схему ИЛИ1

поступает

цифра вi

второго слагаемого. При этом Т-триггер

реализует функцию

![]() .

Наконец в следующий момент времени t3

через схему ИЛИ1

подается

цифра

переноса из более младшего разряда Pi

и триггер реализует функцию:

.

Наконец в следующий момент времени t3

через схему ИЛИ1

подается

цифра

переноса из более младшего разряда Pi

и триггер реализует функцию:

![]()

![]() ,

которая совпадает с функцией Si,

полученной ранее по таблице истинности

одноразрядного сумматора. Таким образом,

по истечении трех тактов в триггере

будет находится значение i-ого

разряда суммы слагаемых А

и В,

т.е. Si.

,

которая совпадает с функцией Si,

полученной ранее по таблице истинности

одноразрядного сумматора. Таким образом,

по истечении трех тактов в триггере

будет находится значение i-ого

разряда суммы слагаемых А

и В,

т.е. Si.

Сигнал

переноса Pi+1

формируется

комбинационной схемой, стоящей на выходе

триггера. В момент времени t3,

когда триггер еще находится в состоянии

f1,

приходит сигнал Pi.

На выходе И1

имеем

![]() .

Если теперь к f3

добавить через дизъюнкцию ai×bi,

то получится Pi+1.

Непосредственно ai×bi

получить с помощью конъюнктора нельзя,

т.к. они поступают в различные дискретные

моменты времени. Поэтому ai×bi

формируются с помощью элемента И2

реализующего функцию

.

Если теперь к f3

добавить через дизъюнкцию ai×bi,

то получится Pi+1.

Непосредственно ai×bi

получить с помощью конъюнктора нельзя,

т.к. они поступают в различные дискретные

моменты времени. Поэтому ai×bi

формируются с помощью элемента И2

реализующего функцию

![]() .

.

Окончательно,

сигнал переноса Pi+1

на выходе ИЛИ2

равен

Этот сигнал совпадает с сигналом, формируемом в комбинационном сумматоре на выходе Pi+1 .

Недостаток рассмотренного сумматора заключается в том, что он имеет малое быстродействие, поскольку в каждом цикле суммирования число срабатываний триггера может равняться четырем (Уст «0», ai(t1), bi(t2), Pi(t3)).

Достоинство накапливающего сумматора по сравнению с комбинационным состоит в более простой организации суммирования с накоплением результата, благодаря его способности к запоминанию. Полученная сумма сохраняется в сумматоре и после снятия входных сигналов.

Комбинационно-накапливающий одноразрядный сумматор

Положительные свойства сумматоров накапливающего и комбинационного типов сочетает в себе сумматор комбинационно-накапливающего типа, в котором сигнал переноса вырабатывается комбинационной схемой, а сумма образуется в Т-триггере, на счетный вход которого с помощью другой комбинационной схемы подается результат сложения по модулю два цифр второго слагаемого и переноса.