- •Раздел I. Введение. Общие сведения о цифровых автоматах Лекция 1. Основные понятия и определения.

- •Раздел 2. Синтез цифровых автоматов без памяти

- •Преобразование функции в минимальную конъюнктивную нормальную форму (кнф).

- •Раздел 3. Общая теория конечных цифровых автоматов с памятью. Лекция 4. Основные понятия и определения.

- •Элементарный автомат

- •Диаграмму Вейча

- •Граф d-триггера

- •Матрица переходов rs-триггера:

- •Матрица переходов jk-триггера:

- •Перерисованная совмещенная таблица переходов и выходов

- •Диаграммы Вейча

- •Двухступенчатый триггер

- •Раздел 4.Синтез типовых узлов эвм

- •Кодированная таблица переходов и функций возбуждения

- •Минимальные дизъюнктивные нормальные формы функций возбуждения триггеров

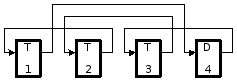

- •Регистр сдвига

- •Временная диаграмма

- •Асинхронный вычитающий счетчик

- •Асинхронный реверсивный счетчик

- •Диаграммы Вейча

- •Счетчик на синхронных т-триггерах

- •Счетчик со сквозным переносом

- •Организация цепей сквозного переноса

- •Диаграммы Вейча

- •Синхронный пятеричный счетчик

- •Счетчик на кольцевых сдвигающих регистрах

- •Счетчик Джонсона

- •По матрице построим схему счетчика:

- •Дешифратор с парафазными входами

- •Линейный дешифратор

- •Принцип построения пирамидального дешифратора на 16 выходов

- •Полусумматор

- •Кроме сумматоров существуют полусумматоры, которые осуществляют сложение двух чисел с формированием сигналов суммы и переноса.

- •Диаграммы Вейча

- •Сумматор комбинационно-накапливающего типа

- •Последовательный сумматор

- •В свою очередь:

- •Раздел 5. Лекция 13. Абстрактный синтез конечных автоматов

- •Регулярным выражением:

- •Раздел 6. Лекция 15. Вероятностные автоматы

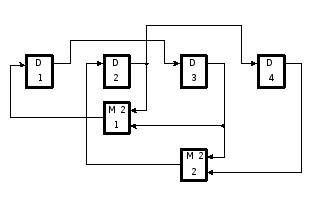

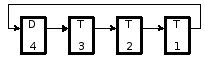

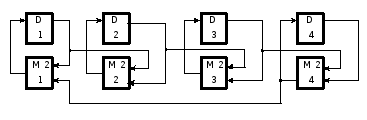

По матрице построим схему счетчика:

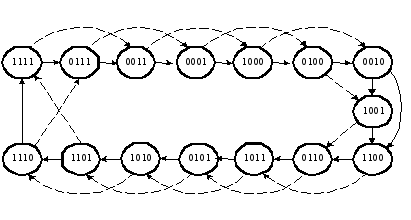

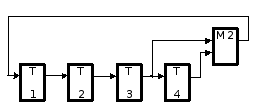

Последовательность состояний регистра сдвига при s = 2 (пунктирные линии) и при s = 1 (сплошные линии) показаны на рисунке.

Как видно из рисунка, счетчик также формирует М-последовательность. Возьмем s = 3. Матрица функционирования счетчика в этом случае имеет вид:

.

.

Рассмотрим схему счетчика при s = 3:

В данном случае D-триггер и сумматор по модулю два в его обратной связи представляют собой T-триггер. Следовательно, эту схему можно преобразовать следующим образом, т.е. она может быть построена только на D- и T-триггерах, соединенных в кольцо.

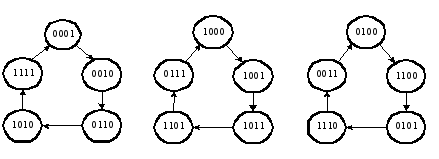

Здесь необходимо отметить, что для того, чтобы каждый выходной разряд счетчика также формировал последовательности максимальной длины, необходимо, чтобы число шагов s и период последовательности M были взаимно простыми числами, т.е. (M, s) = 1. Поскольку в данном примере это условие не выполняется, диаграмма последовательности состояний регистра разбивается на несколько периодов меньшей длины:

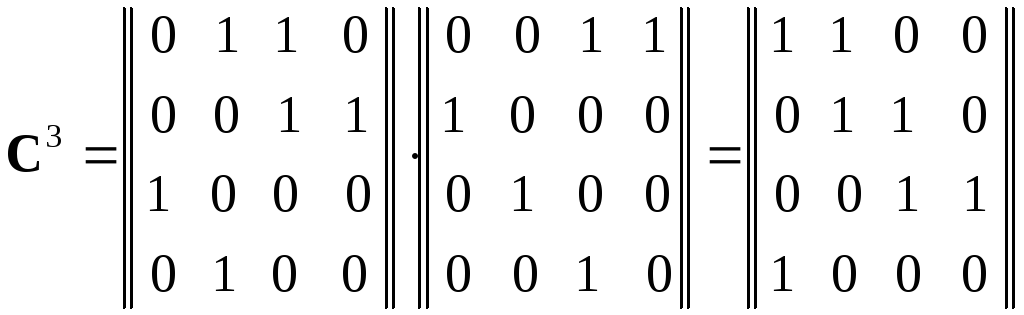

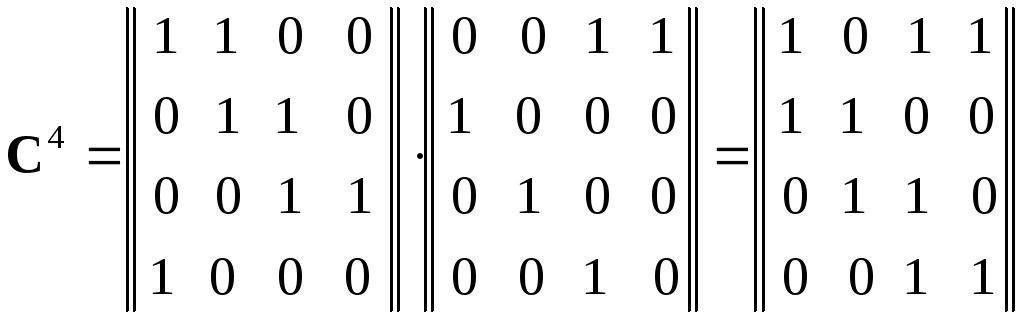

Пусть s = 4. Матрица в этом случае имеет вид:

.

.

Схема счетчика приведена на рисунке.

Эта схема может быть построена только на Т-триггерах и одном сумматоре по модулю два:

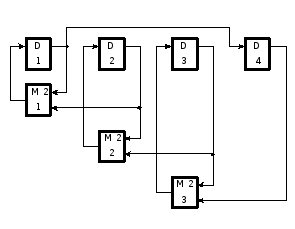

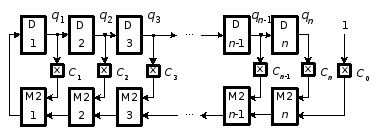

В общем случае схема полиномиального счетчика на основе n-разрядного регистра сдвига с линейными обратными связями, представлена на рисунке.

Если коэффициент Ci = 1, то выход i-го триггера подается на вход сумматора по модулю 2, если же Ci =0, то – не подается. В соответствии с коэффициентами многочлена однозначно определяется структура обратной связи регистра сдвига. Есть таблица всех неприводимых многочленов, из которой находят многочлены, представленые в 8-ричной форме.

Например,

характеристический многочлен

![]() =x4

=x4

![]() x

x

![]() 1

в этой таблице будет иметь следующий

вид:

1

в этой таблице будет иметь следующий

вид:

![]() = 1

= 1![]() .

.

В двоичном виде этом многочлен запишется как: 10 011, или в 8-ричном виде – 23. По такой записи многочлена однозначно строится схема полиномиального счетчика.

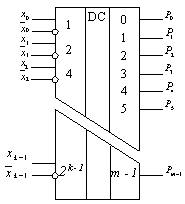

Лекция 11. Дешифраторы

Дешифратор представляет собой комбинационную схему с n входами и m выходами. Назначение дешифраторов – обеспечить на каждом из выходов сигнал, равный единицы, только при вполне определенной комбинации входных сигналов. Пусть входные шины дешифратора пронумерованы целыми числами, начиная с нуля. Тогда при подаче на входы дешифратора сигналов, соответствующих k-разрядному двоичному числу L, единичный выходной сигнал появится на L-ом выходе. Например. Пусть на входы дешифратора подается комбинация сигналов 1100(2)=12(10). Тогда единичный сигнал появится только на 12-ом выходе дешифратора, а на остальных выходах будут нулевые сигналы. Максимальное число выходов дешифратора равно m=2k. Дешифраторы, имеющие максимальное число выходов при данном k, называются полными. Здесь k-разрядность дешифрируемого числа.

Дешифраторы ставятся на выходах регистров и счетчиков. При этом они преобразуют двоичный код числа на регистре в управляющий сигнал на одном из своих выходов. Причем код числа может подаваться как в однофазном коде (n=k), так и в парафазном (n=2k). В последнем случае с выхода регистра (счетчика) на входы дешифратора поступают как прямые, так и инверсные сигналы. На структурных схемах дешифратор обозначается следующим образом (с парафазными входами):

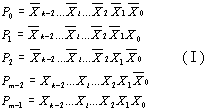

Дешифратор представляет собой комбинационную схему со многими выходами и описывается следующей системой переключательных функций:

Здесь

![]() -

входные сигналыDC,

-

входные сигналыDC,

![]() -

выходные сигналы.

-

выходные сигналы.

Каждая переключательная функция Pj представляет собой конституэнту единицы и поэтому равна единице на одном наборе, номер которого равен j.

По способам реализации системы переключательных функций различают линейные, прямоугольные (матричные) и пирамидальные дешифраторы.

Линейные дешифраторы

Линейные дешифраторы являются наиболее быстродействующими. Они представляют собой одну ступень логических элементов, которая непосредственно реализует систему (I) ПФ. Такой дешифратор содержит m независимых конъюнкторов с числом входом K у каждого. В качестве простейшего примера приведем схему дешифратора с парафазными входами при k=3, n=6, m=8.