- •Раздел I. Введение. Общие сведения о цифровых автоматах Лекция 1. Основные понятия и определения.

- •Раздел 2. Синтез цифровых автоматов без памяти

- •Преобразование функции в минимальную конъюнктивную нормальную форму (кнф).

- •Раздел 3. Общая теория конечных цифровых автоматов с памятью. Лекция 4. Основные понятия и определения.

- •Элементарный автомат

- •Диаграмму Вейча

- •Граф d-триггера

- •Матрица переходов rs-триггера:

- •Матрица переходов jk-триггера:

- •Перерисованная совмещенная таблица переходов и выходов

- •Диаграммы Вейча

- •Двухступенчатый триггер

- •Раздел 4.Синтез типовых узлов эвм

- •Кодированная таблица переходов и функций возбуждения

- •Минимальные дизъюнктивные нормальные формы функций возбуждения триггеров

- •Регистр сдвига

- •Временная диаграмма

- •Асинхронный вычитающий счетчик

- •Асинхронный реверсивный счетчик

- •Диаграммы Вейча

- •Счетчик на синхронных т-триггерах

- •Счетчик со сквозным переносом

- •Организация цепей сквозного переноса

- •Диаграммы Вейча

- •Синхронный пятеричный счетчик

- •Счетчик на кольцевых сдвигающих регистрах

- •Счетчик Джонсона

- •По матрице построим схему счетчика:

- •Дешифратор с парафазными входами

- •Линейный дешифратор

- •Принцип построения пирамидального дешифратора на 16 выходов

- •Полусумматор

- •Кроме сумматоров существуют полусумматоры, которые осуществляют сложение двух чисел с формированием сигналов суммы и переноса.

- •Диаграммы Вейча

- •Сумматор комбинационно-накапливающего типа

- •Последовательный сумматор

- •В свою очередь:

- •Раздел 5. Лекция 13. Абстрактный синтез конечных автоматов

- •Регулярным выражением:

- •Раздел 6. Лекция 15. Вероятностные автоматы

Раздел 4.Синтез типовых узлов эвм

Лекция 8. Регистры

К типовым узлам ЭВМ, предназначенным для хранения и преобразования двоичной информации, относятся различные виды регистров, счетчиков, сумматоров и дешифраторов.

Регистром называется устройство, предназначенное для приема, хранения и передачи информации. Информация в регистре хранится в виде двоичного числа, причем каждому разряду числа, записанного в регистр, соответствует свой разряд регистра.

Регистры используются также для выполнения некоторых операций над числами, такими как сдвиг числа влево или вправо, образование обратного кода числа, преобразование последовательного кода в параллельный и обратно, поразрядное логическое сложение и умножение чисел и т.д. В зависимости от способа ввода и вывода информации различают регистры параллельного, последовательного и параллельно-последовательного действия.

Регистры параллельного действия

В регистрах параллельного действия запись числа осуществляется параллельным кодом, т.е. во все разделы регистра одновременно.

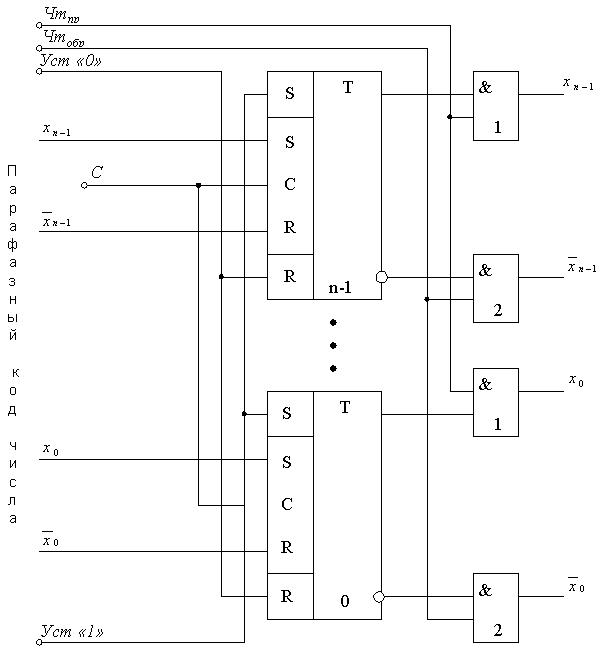

Регистр строится на триггерах, число которых равно числу разрядов в хранимом слове, т.е. каждый триггер предназначен для запоминания одного разряда числа. В качестве триггеров в таких регистрах используется, как правило, RS- и D- триггера. В зависимости от количества каналов, по которым поступает информация на входы регистра, различают регистры парафазного и однофазного вида. Парафазные регистры характеризуются тем, что информация на каждый разряд поступает по двум каналам (прямому и инверсному), а в однофазных регистрах информация поступает по одному каналу (прямому или инверсному). Приведем схему парафазного регистра на синхронных RS-триггерах с асинхронными и установочными входами R и S:

Пусть в n-разрядный регистр необходимо записать n-разрядное двоичное число X=xn-1xn-2…x1x0. Прямой и обратный коды каждого разряда числа поступают одновременно на S и R входы триггера. Запись числа осуществляется по синхронизирующему сигналу С. Если необходимо прочитать прямой код числа, хранящегося в регистре, необходимо в схему подать сигнал Чтпр (чтение прямое). Тогда на выходах конъюнкторов первой группы появится число в прямом коде, поскольку входы этих конъюнкторов соединены с прямыми выходами триггеров. Аналогично, при подаче сигнала Чтобр (чтение обратное), на выходах конъюнкторов второй группы появится число в обратном коде, а при одновременной подаче сигналов Чтпр и Чтобр будет прочитано число из регистра в парафазном параллельном коде.

Схема однофазного регистра на синхронных RS-триггерах с установочными R и S входами отличаются от приведенной лишь тем, что на вход R регистра инверсный код числа не подается. В этом случае этапу приема числа в регистр предшествует этап сброса регистра в нулевое состояние, который осуществляется по сигналу Уст «0», поступающему одновременно на асинхронные R входы всех триггеров. Далее по сигналу С те триггера, на вход S которых подается единичный сигнал, перейдут в единичное состояние, а остальные останутся в нулевом состоянии. Таким образом, однофазный регистр на RS-триггерах является двухтактным, тогда, как парафазный регистр – однотактным. Поэтому для увеличения быстродействия однофазные регистры строятся на D-триггерах, сбрасывать которые в нулевое состояние нет необходимости.

Регистр последовательного действия

В ЭВМ на ряду с параллельным используется также последовательный способ представления двоичной информации, при котором код числа передается по одному каналу последовательно разряд за разрядом в дискретные моменты времени, задаваемые синхроимпульсами. Для приема и выдачи чисел, представленных в последовательном коде, и используются регистры последовательного действия, основу которых составляют регистры сдвига. Регистр сдвига осуществляет операцию сдвига записанного в него двоичного числа влево или вправо на один или несколько разрядов при подаче специального управляющего сигнала «сдвиг». Рассмотрим синтез двухразрядного сдвигающего регистра на D-триггерах. Регистр должен работать следующим образом: в момент прихода синхронизирующего сигнала С число сдвигается в регистре вправо на один разряд. При этом разряды числа, сдвигаемые вправо, поступают на выход регистра, а в освобождающиеся слева разряды вводятся разряды числа, поступившего в последовательном коде на его вход. Имеем следующую кодированную таблицу переходов и функции возбуждения (таблица выходов не строится, ибо выходами регистра являются выходы самих триггеров).