- •23.05.05(190901.65) – «Системы обеспечения движения поездов»

- •Санкт-Петербург

- •Содержание

- •Введение

- •Арифметические и логические основы эвм

- •Системы счисления

- •1.2. Системы счисления, используемые в мпт

- •1.3. Преобразование чисел в различные системы счисления

- •- Метод подбора;

- •1.5. Кодирование чисел в машине

- •1.6. Сложение чисел в машинах с фиксированной запятой

- •1.7. Логические основы эвм

- •1.7.1. Основные понятия алгебры логики

- •1.7.2. Системы логических элементов эвм

- •Контрольные вопросы (тест)

- •Управляющий блок

- •Программа

- •Выработка cu последова-

- •Выполнение операции

- •2.2. Программная модель микропроцессора Программная модель имеет второе название регистровая структура.

- •2.3. Понятие о состоянии процессора (программы). Вектор слова состояния.

- •2.4. Система команд микропроцессора кр1821вм85а. Классификация команд по назначению.

- •2.5. Структура и формат команды.

- •Операционная часть Адресная часть ля фиксации этой информации в коде команды выделяются определенные разряды или поля. Общая структура команды имеет вид:

- •2.7. Информационный обмен при выполнении команд различных типов

- •Признак «Чт» mem r на шу

- •Передача адреса 0802н из рс на ша

- •Признак «Зп» mem w на шу

- •2.8. Команды передачи управления

- •2.9. Типы программ

- •Циклические программы содержат части, которые могут повторяться многократно при различных начальных условиях. Такие повторяющиеся части называются телом цикла.

- •Принципы организации системы прерываний

- •Контрольные вопросы (тест)

- •Библиографический список

- •3.1.Программируемый таймер

- •Рг режима

- •Каналы счета содержат 16-разрядные независимые счетчики; счет осуществляется вычитанием 1 из загруженного начального значения.

- •Режим 0 – программируемая задержка

- •3.2. Программируемый параллельный интерфейс

- •Буфер данных Канал а (7-0) ка(7-0)

- •Канал с

- •Режим 0 0 0

- •Ка ввод 1

- •Кс ввод 1

- •3.3. Программируемый последовательный интерфейс (универсальный синхронно-асинхронный приемо-передатчик усапп)

- •Буфер пе-

- •Буфер приемника

- •Запрещено 0 1

- •Запрещен х 0

- •3.4. Программируемый контроллер прерываний

- •Регистр маски прерывания

- •3.5.Контроллер прямого доступа к памяти

- •Основные понятия об интерфейсе

- •Библиографический список Вопросы к экзамену

- •Приложение 2 Варианты заданий по теме «Кодирование числе в машине» Вариант 1

- •Вариант 2

- •Вариант 3

- •Вариант 4

- •Вариант 5

- •Вариант 6

- •Вариант 7

- •Вариант 8

- •Вариант 9

- •Вариант 10

- •Вариант 11

- •Вариант 12

- •Вариант 13

- •Вариант 14

- •Вариант 15

- •Вариант 16

- •Вариант 17

- •Вариант 18

- •Вариант 19

- •Вариант 20

- •Вариант 21

- •Вариант 22

- •Вариант 23

- •Вариант 24

- •Вариант 25

- •Вариант 26

- •Вариант 27

- •Вариант 28

- •Приложение 3

- •Варианты заданий по теме

- •«Сложение чисел с фиксированной запятой»

- •Приложение 4

- •Варианты заданий на лабораторные работы по теме «Линейные программы»

- •Задание на учебную программу 1.

- •Приложение 5 Варианты заданий на лабораторные работы по теме «Разветвляющиеся программы» Задание на учебную программу 2.

- •Вариант 2

- •Вариант 4

- •Приложение 7 Варианты заданий на лабораторные работы по теме «Итоговые программы» Задание на учебную программу 4

- •Вариант 1

- •Вариант 13

- •Приложение 7 Система команд мп кр1821вм85а

- •Микропроцессоры. Особенности архитектуры.

- •Типовая архитектура микропроцессорной системы

- •Выработка cu последова-

- •Выполнение операции

- •Классификация команд по назначению.

- •Структура и формат команды.

- •Операционная часть Адресная часть ля фиксации этой информации в коде команды выделяются определенные разряды или поля. Общая структура команды имеет вид:

- •Библиографический список

- •Система команд простейшего мп

- •Прикладное программирование и основы микропроцессорной техники

Управляющий блок

(УБ)

управляющиесигналы

оповещательные

к

од

операции сигналы

од

операции сигналы

Рис.6. Декомпозиция автоматов

Функции ОБ:

прием и хранение операндов;

преобразование операндов;

выдача результатов и оповещательных сигналов о знаках, особых значениях операндов, особых значениях промежуточных и конечных результатов.

УБ вырабатывает последовательность управляющих сигналов, обеспечивающих выполнение в ОБ нужной последовательности микроопераций (микрокоманд).

Управляющий блок может быть организован двумя способами:

1.УБ аппаратного типа (с жесткой или схемной логикой). В этом случае организуется набор комбинационных схем, которые в нужный момент времени вырабатывают соответствующие управляющие сигналы.

2. УБ с микропрограммным управлением. В этом случае в памяти УБ (в ПЗУ) хранятся микрокоманды, каждая из которых содержит информацию о микрооперациях, подлежащих выполнению в течение одного машинного такта и адрес следующей микрокоманды.

Программные единицы связаны следующей иерархией:

Программа

Команда

Команда

(операция;

микропрограмма)

микропрограмма

(микрооперация)

На рис.7 приведена типовая архитектура микропроцессорной системы.

шина

адреса (AB)

шина

адреса (AB)

шина данных (DB)

RAM

RAM

ROM

ROM

CPU

ROM

RAM

In/Out

шина управления (CB)

_ __ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ __

КПр

ППИ

КПД

УСАПП

ПрТ

_ __ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ __

Внешние устройства

рис.7. Типовая архитектура микропроцессорной системы

Разрядность двунаправленной шины данных – от 8 разрядов.

Разрядность шины адреса – от 16 разрядов.

CPU – центральное процессорное устройство. Обеспечивает выполнение всех операций в соответствии с заданным алгоритмом. Практически обеспечивает выполнение всего процесса функционирования системы.

ROM (ПЗУ) – постоянное запоминающее устройство.

RAM (ОЗУ) – оперативное запоминающее устройство.

In/Out - интерфейсы ввода-вывода (порты ввода-вывода). Обеспечивают связь системы с внешними устройствами.

КПр - программируемый контроллер прерываний.

ППИ- программируемый параллельный интерфейс.

КПД- контроллер прямого доступа к памяти для управления внешними запоминающими устройствами.

УСАПП – программируемый последовательный интерфейс (универсальный синхронно-асинхронный приемо-передатчик).

ПрТ – программируемый таймер.

Однокристальные МП с малой разрядность шин данных и адреса ориентированы на применение в устройствах цифровой автоматики, в управляющих блоках периферийных устройств ЭВМ.

МП с большой разрядностью шин обладают следующими достоинствами:

большой объем адресуемой памяти;

развитая система команд;

разнообразные способы адресации:

встроенные векторные системы прерываний;

автоматическое обнаружение отказов питания.

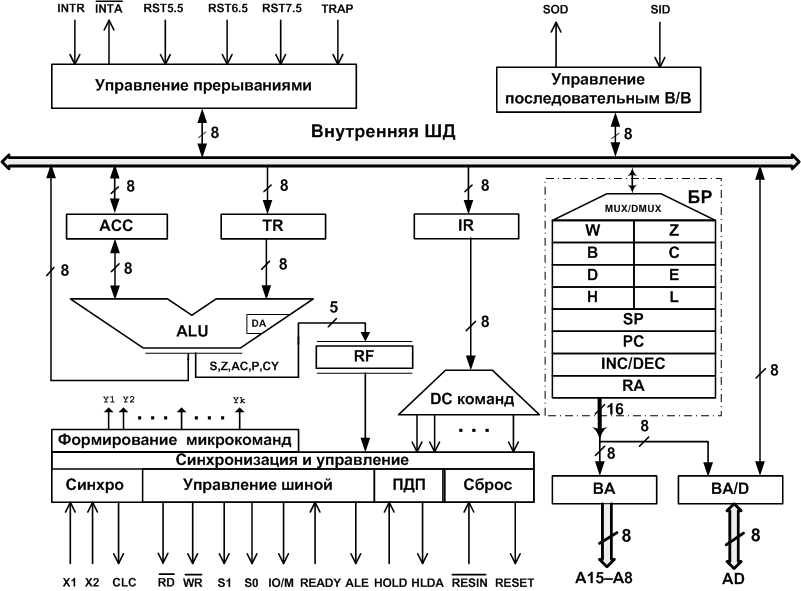

Ниже на рис. 8 представлена архитектура микропроцессора КР1821ВМ85А.

ШД – 8-разрядная шина данных.

Внутренняя шина данных связывает между собой все блоки МП. Ее разрядность равна разрядности информационного слова.

ША – 16-разрядная шина адреса.

ШУ – шина управления.

МЕМ – память.

PORT – устройства ввода-вывода (порты).

Шина – группа проводов передачи информации, объединенных одним общим функциональным признаком. МП имеет три шины. Совокупность шин образует магистраль.

РОН – регистры общего назначения. Служат для хранения операндов, промежуточных результатов, могут использоваться для хранения адресов памяти. РОН могут объединяться в пары для работы с 16-разрядными данными – BC, DE, HL. Все РОН программно доступны. Разрядность каждого РОН равна разрядности шины данных.

MX/DX- мультиплексор-демультиплексор. Обеспечивает передачу данных с внутренней шины данных в блок РОН.

W,Z – регистры временного хранения. Служат для временного хранения второго и третьего байта кода команды. Регистры программно недоступны.

SP – 16-разрядный указатель стека. В нем хранится адрес последней занятой ячейки стека (вершины стека). При записи данных содержимое регистра увеличивается на 1, а при чтении – уменьшается на 1. Стек реализуется в основной памяти с дисциплиной LIFО.

РС – 16- разрядный счетчик команд (программный счетчик). Используется для приема и хранения текущего адреса команды. При выборке каждого байта команды содержимое программного счетчика автоматически увеличивается на 1, при этом первый байт всегда передается в регистр команд RI.

I/D – схема инкремена-декремента. Позволяет автоматически увеличить или уменьшить на 1 содержимое регистра адреса и совместить во времени модификацию адреса и выполнение операции в АЛУ.

RGA – буферный регистр адреса. Служит для приема и хранения адресной части команды. Разрядность регистра равна разрядности шины адреса.

BD – буферный регистр данных. Используется для временного хранения выбранного из памяти слова перед его передачей на внутреннюю шину данных или для временного хранения результата перед его выдачей во внешнюю шину данных.

IR – регистр команд. Принимает и хранит код очередной команды, адрес которой хранится в программном счетчике.

DCкоманд – дешифратор кода команды.

ALU – 8-разрядное арифметико-логическое устройство. Предназначено для выполнения арифметических и логических операций.

АСС – регистр-аккумулятор или просто аккумулятор. Предназначен для временного хранения операнда или промежуточного результата. При выполнении операции с двумя операндами в А хранится один из операндов, а после выполнения операции – результат. Разрядность А равна разрядности информационного слова.

TR – регистр временного хранения. Предназначен для временного хранения одного из операндов перед выполнением операции в АЛУ.

CU – устройство управления. Вырабатывает последовательность управляющих сигналов, обеспечивающих выполнение микрооперации, расшифрованной по коду операции.

RF – регистр признаков или регистр флагов. В нем формируются признаки результата операции, выполненной в АЛУ. Регистр 8-разрядный, формирует 5 признаков (флагов).

7 6 5 4 3 2 1 0

S

Z

AC AAC

P

C

0 0 1

S - знак результата.

S = 1 – результат отрицательный; S = 0 – результат положительный.

Z – признак нулевого результата.

Z = 1 – результат равен нулю; Z =0 – результат ненулевой.

АС – признак полупереноса или вспомогательный перенос. Фиксирует при сложении перенос из младшей тетрады в старшую.

АС = 1, если перенос был; АС = 0, если переноса не было.

Р – признак четности или паритет. Определяет, четное или нечетное число единиц в результате.

Р = 1, если число единиц в результате четное; Р = 0, если число единиц в результате нечетное.

С – признак переноса. Фиксирует перенос из старшего разряда.

С = 1, если перенос был; С = 0, если переноса не было.

Ниже приводятся значения входов и выходов микропроцессора.

А8 – А15 – адресная шина. Старший байт адреса памяти или байт адреса ввода-вывода.

Д0 – Д7 – мультиплексная шина адреса/данных. Младший байт адреса памяти или адреса ввода-вывода появляются на этой шине в течение первого такта машинного цикла. В течение второго и третьего тактов она становится шиной данных.

ALE (выход) – разрешение фиксации адреса.

S0,S1,IO/M (выход) – состояние машинного цикла.

-

IO/M

S0

S1

состояние

0

0

1

1

0

1

*

*

*

0

1

0

1

1

1

0

Х

Х

1

0

1

0

1

1

0

Х

Х

Запись в память

Чтение из памяти

Запись при вводе-выводе

Чтение при вводе выводе

Выборка кода операции

Подтверждение прерывания

Останов

Захват

Сброс

* - третье состояние (высокий импеданс)

Х – значение безразлично.

Сигналы S0 , S1 , IO/M устанавливаются в начале машинного цикла и остаются неизменными в течение всего цикла.

R D (выход) – управление чтением. Низкий уровень сигнала указывает, что должно быть произведено чтение из выбранной ячейки или из устройства ввода-вывода.

W R (выход) – управление записью. Низкий уровень сигнала указывает, что информация с шины данных должна быть записана в выбранную ячейку или устройство ввода-вывода.

READY (вход). Если сигнал READI имеет высокий уровень в течение цикла чтения или записи, это указывает на то, что память или внешнее устройство готово пересылать или получать информацию.

HOLD (вход). Сигнал HOLD (Захват) указывает, что другие устройства запрашивают использование шины адреса или шины данных. Центральный процессор, получив запрос захвата, откажется от использования этой шины, как только завершится текущая операция передачи информации по этой шине.

HLDA (выход). Подтверждение захвата. Указывает, что центральный процессор получил запрос захвата и что он освободит шину в следующем цикле.

INTR (вход). Запрос прерывания. Используется как прерывание общего назначения. Этот сигнал воспринимается только в течение цикла, следующего за последним циклом выполнения текущей команды. С появлением сигнала INTR запрещается увеличение содержимого счетчика команд и формируетcя сигнал INTA. В течение этого цикла могут выдаваться команды RESTART (повторный запуск) или CALL для перехода к выполнению подпрограммы обработки прерывания. Прием сигнала INTR разрешается и запрещается программным путем. Он запрещается сигналом RESET (сброс) и немедленно после того, как прерывание принято.

I NTA (выход). Подтверждение прерывания. Выдается в течение цикла команды после того, как принят сигнал INTR.

RST5.5, RST6.5, RST7.5 (входы). Прерывания повторного запуска. Вызывают автоматическую выдачу внутренней команды RESTART.

TRAP (вход). Немаскируемое прерывание при возникновении непредусмотренной ситуации. Этот сигнал не может быть замаскирован либо заблокирован запретом прерывания никаким способом. Имеет самый высокий приоритет из всех прерываний.

R ESIN (вход). Устанавливает СК в нуль и сбрасывает триггеры разрешения прерывания и подтверждения захвата.

RESOUT (выход). Указывает на то, что произведен сброс центрального процессора. Может использоваться в качестве сигнала сброса системы.

Х1, Х2 – синхровходы. Служат для запуска внутреннего синхрогенератора.

CLK (выход). Выход синхроимпульса для системной синхронизации.

SID (вход). Линия последовательных входных данных. Данное с этой линии загружается в 7-й разряд аккумулятора при каждом выполнении команды RIM (читать маску прерывания).

SOD (выход). Линия последовательных выходных данных. Выходной сигнал SOD устанавливается или сбрасывается в соответствии с командой SIM (установить маску прерывания.

Vcc – питание +5в.

VSS – земля.

Функционирование МП происходит следующим образом.

1. Вся информация (программа, исходные данные, результаты) размещается в памяти (ОЗУ или ПЗУ).

2. Информация поступает в МП по шине данных.

3. Каждое внешнее или внутреннее устройство имеет адрес или диапазон адресов.

4. При обращении к конкретному устройству МП выставляет на ША адрес этого устройства, а на ШУ – признак обращения к этому устройству и обеспечивает выдачу информации на ШД.

Выполняя программу, МП обрабатывает команду за командой последовательно.

Алгоритм выполнения команды выглядит следующим образом.

начало

А

В