Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ШИФРАТОРЫ И ДЕШИФРАТОРЫ

Отчет по лабораторной работе №2 по дисциплине «Электроника и схемотехника 2»

Вариант №9

Студент гр. ____

______________

__.__.202_

Преподаватель каф. КИБЭВС

__.__.202_

Томск 2022

Введение

Цель работы: научиться создавать шифраторы и дешифраторы на разных базисах и решать задачу увеличения их размерности.

Постановка задачи:

1. Составить таблицы истинности для схем согласно варианту 9:

|

Тип |

Базис |

Нарастить до |

|

|

|

|

Шифратор |

6-3 |

ИЛИ-НЕ |

- |

|

|

|

|

Дешифратор |

4-10 |

И-НЕ |

- |

|

|

|

|

Приоритетный |

8-3 |

И, ИЛИ, НЕ |

16-4 |

|

|||

шифратор |

|

|

|

|

|

|

|

Написать формулы для всех выходов в СДНФ или СКНФ.

2.Собрать схемы на холстах .bdf согласно полученным формулам.

3.Создать схему устройства согласно варианту большей размерности на основе созданного ранее символа.

4.Промоделировать работу всех схем в двух режимах. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

5.Сверить результаты моделирования с составленными таблицами истинности.

6.Повторить пп. 2-5 для заданного вариантом HDL (SystemVerilog). При масштабировании использовать модульное подключение.

7.Написать выводы о проделанной работе.

2

1. ШИФРАТОР X-Y

Согласно 9 варианту, у шифратора должно быть 6 входов на базисе ИЛИ-

НЕ. Количество выходов – 3. Ниже приведены таблица истинности (1.1) и

формулы для всех входов и выходов устройства. А также на рисунках 1.1-1.3

изображены схема и моделирование шифратора 6-3. На рисунках 1.4-1.6 код,

моделирование и RTL-схема.

Таблица 1.1 – Таблица истинности шифратора 6-3.

|

|

|

Входы |

|

|

|

|

Выходы |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

|

|

|

Y |

|

|

|

E |

|

|

|

|

|

|

|

|

|

|

G |

5 |

4 |

3 |

|

2 |

1 |

0 |

2 |

1 |

0 |

||

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

х |

х |

х |

|

х |

х |

х |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

Формулы для входов:

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

||||||

|

̅ |

|

|

|

|

|

̅̅̅ |

= |

|||||||

0 |

|

5 |

4 |

3 |

2 |

1 |

0 |

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

||||||

|

̅ |

|

|

|

|

̅̅̅ |

|

= |

|||||||

1 |

|

5 |

4 |

3 |

2 |

1 |

0 |

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

||||||

|

̅ |

|

|

|

̅̅̅ |

|

|

= |

|||||||

2 |

|

5 |

4 |

3 |

2 |

1 |

0 |

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

||||||

|

̅ |

|

|

̅̅̅ |

|

|

|

= |

|||||||

3 |

|

5 |

4 |

3 |

2 |

1 |

0 |

3

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

||||||

|

̅ |

|

̅̅̅ |

|

|

|

|

= |

|||||||

4 |

|

5 |

4 |

3 |

2 |

1 |

0 |

|

̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ |

||||||

|

̅ |

|

|

|

|

|

|

= ̅̅̅ |

|||||||

5 |

|

5 |

4 |

3 |

2 |

1 |

0 |

4

Формулы для выходов:

2 = ̿̿̿̿̿̿̿̿̿̿

5 4

1 = ̿̿̿̿̿̿̿̿̿̿

3 2

0 = ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿

5 3 1

= 5 4 3 2 1 0

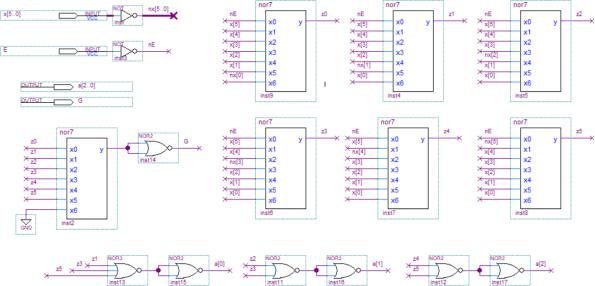

Рисунок 1.1 – Функциональная схема шифратора 6-3.

5

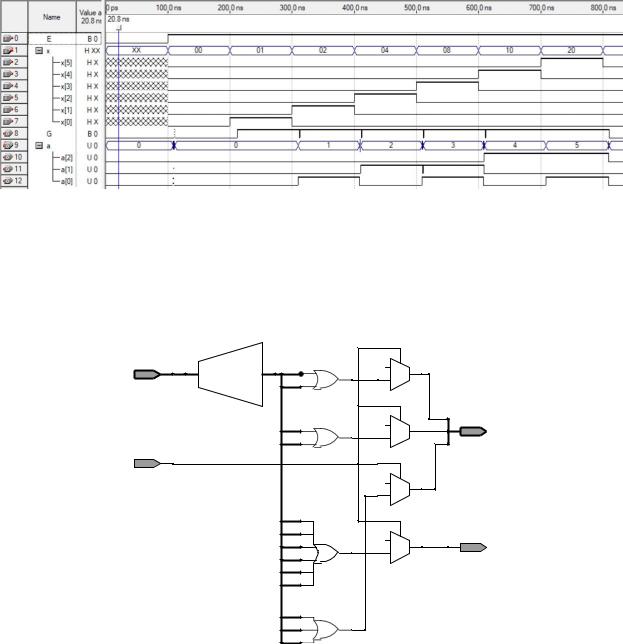

Рисунок 1.2 – Моделирование схемы шифратора 6-3.

6

Рисунок 1.3 – Функциональный режим моделирования шифратора 6-3.

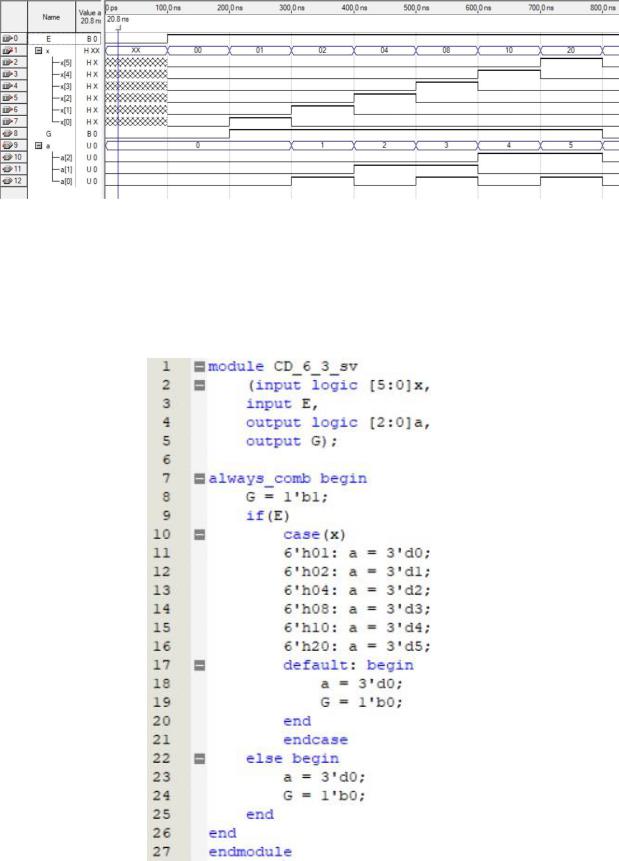

Рисунок 1.4 – Код шифратора 6-3 на SystemVerilog. 7

Рисунок 1.5 – Моделирование кода шифратора 6-3.

Decoder0

|

|

a~0 |

0 |

0 |

|

|

|

|

|

||

x[5..0] |

IN[5..0] |

OUT[63..0] |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

a~2 |

|

|

DECODER |

|

|

|

|

|

|

a~1 |

0 |

0 |

|

|

|

|

|

||

|

|

|

|

1 |

|

|

|

|

|

a~3 |

|

|

|

|

0 |

0 |

|

|

|

|

|

1 |

|

|

|

|

|

a~4 |

a[2..0] |

E |

|

WideOr1 |

0 |

0 |

|

|

|

|

|||

|

|

|

1 |

|

|

|

|

|

|

G |

|

|

|

WideOr0 |

|

|

|

Рисунок 1.6 – RTL-схема кода шифратора 6-3. |

|||||

8

2. ПРИОРИТЕТНЫЙ ШИФРАТОР (HPRI)

По условию варианта, нужно собрать схему приоритетного шифратора с

8 входами (3 выхода) на базисе И, ИЛИ, НЕ и нарастить его до 16 входов (4

выхода). Ниже приведены таблица истинности (2.1) и формулы для всех входов и выходов устройства 8-3. А также таблица (2.2) и формулы для масштабируемого устройства 16-4.

Таблица 2.1 – Таблица истинности приоритетного шифратора 8-3.

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

|

|

|

|

Y |

|

|

0 |

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

|

7 |

6 |

5 |

|

4 |

|

3 |

2 |

1 |

0 |

2 |

1 |

0 |

|||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

x |

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

x |

x |

0 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

1 |

x |

x |

x |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

|

x |

x |

x |

x |

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

x |

|

x |

x |

x |

x |

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

x |

|

x |

|

x |

x |

x |

x |

1 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

|

x |

|

x |

x |

x |

x |

1 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

|

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Формулы для выходов:

2 = ( 7 7 ∩ 6 7 ∩ 6 ∩ 5 7 ∩ 6 ∩ 5 ∩ 4) ∩ E

1 = ( 7 7 ∩ 6 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 ∩ 2) ∩ E

0 = ( 7 7 ∩ 6 ∩ 5 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 ∩ 2 ∩ 1) ∩

9

= ( 7 6 5 4 3 2 1 0) ∩

0 = 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 ∩ 2 ∩ 1 ∩ 0 ∩

10