Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Отчет по лабораторной работе №1 по дисциплине «Электроника и схемотехника 2»

Вариант №9

Студент гр. ____

______________

__.__.202_

Преподаватель

каф. КИБЭВС

__.__.202_

Томск 2022

Введение

Цель работы – изучить основные инструменты САПР QuartusII и научиться моделировать в ней работу схем на основе простых логических элементов.

Постановка задачи.

1.Собрать на холсте .bdf и промоделировать работу схем 2И, 2ИЛИ, 2искл.ИЛИ, 2И-НЕ и 2ИЛИ-НЕ в двух режимах.

2.Описать логические элементы из п.1 на HDL и промоделировать эти схемы.

3.Собрать схему на отдельном холсте .bdf для выражения из таблицы согласно варианту.

4.Промоделировать её работу в двух режимах. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

5.Выполните пп. 3-4 с помощью HDL согласно варианту 9.

6.Составить таблицу истинности для выражения из таблицы согласно варианту. Сверить результаты моделирования с составленной таблицей истинности.

7.Написать выводы о проделанной работе.

1. УСТРОЙСТВО 2И

Первый логический элемент – 2И, ниже в таблице 1.1 представлена его таблица истинности. Если на входе будет ходя бы один логический 0, то на выходе будет 0.

Таблица 1.1 – Таблица истинности для ЛЭ 2И

A |

B |

C |

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

|

|

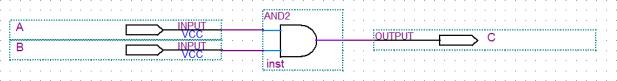

Формула схемы 2И выглядит следующим образом: С = A B. Функциональная схема продемонстрирована на рисунке 1.1, на ней можно увидеть два входа А и B, выход С, и непосредственно сам логический элемент И.

Рисунок 1.1 – Функциональная схема 2И

2

Также был составлен код на языке описания аппаратуры HDL (рисунок 1.2). В блоке “entity”, описаны порты внешнего взаимодействия (на 5 строчке описаны два наших входа A и B, а на 6 выход С). Затем идет структура блока, описание которой происходит внутри оператора “architecture”.

Рисунок 1.2 – HDL код 2И

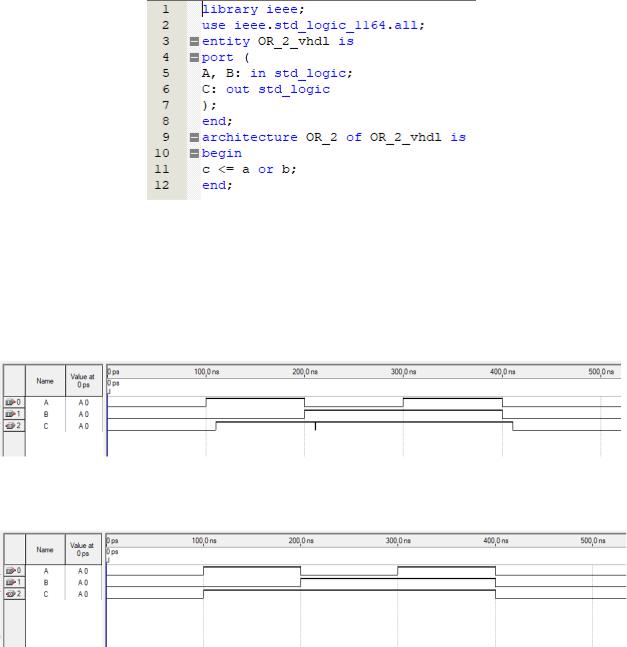

Далее было проведено моделирование построенной схемы 2И в двух режимах: “Timing” и “Functional”. Результаты моделирований продемонстрированы на рисунках 1.3 и 1.4 соответственно.

Рисунок 1.3 – 2И в режиме “Timing”

Рисунок 1.4 - 2И в режиме “Functional”

На рисунках выше можно заметить, что при работе в режиме “Timing” есть небольшие выходы за границы интервала. Это происходит из-за того, что он учитывает задержку на логических элементах. Для исключения задержек нужно просто поменять режим моделирования на “Functional”.

3

Если посмотреть на моделирование схемы 2И в режиме “Functional”, можно заметить, что значения выхода С полностью совпадают с таблицей истинности, представленной ранее.

2 УСТРОЙСТВО 2ИЛИ

Второй логический элемент – 2ИЛИ, ниже в таблице 2.1 представлена его таблица истинности. Если на входе будет ходя бы одна логическая 1, то на выходе будет 1.

Таблица 2.1 – Таблица истинности для ЛЭ 2ИЛИ

A |

B |

C |

|

|

|

0 |

0 |

0 |

|

|

|

1 |

0 |

1 |

|

|

|

0 |

1 |

1 |

1 |

1 |

1 |

Формула схемы 2ИЛИ выглядит следующим образом: С = A B. Функциональная схема продемонстрирована на рисунке 2.1, на ней можно увидеть два входа А и B, выход С, и непосредственно сам логический элемент ИЛИ.

Рисунок 2.1 – Функциональная схема 2ИЛИ

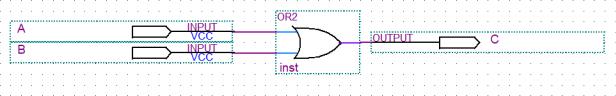

Также был составлен код на языке описания аппаратуры HDL (рисунок 2.2). В блоке “entity”, описаны порты внешнего взаимодействия (на 5 строчке описаны два наших входа A и B, а на 6 выход С). Затем идет структура блока, описание которой происходит внутри оператора “architecture”.

4

Рисунок 2.2 – HDL код 2ИЛИ

Далее было проведено моделирование построенной схемы 2ИЛИ в двух режимах: “Timing” и “Functional”. Результаты моделирований продемонстрированы на рисунках 2.3 и 2.4 соответственно.

Рисунок 2.3 – 2ИЛИ в режиме “Timing”

Рисунок 2.4 - 2ИЛИ в режиме “Functional”

Если посмотреть на моделирование схемы 2ИЛИ в режиме “Functional”, можно заметить, что значения выхода С полностью совпадают с таблицей истинности, представленной ранее.

5

3 УСТРОЙСТВО 2ИСКЛ.ИЛИ

Третий логический элемент – 2искл.ИЛИ, ниже в таблице 3.1 представлена его таблица истинности. Если на входе не будет логической 1 или их чётное количество, то на выходе будет 0.

Таблица 3.1 – Таблица истинности для ЛЭ 2искл.ИЛИ

x1 |

x2 |

y1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

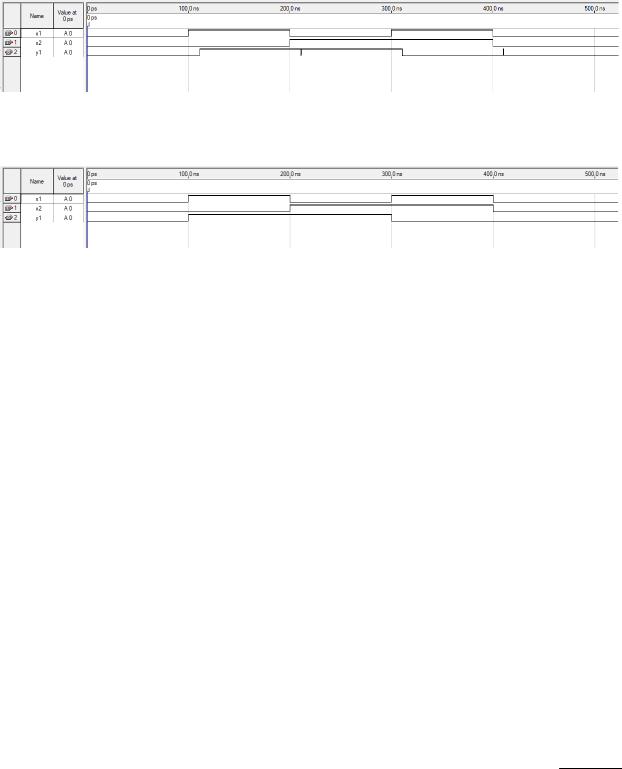

Формула схемы 2искл.ИЛИ выглядит следующим образом: С = A B. Функциональная схема продемонстрирована на рисунке 3.1, на ней можно увидеть два входа x1 и x2, выход y1, и непосредственно сам логический элемент искл.ИЛИ.

Рисунок 3.1 – Функциональная схема 2искл.ИЛИ

Также был составлен код на языке описания аппаратуры HDL (рисунок 3.2). В блоке “entity”, описаны порты внешнего взаимодействия (на 5 строчке описаны два наших входа x1 и x2, а на 6 выход y1). Затем идет структура блока, описание которой происходит внутри оператора “architecture”.

Рисунок 3.2 – HDL код 2искл.ИЛИ

6

Далее было проведено моделирование построенной схемы 2искл.ИЛИ в двух режимах: “Timing” и “Functional”. Результаты моделирований продемонстрированы на рисунках 3.3 и 3.4 соответственно.

Рисунок 3.3 – 2искл.ИЛИ в режиме “Timing”

Рисунок 3.4 – 2искл.ИЛИ в режиме “Functional”

Если посмотреть на моделирование схемы 2искл.ИЛИ в режиме “Functional”, можно заметить, что значения выхода y1 полностью совпадают с таблицей истинности, представленной ранее.

4 УСТРОЙСТВО 2И-НЕ

Четвёртый логический элемент – 2И-НЕ, ниже в таблице 4.1 представлена его таблица истинности. Является противоположностью ЛЭ И, если на входе есть хотя бы один логический 0, то на выходе будет 1. Если на входе все 1, то на выходе 0.

Таблица 4.1 – Таблица истинности для ЛЭ 2И-НЕ

A |

B |

C |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

|

|

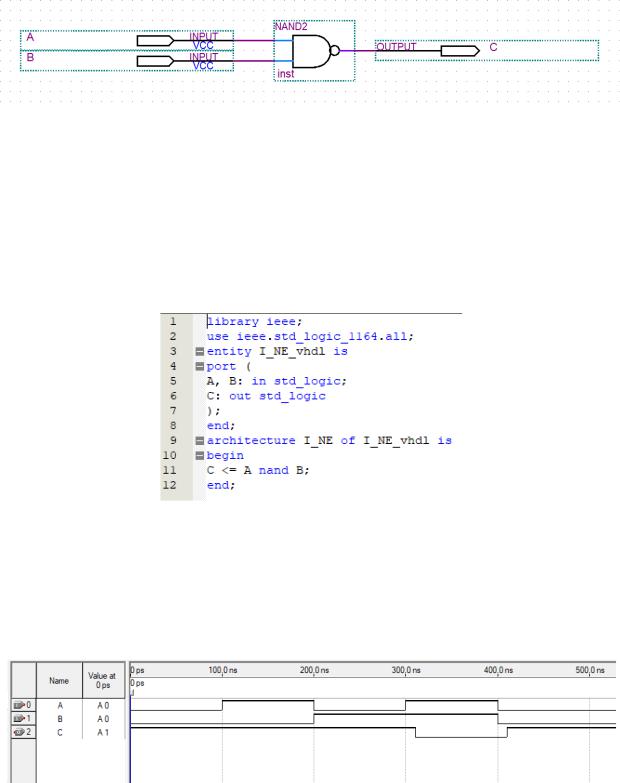

Формула схемы 2И-НЕ выглядит следующим образом: С = A B. Функциональная схема продемонстрирована на рисунке 4.1, на ней можно

7

увидеть два входа A и B, выход C, и непосредственно сам логический элемент И-НЕ.

Рисунок 4.1 – Функциональная схема 2И-НЕ

Также был составлен код на языке описания аппаратуры HDL (рисунок 4.2). В блоке “entity”, описаны порты внешнего взаимодействия (на 5 строчке описаны два наших входа А и В, а на 6 выход С). Затем идет структура блока, описание которой происходит внутри оператора “architecture”.

Рисунок 4.2 – HDL код 2И-НЕ

Далее было проведено моделирование построенной схемы 2И-НЕ в двух режимах: “Timing” и “Functional”. Результаты моделирований продемонстрированы на рисунках 4.3 и 4.4 соответственно.

Рисунок 4.3 – 2И-НЕ в режиме “Timing”

8

Рисунок 4.4 – 2И-НЕ в режиме “Functional”

Если посмотреть на моделирование схемы 2И-НЕ в режиме “Functional”, можно заметить, что значения выхода С полностью совпадают с таблицей истинности, представленной ранее.

5 УСТРОЙСТВО 2ИЛИ-НЕ

Пятый логический элемент – 2ИЛИ-НЕ, ниже в таблице 5.1 представлена его таблица истинности. Является противоположностью ЛЭ ИЛИ, если на входе есть хотя бы одна логическая 1, то на выходе будет 0. Если на входе все 0, то на выходе 1.

Таблица 5.1 – Таблица истинности для ЛЭ 2ИЛИ-НЕ

A |

B |

C |

|

|

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

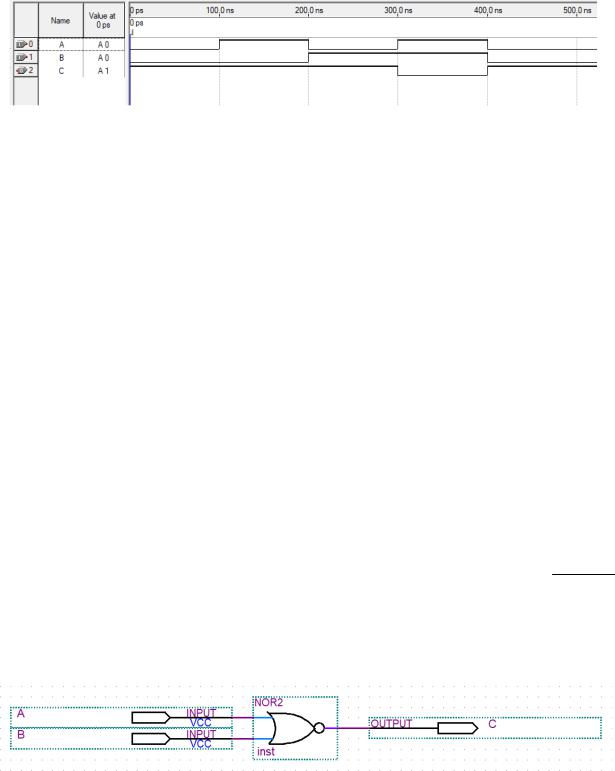

Формула схемы 2ИЛИ-НЕ выглядит следующим образом: С = A B. Функциональная схема продемонстрирована на рисунке 5.1, на ней можно увидеть два входа A и B, выход C, и непосредственно сам логический элемент ИЛИ-НЕ.

Рисунок 5.1 – Функциональная схема 2ИЛИ-НЕ

Также был составлен код на языке описания аппаратуры HDL (рисунок 5.2). В блоке “entity”, описаны порты внешнего взаимодействия (на 5 строчке описаны два наших входа А и В, а на 6 выход С). Затем идет структура блока, описание которой происходит внутри оператора “architecture”.

9

Рисунок 5.2 – HDL код 2ИЛИ-НЕ

Далее было проведено моделирование построенной схемы 2ИЛИ-НЕ в двух режимах: “Timing” и “Functional”. Результаты моделирований продемонстрированы на рисунках 5.3 и 5.4 соответственно.

Рисунок 5.3 – 2ИЛИ-НЕ в режиме “Timing”

Рисунок 5.4 – 2ИЛИ-НЕ в режиме “Functional”

Если посмотреть на моделирование схемы 2ИЛИ-НЕ в режиме “Functional”, можно заметить, что значения выхода С полностью совпадают с таблицей истинности, представленной ранее.

10