Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ РЕГИСТРОВ

Отчет по лабораторной работе №6 по дисциплине «Электроника и схемотехника 2»

Вариант №9

Студент гр. ____

______________

__.__.2022

Преподаватель

каф. КИБЭВС

______________

__.__.2022

Томск 2022

Введение

Цель работы – изучить регистры, их принципы построения и работы.

Постановка задачи:

1.Составить таблицы истинности для схем согласно варианту.

2.Собрать заданные схемы регистров.

3.Описать устройства с помощью HDL.

3. Промоделировать работу схем и проверить с таблицами

истинностями.

Задания по варианту:

-описать регистр SISO DSR с асинхронной загрузкой и синхронным сбросом, разрядность регистра – 12;

-описать регистр с параллельной записью и последовательной выдачей

DSL, сброс – синхронный, разрядность регистра – 16;

- описать регистр PIPO с асинхронной загрузкой и синхронным

сбросом, разрядность-8.

2

1 РЕГИСТР ТИПА SISO

1.1 ТАБЛИЦА ИСТИННОСТИ

Ниже приведена таблица истинности 1.1 для регистра типа SISO DSR.

Таблица 1.1 – Таблица истинности регистра типа SISO DSR

№ |

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

Вых. |

||

|

sin |

R |

L |

D11 |

D10 |

D |

D |

D |

D |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

|

|

|

|

|

|

9 |

8 |

7 |

6 |

|

|

|

|

|

|

|

1 |

a1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

2 |

a2 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

3 |

a3 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

4 |

a4 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

5 |

a5 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

6 |

a6 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

7 |

a7 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

8 |

a8 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

9 |

a9 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

10 |

a10 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

11 |

a11 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

12 |

a12 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

a1 |

13 |

a13 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

a2 |

14 |

a14 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

a3 |

15 |

a15 |

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

a4 |

16 |

a16 |

x |

1 |

b11 |

b10 |

b |

b |

b |

b6 |

b5 |

b4 |

b3 |

b2 |

b1 |

b0 |

b0 |

|

|

|

|

|

|

9 |

8 |

7 |

|

|

|

|

|

|

|

|

17 |

a17 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b1 |

18 |

a18 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b2 |

19 |

a19 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b3 |

20 |

a20 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b4 |

21 |

a21 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b5 |

22 |

a22 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b6 |

23 |

a23 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b7 |

24 |

a24 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b8 |

25 |

a25 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b9 |

26 |

a26 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b10 |

27 |

a27 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

b11 |

3

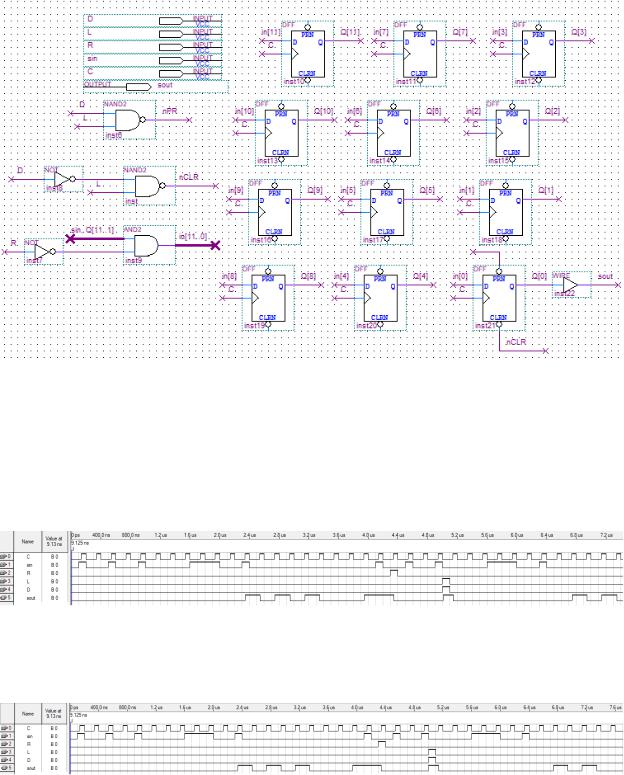

1.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 1.1 представлена функциональная схема регистра типа

SISO DSR.

Рисунок 1.1 – Функциональная схема асинхронного вычитающего счетчика

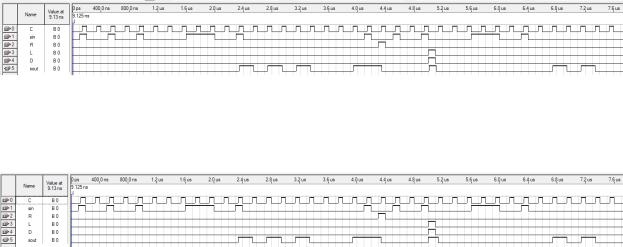

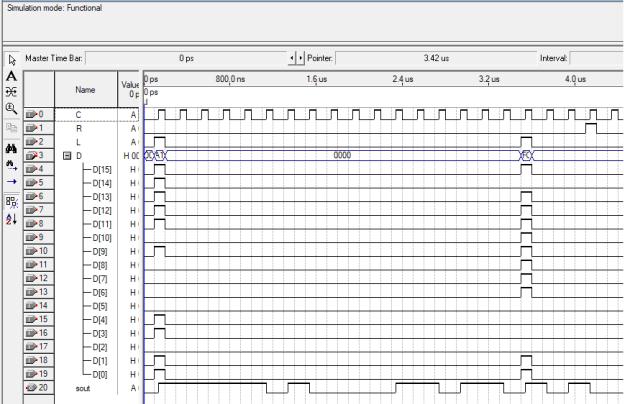

1.3 МОДЕЛИРОВАНИЕ

Было выполнено моделирование составленной функциональной схемы из пункта 1.3. На рисунке 1.2 изображен результат моделирования в режиме

Timing.

Рисунок 1.2 – Моделирование регистра SISO в режиме Timing

На рисунке 1.3 представлен результат моделирования в режиме

Functional.

Рисунок 1.3 – Моделирование регистра SISO в режиме Functional

4

По результатам моделирования можно сделать вывод, что схема

выполнена в соответствии с таблицей истинности асинхронного регистра

SISO DSR 1.1.

1.4 ОПИСАНИЕ С ПОМОЩЬЮ HDL

Ниже представлен код на SystemVerilog:

module siso_sv (

input logic C, L, R, sin, input logic D,

output logic sout) ;

logic [11:0] Q; assign sout = Q[0];

always_ff @(posedge C, posedge L) if (L) Q[0] <= D;

else if (R) Q <= 12'b0; else Q <= {sin, Q[11:1]};

endmodule

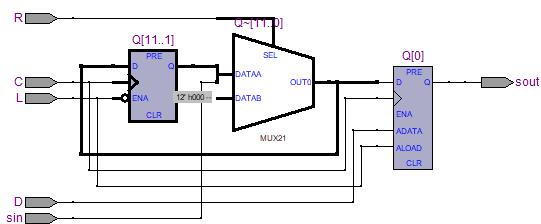

На рисунке 1.4 представлено моделирование регистра SISO в режиме

Timing.

Рисунок 1.4 – Моделирование регистра SISO в режиме Timing

На рисунке 1.5 представлено моделирование регистра SISO в режиме

Functional.

Рисунок 1.5 – Моделирование регистра SISO в режиме Functional

На рисунке 1.6 представлено изображение схемы с помощью RTL

Viewer.

5

Рисунок 1.6 – RTL Viewer представление

2 УНИВЕРСАЛЬНЫЙ РЕГИСТР

2.1 ТАБЛИЦА ИСТИННОСТИ

Ниже приведена таблица истинности 2.1 для универсального регистра с параллельной записью и последовательной выдачей DSL.

Таблица 2.1 – Таблица истинности универсального регистра

№ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Вы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

х. |

|

R |

L |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

sou |

|

|

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

t |

1 |

0 |

1 |

a1 |

a1 |

a1 |

a1 |

a1 |

a1 |

a |

a |

a |

a |

a |

a |

a |

a |

a |

a0 |

a1 |

|

|

|

5 |

4 |

3 |

2 |

1 |

0 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

5 |

2 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c0 |

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

3 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

4 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c2 |

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

5 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c3 |

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

6 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c4 |

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

7 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c5 |

a9 |

8 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c6 |

a8 |

9 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c7 |

a7 |

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c8 |

a6 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c9 |

a5 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

a4 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

Продолжение таблицы 2.1

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

a3 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

a2 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

a1 |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

a0 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

c0 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

1 |

0 |

1 |

b1 |

b1 |

b1 |

b1 |

b1 |

b1 |

b |

b |

b |

b |

b |

b |

b |

b |

b |

b0 |

b1 |

8 |

|

|

5 |

4 |

3 |

2 |

1 |

0 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

5 |

1 |

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

c1 |

b1 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.2 ФУНКЦИОНАЛЬНАЯ СХЕМА |

|

|

|

|

|

|||||||||

Для данного задания необходимо реализовать синхронный сброс.

На рисунках 2.1, представлена функциональная схема заданного универсального регистра.

Рисунок 2.1 – Функциональная схема универсального регистра

7

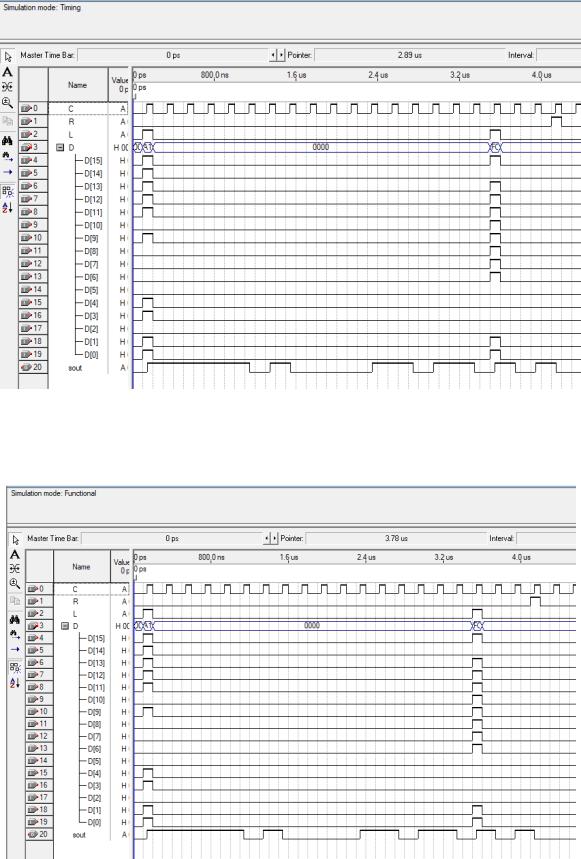

2.3 МОДЕЛИРОВАНИЕ

Было выполнено моделирование составленной функциональной схемы из пункта 2.2. На рисунке 2.2 изображен результат моделирования в режиме

Timing.

Рисунок 2.2 – Моделирование универсального регистра в режиме Timing

На рисунке 2.3 представлен результат моделирования в режиме

Functional.

8

Рисунок 2.3 – Моделирование универсального регистра в режиме Functional

По результатам моделирования можно сделать вывод, что схема

выполнена в соответствии с таблицей истинности универсального регистра

2.1.

2.4 ОПИСАНИЕ С ПОМОЩЬЮ HDL

Ниже представлен код на SystemVerilog:

module piso_sv (

input logic C, L, R, input logic [15:0] D, output logic sout) ;

logic [15:0] Q; assign sout = Q[15];

always_ff @(posedge C) if (R) Q <= 16'b0; else if (L) Q <= D;

else Q <= {Q[15:0], D[0]}; endmodule

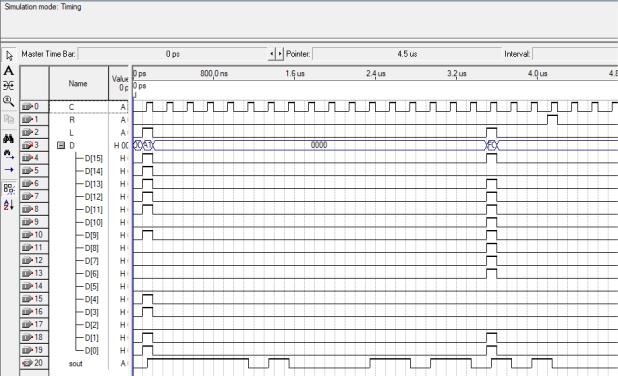

На рисунке 2.4 представлено моделирование универсального регистра

в режиме Timing.

9

Рисунок 2.4 – Моделирование универсального регистра в режиме Timing

На рисунке 2.5 представлено моделирование универсального регистра в режиме Functional.

Рисунок 2.5 – Моделирование универсального регистра в режиме Functional

На рисунке 2.6 представлено изображение схемы с помощью RTL

Viewer.

10