Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНОГО БЛОКА

Отчет по лабораторной работе №8

по дисциплине «Электроника и схемотехника 2»

Вариант №9

Студент гр. ____

______________

__.__.2022

Преподаватель

каф. КИБЭВС

______________

__.__.2022

Томск 2022

Введение

Цель данной работы: научиться совместно применять устройства средней степени интеграции.

Постановка задачи:

В данной работе необходимо спроектировать и реализовать вычислительный блок, в котором приём входных данных осуществляется параллельным кодом с их синхронизацией по отдельной линии по заднему фронту сигнала. Вычислительный блок должен после получения входных данных выполнить операцию согласно коду операции: 00 – операция не производится, на выход передаётся значение счётчика выполненных операций;

01 – кодирование двоичного числа в 4b5b-кода; 10 – над 3-х разрядными А и В выполняется логическая побитовая операция 3-х разрядный результат подаётся на выход; 11 – над 3-х разрядными А и В выполняется арифметическая операция сложения, 3-х разрядный результат подаётся на выход. После выполнения каждой операции 5-ти разрядный счётчик операции. Устройство должно иметь вход синхронного сброса, который должен сбрасывать все буферы. После получения логической единицы по линии «read» произвести выдачу полученных результатов последовательным кодом старшими разрядами вперёд. Синхронизация передаваемых разрядов должна осуществляться передним фронтом внутреннего синхросигнала, который также должен передаваться вместе с выходными данными.

Для данного устройства проделать следующие пункты:

1.Разработать обобщённую функциональную схему устройства.

2.Описать составные части схемы.

3.Составить таблицы функционирования операционного блока.

4.Организовать приём и выдачу данных согласно варианту №9, из таблицы для выполнения 4-х операций, используя встроенные блоки регистров

исчётчиков.

2

5.Создать схему реализации вычислительного блока, выполняющего заданные операции и осуществляющего приём входных данных и выдачу результата согласно варианта в таблице.

6.Составить план моделирования в виде двух столбцов таблицы: входные данные (код операции, данные), выходные данные (ожидаемый результат).

Используйте для каждой операции по два различных набора данных. Поставьте в плане моделирования вызов значения счётчика операций в конце моделирования до сброса и после него.

7.Промоделировать работу схемы в двух режимах. Проведите анализ результатов моделирования разных режимов.

8.Сверить результаты моделирования с составленными таблицами истинности.

9.Повторить п. 4-8, только для описания устройств вместо схем на холстах .bdf используя язык описания аппаратуры System Verilog.

10.Написать выводы о проделанной работе.

3

1.ВЫЧИСЛИТЕЛЬНЫЙ БЛОК

1.1ОБОБЩЕННАЯ ФУНКЦИОНАЛЬНАЯ СХЕМА

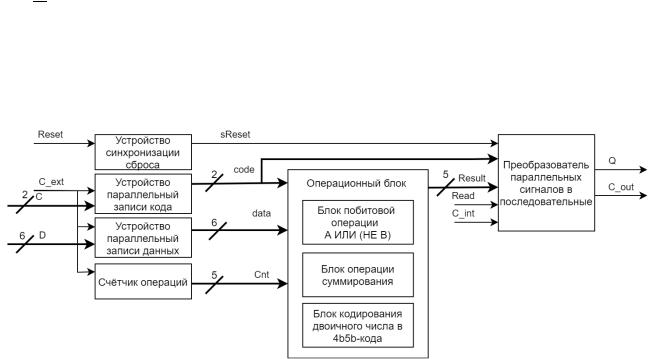

Далее, на рисунке 1.1.1 представлена обобщенная функциональная схема устройства. Устройство состоит из трех основных частей: входной части,

операционного блока и выходной части. Входной часть состоит из 4 других устройств: устройства параллельной записи кода, устройства параллельной записи данных, счетчика операций, а также устройства синхронизации сброса.

Операционный блок состоит из трех других блоков: блока побитовой операции

, блока операции суммирования и блока кодирования двоичного числа в код вида 4b5b. Выходная часть состоит из устройства преобразующего параллельные сигналы в последовательные, где также учитываются сигнал

«Read» и внутренний синхроимпульс.

Рисунок 1.1.1 – Обобщенная функциональная схема

4

1.2ТАБЛИЦЫ ФУНКЦИОНИРОВАНИЯ

Втаблице 1.1 представлены данные до процесса кодирования, данные по заданию. В таблице 1.2 представлены данные, которые должны быть после процесса кодирования.

Таблица 1.1 – Таблица функционирования

Задача №4

|

Входы |

|

|

|

Выходы |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

x3 |

x2 |

x1 |

x0 |

y4 |

y3 |

|

y2 |

|

y1 |

y0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 |

1 |

|

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

1 |

0 |

|

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

1 |

|

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

1 |

1 |

|

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

5

Таблица 1.2 – Таблица функционирования

Задача №4

|

|

Входы |

|

|

|

|

Выходы |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Q4 |

Q3 |

Q2 |

|

Q1 |

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

Далее, в таблице 1.3, представлены значения всех входов и выходов для

вычислительного блока, при выполнении логической побитовой операции.

6

Таблица 1.3 – Таблица функционирования

А B

|

|

Входы |

|

|

|

|

|

|

|

Выходы |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Q4 |

|

Q3 |

|

Q2 |

|

Q1 |

Q0 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

X |

0 |

0 |

0 |

1 |

|

1 |

|

|

1 |

|

|

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

a0 |

0 |

0 |

1 |

1 |

|

1 |

|

|

|

|

a0 |

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

a1 |

X |

0 |

1 |

0 |

1 |

|

|

|

a1 |

1 |

|

|

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

a3 |

a2 |

0 |

1 |

1 |

1 |

|

|

|

a3 |

|

|

a2 |

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a4 |

X |

X |

1 |

0 |

0 |

|

a4 |

1 |

|

|

1 |

|

|

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a6 |

X |

a5 |

1 |

0 |

1 |

|

a6 |

1 |

|

|

|

|

a5 |

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a8 |

a7 |

X |

1 |

1 |

0 |

|

a8 |

|

|

a7 |

1 |

|

|

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a11 |

a10 |

a9 |

1 |

1 |

1 |

a11 |

|

a10 |

|

|

a9 |

|

- |

- |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

b2 |

b1 |

b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

- |

|

b2 |

|

|

b1 |

|

|

b0 |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 |

0 |

1 |

b4 |

b3 |

X |

|

|

|

|

|

|

|

|

1 |

|

|

|

- |

- |

||

|

b4 |

|

|

b3 |

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 |

1 |

0 |

b6 |

X |

b5 |

|

|

|

1 |

|

|

|

|

|

|

|

|

- |

- |

||

|

b6 |

|

|

|

|

b5 |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 |

1 |

1 |

b7 |

X |

X |

|

|

|

1 |

|

|

1 |

|

|

|

- |

- |

||||

|

b7 |

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

1 |

0 |

0 |

X |

b9 |

b8 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

- |

- |

|

|

|

|

b9 |

|

|

b8 |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

1 |

0 |

1 |

X |

b10 |

X |

1 |

|

|

|

|

|

|

1 |

|

|

|

- |

- |

|||

|

|

b10 |

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

1 |

1 |

0 |

X |

X |

b11 |

1 |

|

1 |

|

|

|

|

|

|

|

|

- |

- |

|||

|

|

|

|

b11 |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

1 |

1 |

1 |

X |

X |

X |

1 |

|

1 |

|

|

1 |

|

|

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В таблице 1.4 представлен полный перебор сигналов и соответствующего выхода для вычислительного блока, при выполнении арифметической операции сложения.

7

Таблица 1.4 – Таблица функционирования

A + B

|

|

Входы |

|

|

|

|

Выходы |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

D5 |

D4 |

D3 |

|

D2 |

D1 |

D0 |

Q4 |

|

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

8

Продолжение таблицы 1.4

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

- |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

- |

|

|

|

|

|

|

|

|

|

|

|

9

1.3 ФУНКЦИОНАЛЬНАЯ СХЕМА

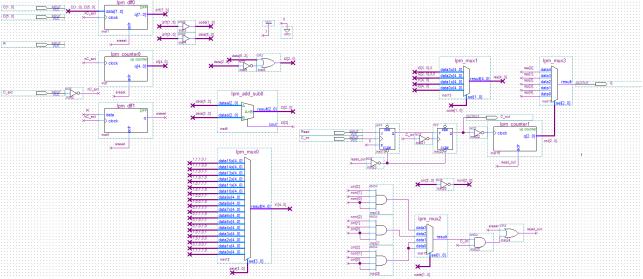

На рисунке 1.3.1 представлена полная функциональная схема

вычислительного блока, включающая в себя входную часть, выходную часть и

операционный блок для кодирования 4b5b-кода, логической побитовой операции

и арифметического сложения.

Рисунок 1.3.1 – Функциональная схема Далее, на рисунке 1.3.2 представлена подробно описанная входная часть.

Она состоит из записывающего регистра, на входы которого поданы данные (A, B) и код операции. На выходе этого регистра одна шина, которая после разделяется на две отдельные. Также во входную часть входит счетчик,

работающий задним фронтом. На счетчик подается сигнал внешнего синхроимпульса, а на выходе присутствует шина, которая в последствии будет использоваться в операционном блоке как код операции. Последнее устройство

– это регистр, который отвечает за синхронный сброс.

10