Рисунок 1.5.7 – Операционный блок В него идут значения из входного блока. При помощи кода операции

выбирается операция. В зависимости от кода операции происходит либо вычисление логической функции , либо арифметическое сложение, либо операция кодирования 4b5b-кода. На рисунках 1.5.8 – 1.5.9 представлена схема из RTL Viewer для данной части устройства.

21

Рисунок 1.5.8 – Схема из RTL Viewer операционного блока. Часть 1

22

Рисунок 1.5.9 – Схема из RTL Viewer операционного блока. Часть 2

23

Рисунок 1.5.10 – Выходной блок (1)

Рисунок 1.5.11 – Выходной блок (3)

24

Он считывает сигнал чтения и выдает данные последовательным кодом,

старшими разрядам вперёд. Выходной блок выдает разное количество сигналов в зависимости от кода. На рисунке 1.5.12 представлена схема из RTL Viewer для данной части устройства.

Рисунок 1.5.12 – Схема из RTL Viewer выходного блока

1.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

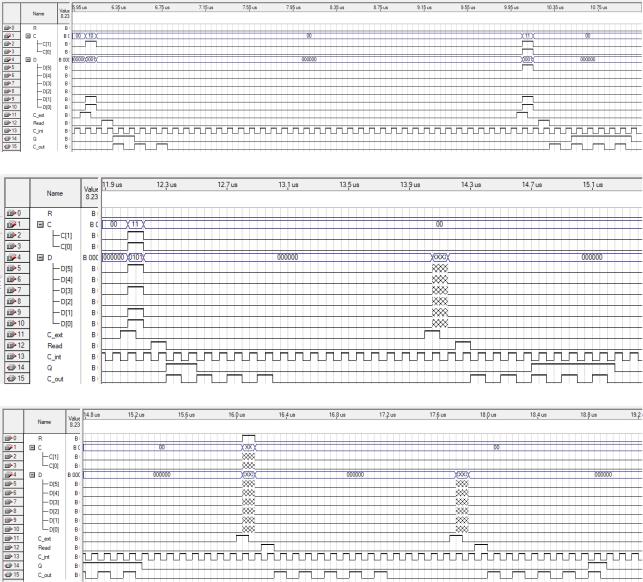

На рисунках 1.6.1 – 1.6.4 представлены результаты моделирования в режиме Timing. На рисунках 1.6.5 – 1.6.8 представлены результаты моделирования в режиме Functional. В промежуток 0-1400нс представлена работа первого сигнала, 2000-3200нс – второго, 4000-4800нс – третьего, 5950-

6800нс – четвертого, 10000-11000нс – пятого, 12000-13000нс – шестого, 14000-

15200нс – седьмого, 16000-17150нс – восьмого, 17700-19100нс – девятого.

Рисунок 1.6.1 – Моделирование в режиме Timing

25

Рисунок 1.6.2 – Моделирование в режиме Timing

Рисунок 1.6.3 – Моделирование в режиме Timing

Рисунок 1.6.4 – Моделирование в режиме Timing

Рисунок 1.6.5 – Моделирование в режиме Functional

26

Рисунок 1.6.6 – Моделирование в режиме Functional

Рисунок 1.6.7 – Моделирование в режиме Functional

Рисунок 1.6.8 – Моделирование в режиме Functional

Результаты совпадают с таблицей плана моделирования, что говорит о том, что все выполнено верно. Наблюдаются задержки на выходах, которые появляются по причине того, что на обработку информации каждым логическим элементом затрачивается некоторое время. В функциональном моделировании нет задержек по причине того, что в нем всё является идеализированным и логические функции обрабатываются моментально.

27

Заключение

В ходе выполнения лабораторной работы были спроектирован и реализован вычислительный блок, в котором приём входных данных осуществляется параллельным кодом с их синхронизацией по отдельной линии по заднему фронту сигнала. Вычислительный блок выполняет операцию согласно коду операции: 00 – операция не производится, на выход передаётся значение счётчика выполненных операций; 01 – кодирование двоичного числа в

4b5b-кода; 10 – над 3-х разрядными А и В выполняется логическая побитовая операция 3-х разрядный результат подаётся на выход; 11 – над 3-х

разрядными А и В выполняется арифметическая операция сложения, 3-х

разрядный результат подаётся на выход. Устройство имеет вход синхронного сброса, который сбрасывать все буферы. После получения логической единицы по линии «read» устройство производит выдачу полученных результатов последовательным кодом старшими разрядами вперёд. Синхронизация передаваемых разрядов осуществляется передним фронтом внутреннего синхросигнала. Для данного устройства была сделана функциональная схема,

написан код на языке описания аппаратуры System Verilog, а также произведено моделирование в обоих случаях.

Также получены навыки совместно применять устройства средней степени интеграции.

28