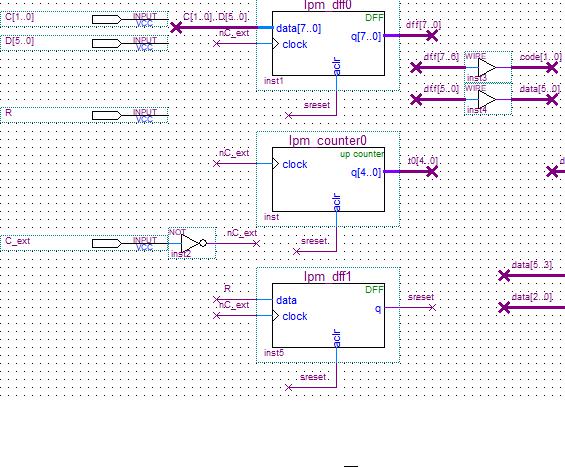

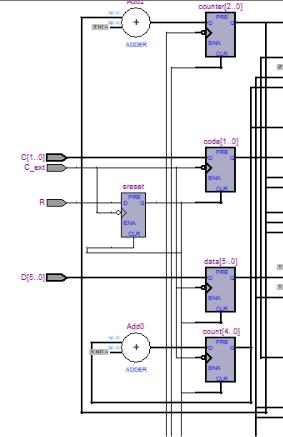

Рисунок 1.3.2 – Входная часть На рисунке 1.3.3 представлен операционный блок. Сверху представлен

блок для вычисления логической функции . Чуть ниже представлен блок для вычисления арифметического сложения, основанный на мультиплексоре.

На оба этих блока идут данные A, B. Третий блок в операционном блоке – это мультиплексор для кодирования 4b5b-кода. На него подается код.

Все три устройства имеют выходы, которые идут на один мультиплексор,

который за счет кода операции выбирает, какая операция пойдет на выход.

11

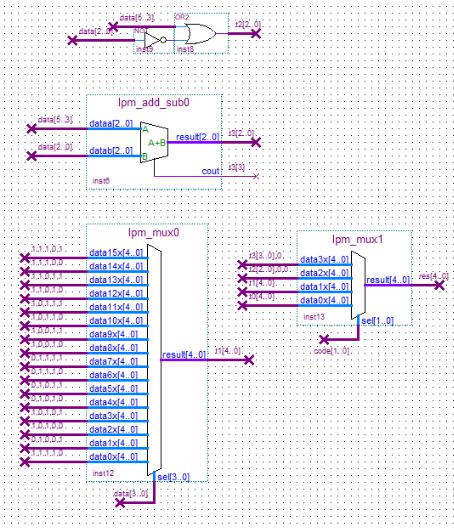

Рисунок 1.3.3 – Операционный блок На рисунке 1.3.4 представлена выходная часть. Так как вывод должен

быть последовательным, на lpm_mux3 – поступают данные с другого мультиплексора, который является частью операционного блока. Lpm_mux3

отвечает за то, какой из номеров сигнала шины пойдет на выход. Чтение происходит через jk-триггер, на который фиксирует сигнал «read», который не будет обновляться, пока не выйдут все необходимые данные. С этого триггера на T-триггер идет разрешающий сигнал, который переключается за счет внутреннего синхроимпульса. Его переключение по заднему фронту воздействует на счетчик, который считает сигналы. Ниже представлена конструкция, которая отвечает за сброс триггеров и счетчика. Также в этой конструкции присутствует костыль, который сделан для синхронизации сброса.

12

Рисунок 1.3.4 – Выходная часть

13

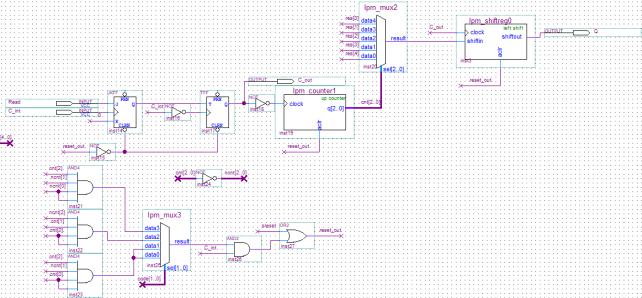

1.4МОДЕЛИРОВАНИЕ

Втаблице 1.5 представлен план моделирования для вычислительного

блока.

Таблица 1.5 – План моделирования

План моделирования

|

|

|

Входы |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Выходы |

|

||

|

Код |

|

|

|

Данные |

|

|

Сброс |

|

|

|||||

№Сигнала |

операции |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

C7 |

C6 |

D5 |

D4 |

|

D3 |

D2 |

D1 |

D0 |

R |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

1 |

0 |

1 |

X |

X |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

2 |

0 |

1 |

X |

X |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

3 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

- |

- |

4 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

- |

- |

5 |

1 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

- |

6 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

- |

7 |

0 |

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

1 |

1 |

1 |

|

8 |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

0 |

0 |

0 |

0 |

0 |

|

9 |

0 |

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

1 |

|

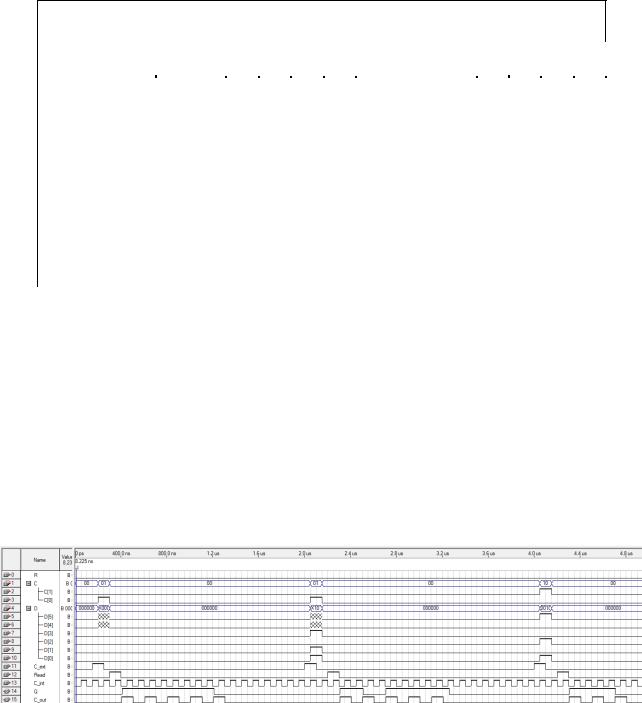

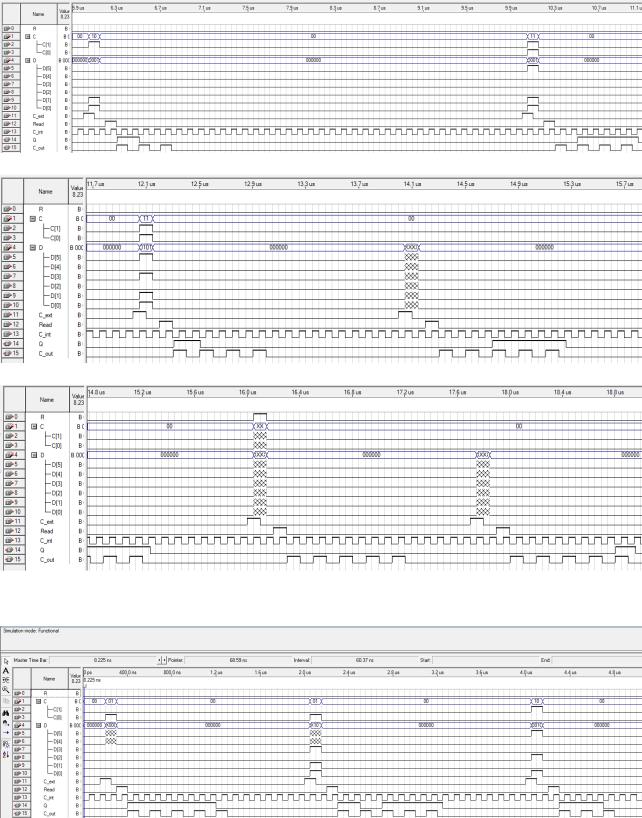

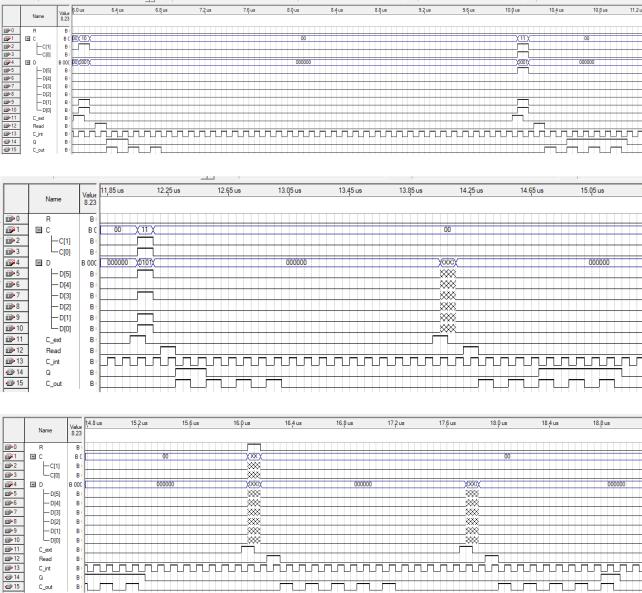

На рисунках 1.4.1 – 1.4.4 представлены результаты моделирования в режиме Timing. На рисунках 1.4.5 – 1.4.8 представлены результаты моделирования в режиме Functional. В промежуток 0-1400нс представлена работа первого сигнала, 2000-3200нс – второго, 4000-4800нс – третьего, 5950-

6800нс – четвертого, 10000-11000нс – пятого, 12000-13000нс – шестого, 14000-

15200нс – седьмого, 16000-17150нс – восьмого, 17700-19100нс – девятого.

Рисунок 1.4.1 – Моделирование в режиме Timing

14

Рисунок 1.4.2 – Моделирование в режиме Timing

Рисунок 1.4.3 – Моделирование в режиме Timing

Рисунок 1.4.4 – Моделирование в режиме Timing

Рисунок 1.4.5 – Моделирование в режиме Functional

15

Рисунок 1.4.6 – Моделирование в режиме Functional

Рисунок 1.4.7 – Моделирование в режиме Functional

Рисунок 1.4.8 – Моделирование в режиме Functional

Результаты совпадают с таблицей плана моделирования, что говорит о том, что все выполнено верно. Наблюдаются задержки на выходах, которые появляются по причине того, что на обработку информации каждым логическим элементом затрачивается некоторое время. В функциональном моделировании нет задержек по причине того, что в нем всё является идеализированным и логические функции обрабатываются моментально.

16

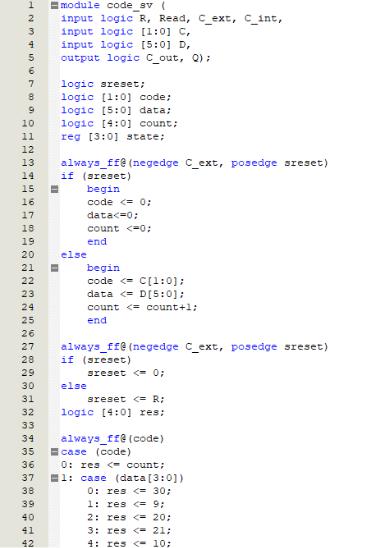

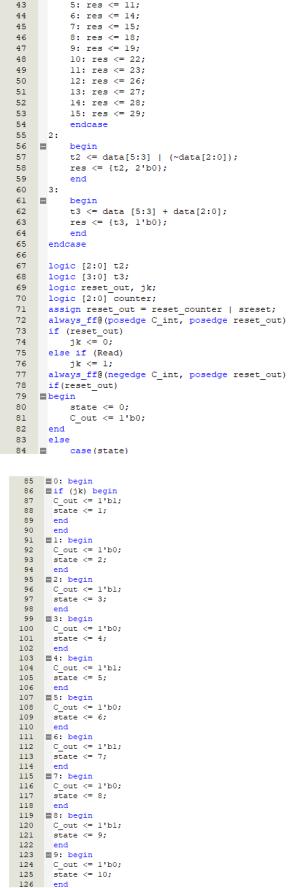

1.5 КОД НА HDL

На рисунках 1.5.1 – 1.5.4 представлен код схемы вычислительного блока,

написанного на языке описания аппаратуры System Verilog. Схема описана поведенчески и также включает в себя три основных блока: входной блок,

операционный блок и выходной блок. Также присутствуют и пути соединения блоков.

Рисунок 1.5.1 – Код на HDL (1)

17

Рисунок 1.5.2 – Код на HDL (2)

Рисунок 1.5.3 – Код на HDL (3) 18

Рисунок 1.5.4 – Код на HDL (4)

На рисунках 1.5.5, 1.5.7, 1.5.10 и 1.5.11 представлен каждый блок кода по отдельности.

Рисунок 1.5.5 – Входной блок

19

Он записывает данные поступающие по внешнему синхроимпульсу

C_ext, а также считает количество операций по тому же синхроимпульсу. На выходе у него записанные данные, код операций, а также значение счётчика. На рисунке 1.5.6 представлена схема из RTL Viewer для данной части устройства.

Рисунок 1.5.6 – Схема из RTL Viewer входного блока

20