Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ПРИМЕНЕНИЕ РЕГИСТРОВ И СЧЁТЧИКОВ

Отчет по лабораторной работе №7

по дисциплине «Электроника и схемотехника 2»

Вариант №9

Студент гр. ____

______________

__.__.2022

Преподаватель

каф. КИБЭВС

______________

__.__.2022

Томск 2022

Введение

Цель данной работы: научиться совместно применять регистры и счётчики. Постановка задачи:

1. Составить таблицы истинности для всех 4-х функций согласно варианту №9: обозначить в таблице порядок разрядов (старший и младший). Порядок разрядов во всех таблицах должен совпадать.

Функции для данного варианта:

7)= ( ) ∩

8)= ∩

9)= ∩

10)= ∩

2.Для выполнения 4-х параллельных операций над полубайтом организовать приём данных последовательным кодом старшими разрядам вперёд, с синхронным сбросом и синхронизацией данных по нарастающему фронту. Организовать выдачу данных параллельным кодом с синхронизацией по заднему фронту и активным уровнем сигнала «read» в 1.

3.Создать схемы, которые с помощью регистров обеспечат «чистый» выходной сигнал для асинхронного вычитающего счетчика с модулем счета 23,

атакже синхронного суммирующего счетчика с модулем счета 29, согласно варианту по ЛР5.

4.Промоделировать работу схем в двух режимах. Провести анализ результатов моделирования разных режимов.

5.Сверить результаты моделирования с составленными таблицами истинности.

6.Повторить п. 2-5, только для описания устройств вместо схем на холстах .bdf, используя VHDL согласно варианту.

7.Написать выводы о проделанной работе.

2

1.ВЫЧИСЛИТЕЛЬ ФУНКЦИЙ

1.1ТАБЛИЦА ИСТИННОСТИ

Ниже представлена таблица истинности для всех 4-х функций, согласно

данному варианту (таблица 1.1).

Функции для данного варианта:

7)= ( ) ∩

8)= ∩

9)= ∩

10)= ∩

Таблица 1.1 – таблица истинности функций

|

|

Входы |

|

|

|

Выходы |

|

||

|

|

|

|

|

F |

|

|||

|

|

|

|

|

|

|

|

||

x |

y |

|

z |

w |

10 |

9 |

|

8 |

7 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

3

1.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

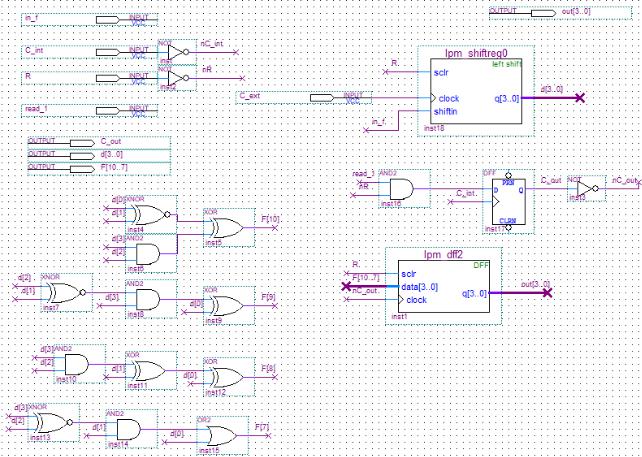

Ниже представлена функциональная схема для вычислителя функций с приёмом данных с последовательным кодом старшими разрядам вперёд,

синхронным сбросом и синхронизацией данных по нарастающему фронту и выдачей данных параллельным кодом с синхронизацией по заднему фронту и активным уровнем сигнала «read» в 1 (рисунок 1.2.1).

Рисунок 1.2.1 – Функциональная схема вычислителя функций

4

1.3 МОДЕЛИРОВАНИЕ

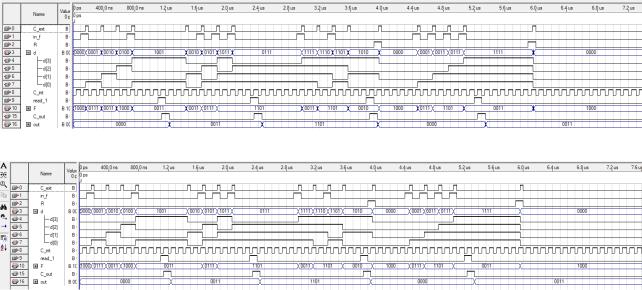

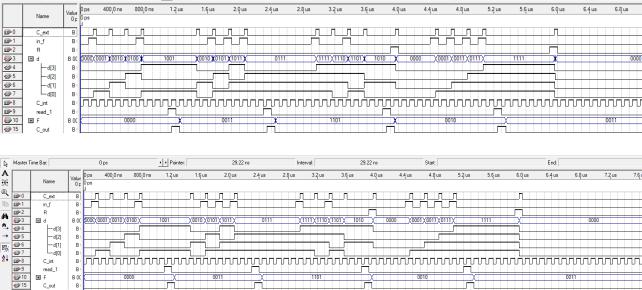

На рисунке 1.3.1 представлен результат моделирования в режиме Timing.

На рисунке 1.3.2 представлен результат моделирования в режиме Functional.

Рисунок 1.3.1 – Результат моделирования в режиме Timing

Рисунок 1.3.2 – Результат моделирования в режиме Functional

Результаты совпадают с таблицей функционирования, что говорит о том,

что все выполнено верно.

5

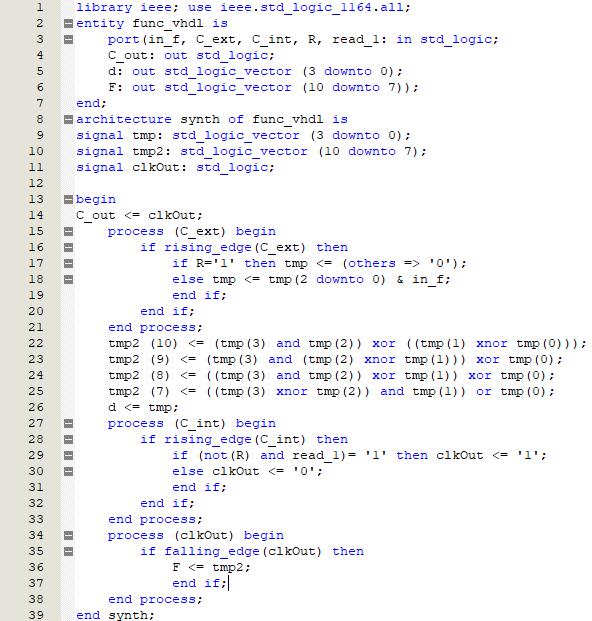

1.4 КОД НА HDL

На рисунке 1.4.1 представлен рисунок с кодом на VHDL для вычислителя

функций.

Рисунок 1.4.1 – Код схемы на VHDL

6

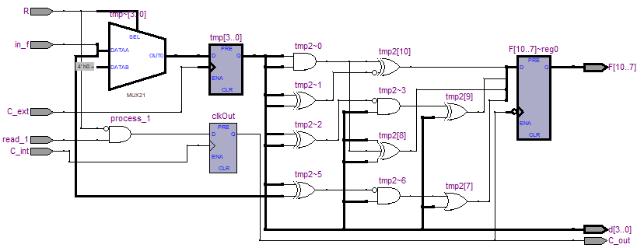

1.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 1.5.1 представлена схема из RTL Viewer для кода VHDL.

Рисунок 1.5.1– Схема из RTL Viewer

7

1.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

На рисунке 1.6.1 представлен результат моделирования в режиме Timing.

На рисунке 1.6.2 представлен результат моделирования в режиме Functional.

Рисунок 1.6.1 – Результат моделирования в режиме Timing

Рисунок 1.6.2 – Результат моделирования в режиме Functional

Результаты совпадают с таблицей функционирования, что говорит о том,

что все выполнено верно.

8

2.АССИНХРОННЫЙ СЧЕТЧИК С ВЫХОДНЫМ БУФЕРОМ

2.1ТАБЛИЦА ИСТИННОСТИ

Ниже представлена таблица функционирования асинхронного вычитающего счетчика с модулем счета 23 и с «чистым» выходным сигналом, сделанным с помощью регистра (таблица 2.1).

Таблица 2.1 – Таблица истинности асинхронного счётчика

|

|

|

Выходы |

|

|

Число в |

№Сигнала |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

10ой |

|

системе |

|||||

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

1 |

0 |

22 |

|

|

|

|

|

|

|

2 |

1 |

0 |

1 |

0 |

1 |

21 |

|

|

|

|

|

|

|

3 |

1 |

0 |

1 |

0 |

0 |

20 |

|

|

|

|

|

|

|

4 |

1 |

0 |

0 |

1 |

1 |

19 |

|

|

|

|

|

|

|

5 |

1 |

0 |

0 |

1 |

0 |

18 |

|

|

|

|

|

|

|

6 |

1 |

0 |

0 |

0 |

1 |

17 |

|

|

|

|

|

|

|

7 |

1 |

0 |

0 |

0 |

0 |

16 |

|

|

|

|

|

|

|

8 |

0 |

1 |

1 |

1 |

1 |

15 |

|

|

|

|

|

|

|

9 |

0 |

1 |

1 |

1 |

0 |

14 |

|

|

|

|

|

|

|

10 |

0 |

1 |

1 |

0 |

1 |

13 |

|

|

|

|

|

|

|

11 |

0 |

1 |

1 |

0 |

0 |

12 |

|

|

|

|

|

|

|

12 |

0 |

1 |

0 |

1 |

1 |

11 |

|

|

|

|

|

|

|

13 |

0 |

1 |

0 |

1 |

0 |

10 |

|

|

|

|

|

|

|

14 |

0 |

1 |

0 |

0 |

1 |

9 |

|

|

|

|

|

|

|

15 |

0 |

1 |

0 |

0 |

0 |

8 |

|

|

|

|

|

|

|

16 |

0 |

0 |

1 |

1 |

1 |

7 |

|

|

|

|

|

|

|

17 |

0 |

0 |

1 |

1 |

0 |

6 |

|

|

|

|

|

|

|

18 |

0 |

0 |

1 |

0 |

1 |

5 |

|

|

|

|

|

|

|

19 |

0 |

0 |

1 |

0 |

0 |

4 |

|

|

|

|

|

|

|

20 |

0 |

0 |

0 |

1 |

1 |

3 |

|

|

|

|

|

|

|

21 |

0 |

0 |

0 |

1 |

0 |

2 |

|

|

|

|

|

|

|

22 |

0 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

23 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

9

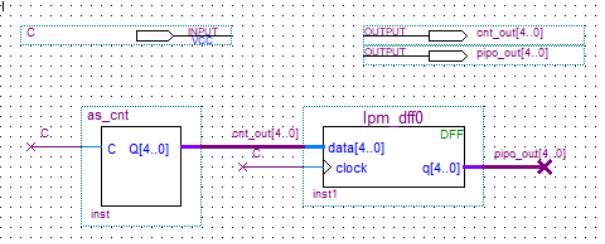

2.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 2.2.1 представлена функциональной схемы асинхронного счетчика с выходным буфером.

Рисунок 2.2.1 – Функциональная схема счетчика

10