3.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

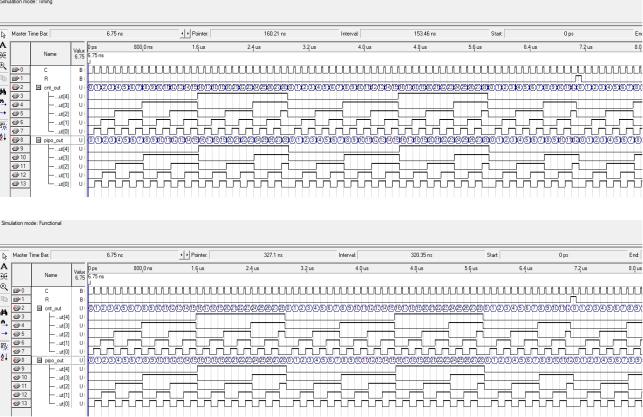

На рисунке 3.6.1 представлен результат моделирования кода в режиме с задержками. На рисунке 3.6.2 представлен результат моделирования без задержек.

Рисунок 3.6.1 – Результат моделирования в режиме с задержками

Рисунок 3.6.2 – Результат моделирования в режиме без задержек Результаты совпадают с таблицей истинности, что говорит о том, что все

выполнено верно.

21

Заключение

В ходе выполнения лабораторной работы были изучены принципы совместного применения регистров и счетчиков. Согласно варианту, были построены на холсте и с помощью кода VHDL следующие схемы:

1) Вычислителя функций с приёмом данных с последовательным кодом старшими разрядам вперёд, синхронным сбросом и синхронизацией данных по нарастающему фронту и выдачей данных параллельным кодом с синхронизацией по заднему фронту и активным уровнем сигнала «read» в 1 для следующих функций:

= ( ) ∩= ∩= ∩= ∩

2) Асинхронного вычитающего счетчика с модулем счета 23 и выходным буфером из ЛР5.

3) Синхронного суммирующего счетчика с модулем счета 29 и выходным буфером из ЛР5.

22