2.3 МОДЕЛИРОВАНИЕ

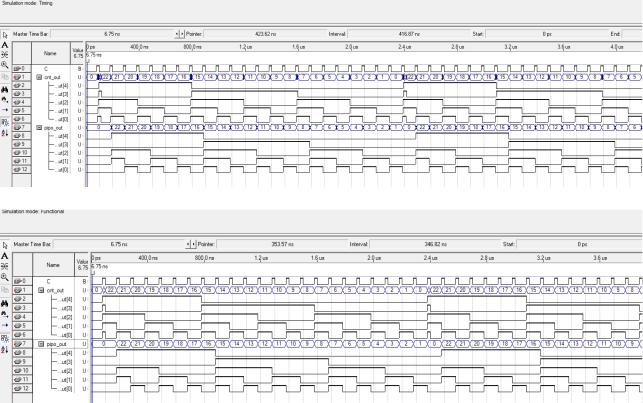

На рисунке 2.3.1 представлен результат моделирования в режиме Timing.

На рисунке 2.3.2 представлен результат моделирования в режиме Functional.

Рисунок 2.3.1 - Результат моделирования в режиме Timing

Рисунок 2.3.2 - Результат моделирования в режиме Functional

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено верно.

11

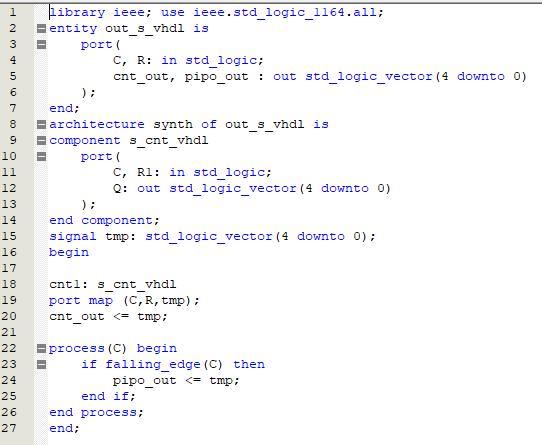

2.4 КОД НА HDL

На рисунке 2.4.1 представлен код на VHDL схемы асинхронного счетчика с выходным буфером.

Рисунок 2.4.1 – Код схемы на VHDL

12

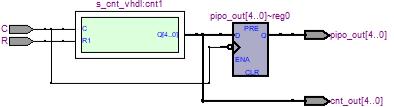

2.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

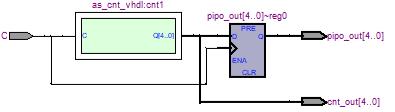

На рисунке 2.5.1 представлена схема из RTL Viewer для кода VHDL.

Рисунок 2.5.1 – Схема из RTL Viewer

13

2.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

На рисунке 2.6.1 представлен результат моделирования кода в режиме с задержками. На рисунке 2.6.2 представлен результат моделирования без задержек.

Рисунок 2.6.1 – Результат моделирования в режиме Timing

Рисунок 2.6.2 – Результат моделирования в режиме Functional

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено верно. Наблюдаются задержки на выходах, которые появляются по причине того, что на обработку информации каждым логическим элементом затрачивается некоторое время. В функциональном моделировании нет задержек по причине того, что в нем всё является идеализированным и логические функции обрабатываются моментально.

14

3.СИНХРОННЫЙ СЧЕТЧИК С ВЫХОДНЫМ БУФЕРОМ

3.1ТАБЛИЦА ИСТИННОСТИ

Ниже представлена таблица функционирования синхронного суммирующего счетчика с модулем счета 29 и с «чистым» выходным сигналом, сделанным с помощью регистра (таблица 3.1).

Таблица 3.1 – Таблица истинности синхронного счётчика

|

|

|

|

Выходы |

|

|

Число |

|

№Сигна |

|

|

|

|

|

|

|

в 10ой |

|

|

|

|

|

|

|

||

ла |

R |

Q4 |

Q3 |

|

Q2 |

Q1 |

Q0 |

систем |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

0 |

|

0 |

1 |

0 |

2 |

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

0 |

|

0 |

1 |

1 |

3 |

|

|

|

|

|

|

|

|

|

4 |

0 |

0 |

0 |

|

1 |

0 |

0 |

4 |

|

|

|

|

|

|

|

|

|

5 |

0 |

0 |

0 |

|

1 |

0 |

1 |

5 |

|

|

|

|

|

|

|

|

|

6 |

0 |

0 |

0 |

|

1 |

1 |

0 |

6 |

|

|

|

|

|

|

|

|

|

7 |

0 |

0 |

0 |

|

1 |

1 |

1 |

7 |

|

|

|

|

|

|

|

|

|

8 |

0 |

0 |

1 |

|

0 |

0 |

0 |

8 |

|

|

|

|

|

|

|

|

|

9 |

0 |

0 |

1 |

|

0 |

0 |

1 |

9 |

|

|

|

|

|

|

|

|

|

10 |

0 |

0 |

1 |

|

0 |

1 |

0 |

10 |

|

|

|

|

|

|

|

|

|

11 |

0 |

0 |

1 |

|

0 |

1 |

1 |

11 |

|

|

|

|

|

|

|

|

|

12 |

0 |

0 |

1 |

|

1 |

0 |

0 |

12 |

|

|

|

|

|

|

|

|

|

13 |

0 |

0 |

1 |

|

1 |

0 |

1 |

13 |

|

|

|

|

|

|

|

|

|

14 |

0 |

0 |

1 |

|

1 |

1 |

0 |

14 |

|

|

|

|

|

|

|

|

|

15 |

0 |

0 |

1 |

|

1 |

1 |

1 |

15 |

|

|

|

|

|

|

|

|

|

16 |

0 |

1 |

0 |

|

0 |

0 |

0 |

16 |

|

|

|

|

|

|

|

|

|

17 |

0 |

1 |

0 |

|

0 |

0 |

1 |

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

Продолжение таблицы 3.1

|

|

|

|

Выходы |

|

|

Число |

|

№Сигна |

|

|

|

|

|

|

|

в 10ой |

|

|

|

|

|

|

|

||

ла |

R |

Q4 |

Q3 |

|

Q2 |

Q1 |

Q0 |

систем |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

|

|

18 |

0 |

1 |

0 |

|

0 |

1 |

0 |

18 |

|

|

|

|

|

|

|

|

|

19 |

0 |

1 |

0 |

|

0 |

1 |

1 |

19 |

|

|

|

|

|

|

|

|

|

20 |

0 |

1 |

0 |

|

1 |

0 |

0 |

20 |

|

|

|

|

|

|

|

|

|

21 |

0 |

1 |

0 |

|

1 |

0 |

1 |

21 |

|

|

|

|

|

|

|

|

|

22 |

0 |

1 |

0 |

|

1 |

1 |

0 |

22 |

|

|

|

|

|

|

|

|

|

23 |

0 |

1 |

0 |

|

1 |

1 |

1 |

23 |

|

|

|

|

|

|

|

|

|

24 |

0 |

1 |

1 |

|

0 |

0 |

0 |

24 |

|

|

|

|

|

|

|

|

|

25 |

0 |

1 |

1 |

|

0 |

0 |

1 |

25 |

|

|

|

|

|

|

|

|

|

26 |

0 |

1 |

1 |

|

0 |

1 |

0 |

26 |

|

|

|

|

|

|

|

|

|

27 |

0 |

1 |

1 |

|

0 |

1 |

1 |

27 |

|

|

|

|

|

|

|

|

|

28 |

0 |

1 |

1 |

|

1 |

0 |

0 |

28 |

|

|

|

|

|

|

|

|

|

29 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

30 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

31 |

0 |

0 |

0 |

|

0 |

1 |

0 |

2 |

|

|

|

|

|

|

|

|

|

32 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

33 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

16

3.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 3.2.1 представлена функциональная схема синхронного счетчика с выходным буфером.

Рисунок 3.2.1 – Функциональная схема счетчика

17

3.3 МОДЕЛИРОВАНИЕ

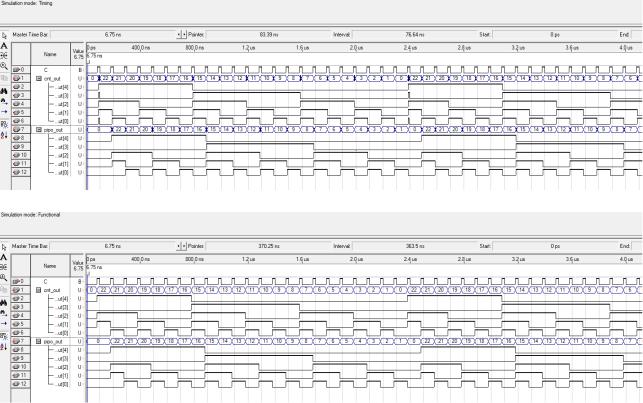

На рисунке 3.3.1 представлен результат моделирования в режиме Timing.

На рисунке 3.3.2 представлен результат моделирования в режиме Functional.

Рисунок 3.3.1 - Результат моделирования в режиме Timing

Рисунок 3.3.2 - Результат моделирования в режиме Functional

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено верно.

18

3.4 КОД НА HDL

На рисунке 3.4.1 представлен код на VHDL для суммирующего синхронного счетчика с выходным буфером.

Рисунок 3.4.1 – Код схемы на VHDL

19

3.5СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

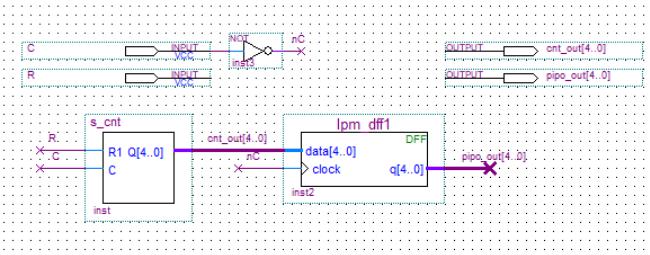

На рисунке 3.5.1 представлена схема из RTL Viewer для кода VHDL.

Рисунок 3.5.1 – Схема из RTL Viewer

20