21

3.2 Формула

Ниже представлена формула для каждого выхода:

1( + 1) = ( ) ( )1( + 1) = ( ) ( )

2( + 2) = 1( + 1) 2( + 1)2( + 2) = 1( + 1) 2( + 1)3( + 3) = 2( + 2) ( + 2)3( + 3) = 2( + 2) ( + 2)

( + 4) = 3( + 3) ( + 3)( + 4) = 3( + 3) ( + 3)

22

3.3 Функциональная схема

На рисунке 3.3.1 представлена функциональная схема D-триггера.

Рисунок 3.3.1 – D-триггер

23

3.4 Моделирование функциональной схемы

На рисунках 3.4.1 – 3.4.2 представлено моделирование функциональной

схемы в двух режимах, timing и functional соответственно. Из рисунков видно,

что моделирование полностью совпадает с таблицей истинности.

Рисунок 3.4.1 – Моделирование в режиме Timing

Рисунок 3.4.2 – Моделирование в режиме Functional

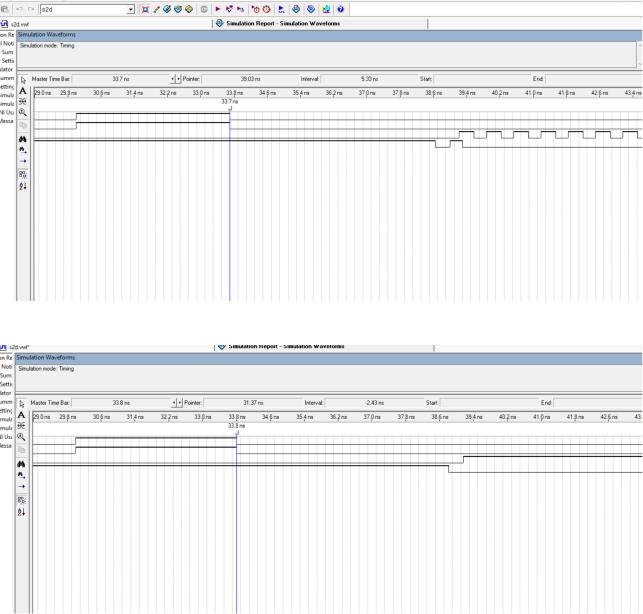

Далее на рисунках 3.4.3 – 3.4.4 был исследован минимальный порог длительности активного уровня управляющего сигнала. Видно, что 3.7 ns не достаточно, а 3.8 ns достаточно.

24

Рисунок 3.3.3 – Недостаточное количество

Рисунок 3.3.4 – Достаточное количество

25

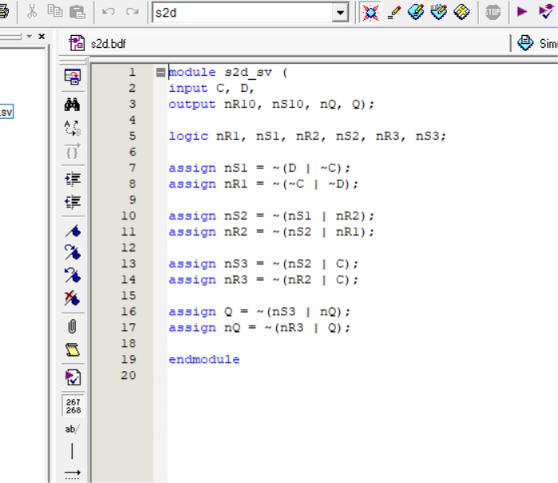

3.5 Код на HDL

На рисунке 3.5.1 представлен код описания триггера на System Verilog.

Рисунок 3.5.1 – Код на System Verilog

26

3.6 Схема RTL viewer для кода HDL

На рисунке 3.6.1 представлена схема RTL viewer для кода, написанном на

System Verilog.

Рисунок 3.6.1 – Схема RTL Viewer

27

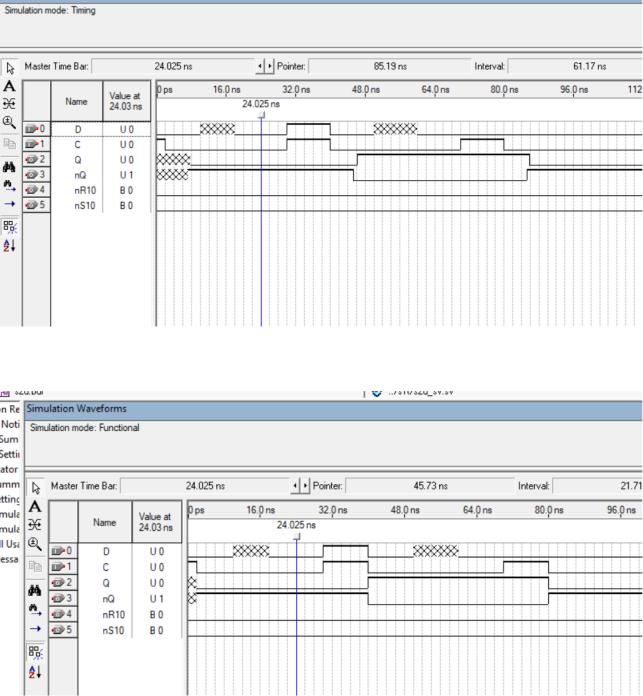

3.7 Моделирование устройства, описанного кодом HDL.

На рисунках 3.7.1 – 3.7.2 представлено моделирование функциональной схемы в двух режимах, timing и functional соответственно. Из рисунков видно,

что моделирование полностью совпадает с таблицей истинности.

Рисунок 3.7.1 – Моделирование в режиме Timing

Рисунок 3.7.2 – Моделирование в режиме Functional

28

ВЫВОДЫ

В ходе данной работы были созданы JK-триггер, T-триггер и D-триггер на разных базисах.

Был реализован динамический JK-триггер в базисе И-НЕ.

Промоделирован в двух режимах и описан на System Verilog. Был исследован минимальный порог длительности активного уровня управляющего сигнала –

1.3ns.

Был реализован одноступенчатый T-триггер в базисе И-НЕ.

Промоделирован в двух режимах и описан на System Verilog. Был исследован минимальный порог длительности активного уровня управляющего сигнала –

0.4ns.

Был реализован двухступенчатый D-триггер в базисе ИЛИ-НЕ.

Промоделирован в двух режимах и описан на System Verilog. Был исследован минимальный порог длительности активного уровня управляющего сигнала –

3.8ns.