11

1.7 Моделирование устройства, описанного кодом HDL

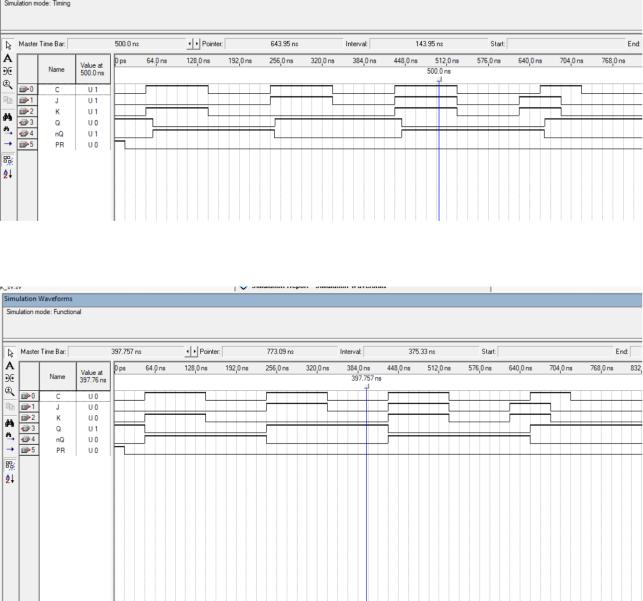

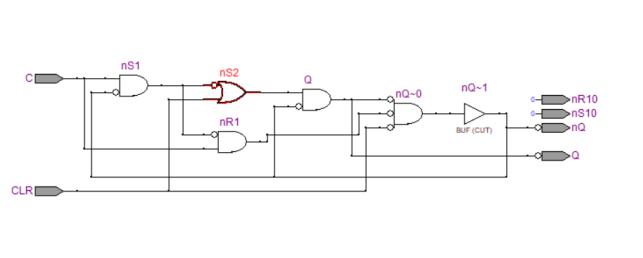

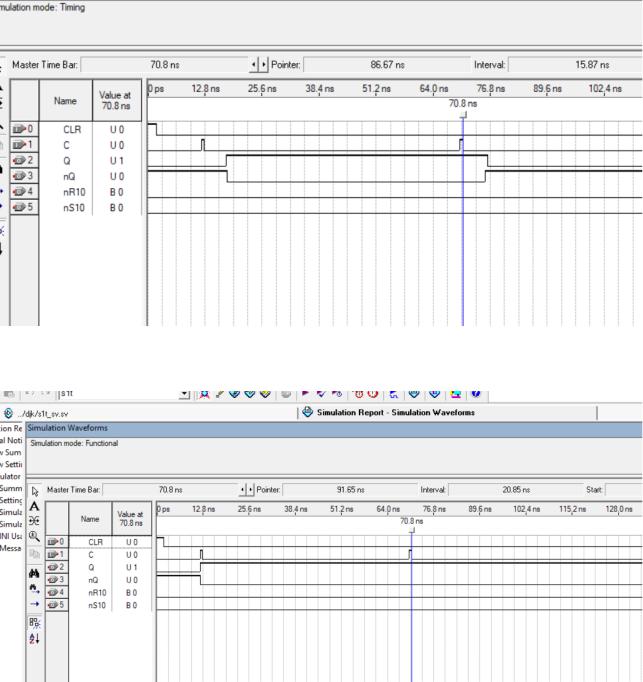

На рисунках 1.7.1 – 1.7.2 представлено моделирование функциональной схемы в двух режимах, timing и functional соответственно. Из рисунков видно,

что моделирование полностью совпадает с таблицей истинности.

Рисунок 1.7.1 – Моделирование в режиме Timing

Рисунок 1.7.2 – Моделирование в режиме Functional

12

2Одноступенчатый Т-триггер

2.1Таблица истинности

Втаблице 2.1 представлены все входы-выходы и режимы работы для данного триггера.

Таблица 2.1 – Таблица функционирования.

Входы |

Выходы |

|

Режим |

|

|

|

|

|

|

C |

Q(t) |

|

Q(t+1) |

|

|

|

|

|

|

0 |

0/1 |

|

0/1 |

хранение |

|

|

|

|

|

1 |

1 |

|

0 |

Счетный из 1 в 0 |

|

|

|

|

|

1 |

0 |

|

1 |

Счетный из 0 в 1 |

|

|

|

|

|

13

2.2 Формула

Ниже представлена формула для каждого выхода:

1( + 1) = 1( ) ∩ ( )

1( + 1) = ( ) ∩ ( )

( + 2) = 2( + 1) ∩ ( + 1)

( + 2) = 2( + 1) ∩ ( + 1)

14

2.3 Функциональная схема

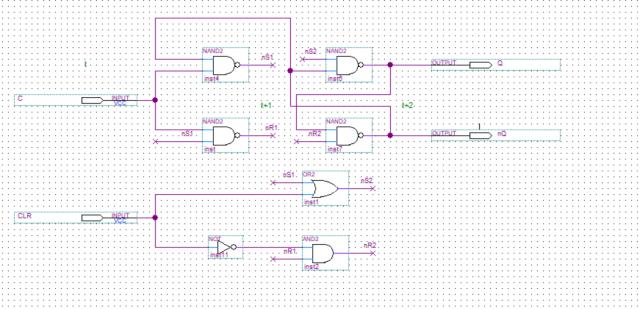

На рисунке 2.3.1 представлена функциональная схема Т-триггера.

Рисунок 2.3.1 – Т-триггер

15

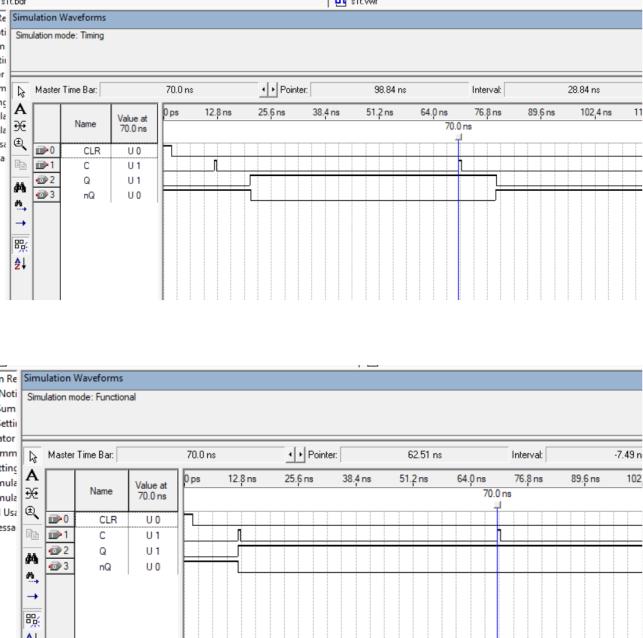

2.4 Моделирование функциональной схемы

На рисунках 2.4.1 – 2.4.2 представлено моделирование функциональной

схемы в двух режимах, timing и functional соответственно. Из рисунков видно,

что моделирование полностью совпадает с таблицей истинности.

Рисунок 2.4.1 – Моделирование в режиме Timing

Рисунок 2.4.2 – Моделирование в режиме Functional

Далее на рисунках 2.4.3 – 2.4.4 был исследован минимальный порог длительности активного уровня управляющего сигнала. Видно, что 0,3 ns не достаточно, а 0.4 ns достаточно.

16

Рисунок 2.3.3 – Недостаточное количество

Рисунок 2.3.4 – Достаточное количество

17

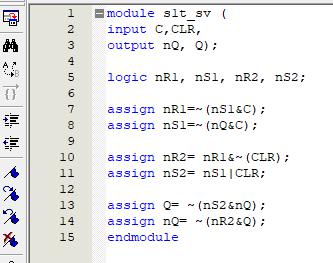

2.5 Код на HDL

На рисунке 2.5.1 представлен код описания триггера на System Verilog.

Рисунок 2.5.1 – Код на System Verilog

18

2.6 Схема RTL viewer для кода HDL

На рисунке 2.6.1 представлена схема RTL viewer для кода, написанном на

System Verilog.

Рисунок 2.6.1 – Схема RTL Viewer

19

2.7 Моделирование устройства, описанного кодом HDL.

На рисунках 2.7.1 – 2.7.2 представлено моделирование функциональной схемы в двух режимах, timing и functional соответственно. Из рисунков видно,

что моделирование полностью совпадает с таблицей истинности.

Рисунок 2.7.1 – Моделирование в режиме Timing

Рисунок 2.7.2 – Моделирование в режиме Functional

20

3 Двухступенчатый D-триггер

3.1Таблица истинности

Втаблице 3.1 представлены все входы-выходы и режимы работы для данного триггера.

Таблица 3.1 – Таблица функционирования.

Входы |

|

Выходы |

|

Режим |

|

|

|

|

|

D |

C |

Q(t) |

Q(t+1) |

|

|

|

|

|

|

x |

0 |

0/1 |

0/1 |

хранение |

|

|

|

|

|

0 |

1 |

x |

0 |

установка в 0 |

|

|

|

|

|

1 |

1 |

x |

1 |

установка в 1 |

|

|

|

|

|