- •Введение

- •1. Программа учебной дисциплины «Проектирование цифровых устройств для 3d изделий»

- •2. Конспект лекций Лекция № 1. Методология проектирования цифровых устройств для 3d изделий

- •Лекция № 2. Описание цифрового устройства на hdl языках

- •Лекция № 3. Топологическое проектирование цифровых устройств для 3d изделий

- •Лекция № 4. Технологические правила для разработки топологии цифровых устройств

- •Лекция № 5. Трассировка межсоединений

- •Лекция № 6. Синхронизация цифровых устройств

- •Лекция № 7. Разводка питающих цепей Энергетическая оптимизация. Статический и динамический анализ питания

- •Лекция № 8. Физическая верификация топологии цифрового устройства

- •3. Методические указания по проведению вЕбинара

- •4. Контроль усвоенного материала. Тестовые вопросы

- •5. Методические указания по выполнению практических заданий Практическая работа № 1. Моделирование цифрового устройства на rtl уровне

- •Практическая работа № 2. Логический синтез цифрового устройства на основе отлаженного rtl кода

- •Практическая работа № 3. Физическая верификация топологии цифрового устройства

- •6. Методика дистанционного выполнения практических заданий

- •7. Методические указания преподавателям, ведущим занятия по дисциплине

- •8. Методические указания по самостоятельной работе слушателей

- •9. Методические указания слушателям по изучению дисциплины

- •10. Цифровые образовательные ресурсы

- •11. Вопросы самопроверки

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

Лекция № 8. Физическая верификация топологии цифрового устройства

Проектирование топологии завершается этапом физической верификации – важным этапом, который включает в себя:

- проверку топологии на соответствие правилам и нормам проектирования (КТТ – конструкторско-технологические требования) технологического процесса;

- извлечение из топологии электрической схемы;

- верификацию экстрактированной схемы и электрической схемы проекта.

Основными целями физической верификации являются:

- подтверждение соответствия разработанной топологии КТТ;

- подтверждение соответствия разработанной топологии и электрической схемы.

Современные средства САПР, используемые для разработки цифровых блоков, позволяют осуществить полный комплекс физической верификации. Приложения, используемые для физической верификации проектов, должны обладать высоким быстродействием. Таковыми являются приложения Diva, Assura и Calibre. Наибольшую популярность получили программы Assura (Cadence) и Calibre (Mentor Graphics).

Проверка правил проектирования (DRC)

На этапе проверки правил проектирования проверяются геометрические соотношения слоев на соответствие конструкторско-технологическим нормам технологического процесса (DRC – Design Rule Checking). Все нормы КТТ определены в управляющем файле проверки DRC. Данный файл поставляется в составе библиотеки заводом-изготовителем либо разрабатывается самостоятельно при условии знания технологического процесса и требований КТТ.

Проверка правил проектирования в приложении Diva

Запуск приложения Diva осуществляется из меню Verify/DRC топологического редактора Virtuoso (рис. 2.15). Для выполнения проверки проектных норм необходимо настроить: 1) Checking Method – метод проверки: flat – раскрытие топологии во время выполнения проверки, hierarchical – иерархическая проверка; 2) Join Nets With Same Name – соединение одноименных шин; 3) Rules File – название и место расположения управляющего файла.

Рис. 2.15. Интерфейс программы Diva DRC

После завершения проверки проектных норм в окне icfb будет выведена информация о найденных ошибках в формате, показанном на рис. 2.16.

Рис. 2.16. Сведения об обнаруженных ошибках КТТ

Diva DRC информирует о числе обнаруженных ошибок для каждого отдельного нарушенного правила и общем количестве ошибок. При нахождении ошибки программа автоматически размещает в топологии маркер на месте обнаружения ошибки. Для просмотра ошибок необходимо выбрать в меню «Verify/Marker/Find…». При выполнении команды откроется окно Find Marker, показанное на рис. 2.17.

Рис. 2.17. Окно поиска ошибок Find Marker

Основные установки, необходимые для просмотра и исправления ошибок:

- Zoom To Marker – увеличение места ошибки до размера экрана;

- Severity – выбор варианта просмотра: warning – просмотр предупреждений, error – просмотр ошибок;

- Search Scope – границы поиска ошибок: cellview – в ячейке, hierarchy – иерархический поиск, library – в указанной библиотеке. Для типов cellview и hierarchy доступны дополнительные настройки – старт поиска с: top cellview – верхней ячейки, current cellview – для текущей ячейки;

- Find by – поиск в: master cell only – только в верхней ячейке, all occurrences – во всех ячейках.

После того, как все настройки определены, при нажатии на кнопку «Next» будет осуществлен переход к месту следующей ошибки, при нажатии на кнопку «Previous» будет осуществлен переход к предыдущей ошибке. При нахождении места первой ошибки открывается окно marker text, в котором будут указаны в текстовом виде: 1) location: (библиотека, название ячейки, тип представления) – место нахождения ошибки; 2) reason: правило – нарушенное правило.

При переходе к следующим ошибкам в окне marker text будут добавляться новые сведения об ошибках.

Перебирая последовательно все ошибки, их исправляют и запускают процесс проверки сначала. При этом в случае верного исправления ошибок маркеры с места этих ошибок удаляются.

Проверка правил проектирования в приложении Assura

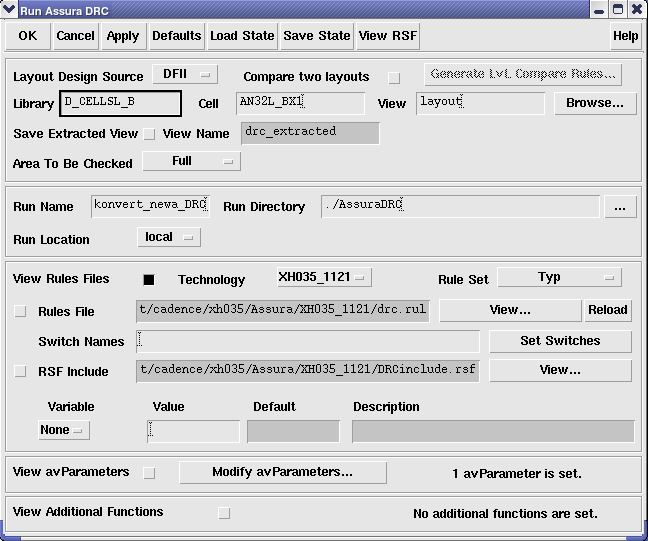

Запуск приложения Assura DRC, предназначенного для проверки проектных норм, осуществляется из меню «Assura/Run DRC» редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рис. 2.18.

Рис. 2.18. Интерфейс программы Assura DRC

Для осуществления проверки необходимо задать следующие настройки программы: 1) место расположения проверяемого файла: а) Library – директория; б) Cell – название ячейки проекта; в) View – представление (обычно Layout), 2) рабочую среду: а) Run Name – имя процесса; б) Run Directory – рабочая директория, где будет сохраняться текущий выполняемый процесс (по умолчанию Assura DRC); 3) параметры технологии проектирования: а) технологический процесс (Technology); б) место расположения и название управляющего файла проверки.

После выполнения проверки норм КТТ Assura выведет результаты проверки в окне Error Layer Window, показанном на рис. 2.19.

Рис. 2.19. Окно поиска исправления ошибок Error Layer Window

В левой части окна ELW перечислены правила проектирования в виде списка, которые были нарушены (обнаруженные ошибки). В каждой строке сначала указывается цвет, которым будет подсвечена ошибка данного правила, затем в квадратных скобках указано число подобных ошибок и название правила. Обычно в названии правила также указывается необходимое минимальное/максимальное численное значение требований (в мкм.). Вверху слева указывается текущее выбранное правило проектирования и его название. Справа в поле для текущего правила указывается топологическая ячейка, в которой эта ошибка найдена. С помощью стрелок вправо/ влево осуществляется переход к следующей/предыдущей ошибке, которая будет подсвечена в топологии в виде цветного полигона.

Дополнительные возможности: кнопки «AV» и «NV» показывают/скрывают все подсвеченные ошибки; нажатием правой кнопкой мыши можно изменять цвет подсветки ошибок; для перехода к какой-либо конкретной ошибке можно ввести число этой ошибки в правой верхней части окна в поле «numbers».

Проверка правил проектирования в приложении Calibre

Запуск приложения Calibre DRC осуществляется из меню Calibre/Run DRC окна редактора топологии Virtuoso (рис. 2.20).

Рис. 2.20. Окно проверки правил проектирования Calibre DRC

Перед началом проверки необходимо задать название и место расположения файла проверки calibre.drc, а также место размещения и название рабочего каталога Run Directory. Во вкладке Input необходимо задать: тип проверки (иерархический или одноуровневый), имя входного GDS-файла, название ячейки верхнего уровня. Во вкладке Outputs требуется определить: название базы данных с результатами проверки, формат базы данных, имя выходного файла-отчета о проверке.

В меню Setup/Select Checks… осуществляется выбор правил/групп правил проектирования, которые необходимо проверить (рис. 2.21).

Рис. 2.21. Окно выбора правил проектирования

После окончания проверки появится окно Calibre DRC RVE, в котором отобразятся результаты проверки правил проектирования (рис. 2.22).

Рис. 2.22. Окно поиска и просмотра ошибок Callibre DRC RVE

Окно Calibre RVE содержит полный список всех правил проектирования. Правила, не прошедшие проверку будут выделены красным квадратом. Для просмотра ошибок по любому из этих правил необходимо раскрыть список и кликнуть по одной из ошибок. При этом в топологии будет подсвечена область ошибки, в правой части окна Calibre DRC RVE будет отображена информация о координатах ошибочного полигона, а в нижней части будет выведен отчет, содержащий текстовую информацию об ошибке и правило, по которому осуществлялась проверка. Перебирая найденные ошибки по всему списку правил, их исправляют и запускают проверку снова.

Верификация топологии и электрической схемы (LVS)

Верификация электрических схем является заключительным этапом проектирования топологии устройства и проходит в два этапа. На первом этапе осуществляется извлечение списка соединений (нетлист), на втором – выполняется сравнение экстрактированной схемы и электрической принципиальной схемы с целью поиска несоответствий по сетям и приборам, а также номиналам и размерам приборов топологии и схемы.

Верификация в программе Diva

Верификация в приложении Diva осуществляется в два этапа: вначале выполняется экстракция электрической схемы из топологии, а лишь затем производится непосредственно верификация.

Экстракция выполняется с помощью приложения Diva EXT. Запуск приложения выполняется из меню «Verify/Extract». Основные настройки программы-экстрактора: 1) Extract Method – метод экстракции: flat – с раскрытием топологии, macro cell – без раскрытия; 2) Join Nets With Same Name – соединение сетей с одинаковыми названиями; 3) Switch Names – переключатель, устанавливается в случаях, когда требуется отключение отдельных правил экстракции; 4) Rules File – управляющий файл экстракции divaEXT.rul; 5) Rules Library – техническая библиотека.

После выполнения экстракции в рабочем каталоге появляется представление ячейки extracted, содержащее топологию с наложенной на нее электрической схемой. Топологические слои в данном файле представлены в net-формате (рис. 2.23).

Рис. 2.23. Окно экстракции приложения Diva Extactor

Для того, чтобы осуществить верификацию топологии и электрической схемы в программе Diva, необходимо вызвать процесс «Verify/LVS…» в меню редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рис. 2.24.

Основные настройки программы верификации Diva LVS: 1) Run Directory – рабочая директория процесса верификации; 2) Create Netlist – создание нетлиста: Schematic – из схемы, далее указывается ячейка схемы, extracted – из экстракта, далее указывается название экстрактированной схемы; 3) Rules File – управляющий файл верификации; 4) Rules Library – техническая библиотека; 5) LVS Options – дополнительные опции LVS: Rewiring – комбинирование симметричных сетей схемы, Device Fixing – фиксация приборов схемы, Create Cross Reference – проверка перекрещивающихся сетей, в случае нахождения таковых формируется совет о замене подключения прибора к другой сети вместо текущей, Terminals – учет при верификации расставленных терминалов.

Рис. 2.24. Окно программы верификации Diva LVS

- Кнопки: 1) Run – запуск процесса верификации; 2) Output – отчет верификации; 3) Error Display – запуск дисплея-указателя обнаруженных ошибок.

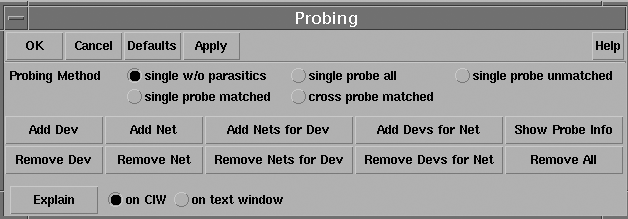

Поиск обнаруженных ошибок осуществляется с помощью приложения Diva Probing, запускаемого из меню «Verify/Probe…» (рис. 2.25).

Рис. 2.25. Окно поиска ошибок Probe

Содержимое окна Probing: 1) Probing Method – метод поиска ошибок: single w/o parasitics – выделение ошибки только в выбранном окне без паразитных элементов, single probe matched – выделение прошедших проверку сетей в выбранном окне, single probe all – выделение всех сетей в выбранном окне, cross probe matched – выделение сопоставленных сетей одновременно в окне схемы и окне экстракта, single probe unmatched – выделение ошибочных сетей в одном окне; 2) клавиши: Add Dev – подсветить прибор, Remove Dev – снять выделение прибора, Add Net – выделить сеть, Remove Net – снять выделение с сети, Add Nets for Dev – выделить сети, подключенные к прибору, Remove Nets for Dev – снять выделение с сетей, подключенных к прибору, Add Devs for Net – выделить приборы, подключенные к сети, Remove Devs for Net – снять выделение с приборов, подключенных к сети, Remove All – снять выделение со всех приборов и сетей.

Сразу после завершения работы программа Diva LVS выводит отчет о завершении процесса верификации.

Поиск ошибок происходит следующим образом. После нажатия соответствующей кнопки следует указать требуемую сеть или прибор, например, в схеме. В случае нахождения соответствия между электрической схемой и экстрактом выделится соответствующая сеть в экстракте, если же сеть не была сопоставлена, она не будет выделена. Выделяя, таким образом, входы, выходы, приборы и сети, находят среди них соответствующие друг другу. После, анализируя и сопоставляя схему и топологию, относящуюся к ошибочным сетям и приборам, находят ошибки.

Верификация в программе Assura

Запуск приложения верификации Assura LVS выполняется из меню «Assura/Run LVS» редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рис. 2.26.

Рис. 2.26. Интерфейс Assura LVS

Для работы приложения необходимо задать: название схемотехнической ячейки и библиотеку ячейки, название топологической ячейки и библиотеку ячейки, название и путь к файлу извлечения списка электрических связей (extract.rul), название и путь к файлу сравнения списков электрических связей топологии и схемы (compare.rul).

Сразу после запуска процесса верификации программа-экстрактор начинает извлечение электрической схемы из топологии. Экстракция происходит согласно правилам, определенным в файле extract.rul.

После извлечения электрической схемы из топологии автоматически запускается процесс верификации. После окончания верификации на экран будет выведен файл отчета. В случае нахождения ошибок сразу после закрытия окна отчета на экран будет выведен графический интерфейс отладки LVS Debug, показанный на рис. 2.27.

Рис. 2.27. Интерфейс отладки LVS Debug

В правой части окна указаны все ошибочные приборы, сети и терминалы. Для того, чтобы посмотреть ошибки, необходимо выбрать тип ошибок: «Rewires», «Nets», «Devices», «Pins», «Parameters», которые будут выведены, и нажать на клавишу «Open Tool». При этом на экран выводится окно ошибок выбранного типа, например, показанное на рис. 2.28.

Рис. 2.28. Окно ошибок Parameters Mismatch Tool

В верхней строке окна указаны названия ячеек (директорий) схемы и топологии. Строка ниже содержит информацию о расхождении параметров. Нижняя половина окна разбита на две части: информация о приборах топологии и информация о приборах схемы. При нахождении соответствия между приборами в топологии и схеме, но несоответствия их размеров Assura LVS указывает эти приборы и их тип в частях информации схемы и топологии. При выделении, например, прибора схемы выделяется соответствующий ему прибор топологии.

Исправив все найденные ошибки, верификацию повторяют.

Верификация в программе Calibre

Запуск приложения верификации Calibre LVS выполняется из меню «Calibre/LVS» окна редактора топологии Virtuoso. После выполнения команды на экран будет выведено окно Calibre LVS, содержащее пять вкладок.

Рис. 2.29. Вкладка Inputs программы Calibre LVS

Настройки вкладки Rules: 1) Rules – название и место расположения управляющего файла, 2) Run Directory - рабочий каталог программы.

На рис. 2.29 представлена вкладка Inputs. Настройки вкладки Input: 1) тип проверки (иерархическая, одноуровневая); 2) варианты сравнения: Layout vs Netlist – топология и нетлист, Netlist vs Netlist – нетлист и нетлист, Netlist Extraction – экстракция нетлиста; 3) закладка Layout (топология): File – имя базы данных топологии, Format – формат базы данных, Export form layout viewer – экспорт из редактора топологии, Top Cell – название головной ячейки, Layout Netlist – название нетлиста, извлеченного из топологии; 4) закладка Netlist (схема): Files – название файла нетлиста, Format – формат нетлиста, Export from schematic viewer – экспорт из редактора схемы, Top Cell – название головной ячейки.

Настройки вкладки Outputs подобны настройкам Calibre DRC.

Просмотр и исправление ошибок после окончания проверки выполняется аналогично DRC проверке в интерактивной программе Calibre RVE.