- •Введение

- •1. Программа учебной дисциплины «Проектирование цифровых устройств для 3d изделий»

- •2. Конспект лекций Лекция № 1. Методология проектирования цифровых устройств для 3d изделий

- •Лекция № 2. Описание цифрового устройства на hdl языках

- •Лекция № 3. Топологическое проектирование цифровых устройств для 3d изделий

- •Лекция № 4. Технологические правила для разработки топологии цифровых устройств

- •Лекция № 5. Трассировка межсоединений

- •Лекция № 6. Синхронизация цифровых устройств

- •Лекция № 7. Разводка питающих цепей Энергетическая оптимизация. Статический и динамический анализ питания

- •Лекция № 8. Физическая верификация топологии цифрового устройства

- •3. Методические указания по проведению вЕбинара

- •4. Контроль усвоенного материала. Тестовые вопросы

- •5. Методические указания по выполнению практических заданий Практическая работа № 1. Моделирование цифрового устройства на rtl уровне

- •Практическая работа № 2. Логический синтез цифрового устройства на основе отлаженного rtl кода

- •Практическая работа № 3. Физическая верификация топологии цифрового устройства

- •6. Методика дистанционного выполнения практических заданий

- •7. Методические указания преподавателям, ведущим занятия по дисциплине

- •8. Методические указания по самостоятельной работе слушателей

- •9. Методические указания слушателям по изучению дисциплины

- •10. Цифровые образовательные ресурсы

- •11. Вопросы самопроверки

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

Лекция № 6. Синхронизация цифровых устройств

Построение дерева синхронизации. Анализ задержек по кристаллу и «разбег фронтов». Временная характеризация. Анализ дерева синхронизации. Оптимизация задержек

Синхронизация цифровых устройств

Принцип работы цифровых устройств построен на тактировании специальным сигналом – тактовым сигналом. Переключение всех прочих сигналов осуществляется по фронтам тактового сигнала. Современные устройства, разработанные с использованием технологий субмикронного диапазона, содержат в своей структуре огромное количество элементов (десятки и сотни миллионов). Вся масса элементов должна переключаться синхронно, практически одновременно. Именно здесь и проявляется проблема тактирования, возникают паразитные эффекты, мешающие нормальной работе схемы.

Существуют различные способы построения деревьев синхронизации, различающиеся принципом их построения и функционирования. Независимо от способа реализации дерева синхронизации тактовый сигнал должен оставаться стабильным во всех частях схемы, фронт тактового сигнала должен приходить ко всем элементам схемы одновременно.

Построение дерева синхронизации. Анализ задержек по кристаллу и разбег фронтов

Расфазировка и дрожание тактовых импульсов в цифровых схемах - серьезные проблемы, способные ограничить быстродействие цифровой системы. Поэтому цепь тактовых импульсов проектируется так, чтобы влияние обоих факторов было минимальным. Особое внимание уделяется проблеме рассеяния мощности. В большинстве высокоскоростных цифровых схем основным источником рассеяния мощности является цепь разводки тактовых сигналов. Для снижения рассеяния необходимо предусмотреть возможность выключения фрагментов цепи тактовых импульсов. Подобная селекция дополнительно увеличивает неопределенность тактовой частоты.

При выборе структуры цепи тактовых импульсов доступно много степеней свободы, в том числе можно выбирать тип материалов проводников, топологию и иерархию схемы, относительные размеры проводов и буферов, время нарастания и спада, а также секционирование емкостей нагрузки.

Схемы цепей тактовых сигналов обычно включают цепь, которая применяется для доставки глобального опорного сигнала в различные части кристалла, и цепь последнего каскада, отвечающего за локальное распределение тактовых сигналов с учетом локальных колебаний нагрузки. В ряде схем распределения тактовых сигналов используется то, что абсолютная задержка распространения от центрального источника тактовых импульсов несущественна, значение имеет лишь разность фаз между двумя синхронизируемыми точками. Следовательно, одним из подходов к распределению тактовых сигналов является использование сбалансированных путей (деревьев). Наиболее распространенным типом схемы распределения тактовых импульсов является Н-дерево (рис. 2.11).

Рис. 2.11. Пример построения H-дерева синхронизации

В первую очередь тактовый сигнал подается в центр кристалла. Затем по сбалансированным путям, включающим согласованные соединения и буферы, в различные узлы-листья распространяется эталонный сигнал. В идеальном случае, если путь отлично сбалансирован, расфазировка тактовых импульсов равна нулю. Хотя на распространение сигнала от центральной точки к каждому конечному узлу может требоваться несколько тактов, на все узлы тактовые сигналы поступают одновременно. В реальности из-за разбросов процесса и условий окружающей среды в схеме возникают расфазировка и дрожание.

Конфигурация «Н-дерево» применяется в схемах, основанных на регулярных структурах, где все элементы идентичны и разводку тактового сигнала можно сделать в виде двоичного дерева. Описанную концепцию можно обобщить в согласованных RC-деревьях — в компоновочном плане, позволяющем так распространить тактовые сигналы, чтобы межсоединения, по которым проходят тактовые сигналы к функциональным субблокам, имели одинаковую длину, т.е. общий подход не предполагает наличие правильной физической структуры.

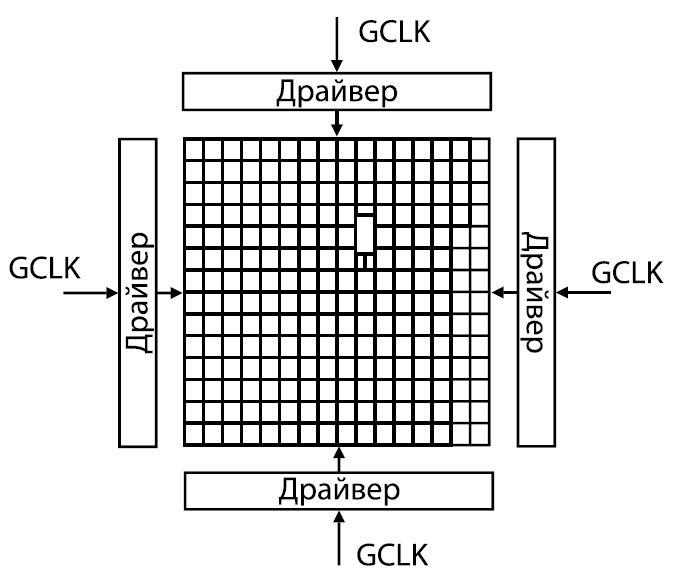

Альтернативный подход к распределению тактовых сигналов представляет сетчатая структура, показанная на рис. 2.12.

Рис. 2.12. Сетчатая структура синхронизации

Сети обычно используются в последнем каскаде цепи разводки тактовых импульсов для распределения тактовых сигналов синхронизируемым локальным нагрузкам. Данный подход полностью отличается от подхода с использованием сбалансированных RС-деревьев. Основное отличие заключается в том, что задержки оконечного усилителя, вызванные всеми нагрузками, не согласовываются. Вместо этого минимизируется абсолютная задержка в предположении, что размер сетки мал.

Основным достоинством подобной сетчатой структуры является то, что она позволяет вносить в проект изменения на более поздних стадиях разработки, поскольку тактовый сигнал легко провести в любую точку кристалла. Благодаря этому имеет место сравнительно большое рассеяние мощности, поскольку структура имеет много лишних межсоединений.

Как правило, цепь тактовой синхронизации сложных СнК проектируется в виде древовидной структуры. Но в отличие от «классических» согласованных RC-деревьев, синхронизации добиваются не выравниванием длины проводников цепи (затруднительно в сложных проектах), а согласованием задержек, возникающих при прохождении тактовых импульсов до потребителей, расположенных в различных местах кристалла. Разводчик автоматически определяет наиболее длинную цепь, и, вводя дополнительные усиливающие буферы и элементы задержки (имеются в библиотеке элементов) в более короткие цепи, добивается синхронного прихода тактовых импульсов.

Анализ связности сигналов осуществляется с использованием диаграммы, на которой строятся временные диаграммы сразу всех входных импульсов регистра состояний, включая и синхросигнал. Диаграммы строятся с учетом всех допустимых отклонений задержек входных сигналов. Если на полученном графике остается промежуток времени, в котором не происходит никаких переключений входных сигналов, то система будет работоспособной. По графику определяются необходимые времена установки и удержания входных импульсов регистра состояний. Очевидно, что период синхросигнала должен быть больше суммарного времени установки и удержания. Отношение ширины промежутка времени без переключений к периоду синхросигнала определяет устойчивость системы к помехам и внешним воздействиям. Чем выше значение этого коэффициента, тем более высокой помехоустойчивостью и запасом по быстродействию обладает схема.

Для сигналов синхронизации важно не только их одновременное воздействие на регистры состояний, но и длительности фронтов, которые не должны быть больше критической величины для выбранного типа триггеров. Для выравнивания задержек и формирования фронтов цепи синхронизации площадь кристалла или цифрового блока, занятая логическими элементами, разбивается на квадранты. Каждый квадрант снова делится на более мелкие квадранты и т.д. Корневой драйвер цепи синхронизации размещается в центре кристалла или блока. Этот драйвер управляет четырьмя драйверами второго яруса, размещенными в центрах больших квадрантов. Далее сигнал идет к драйверам третьего яруса, размещенным в центрах малых квадрантов и т.д. Необходимое число ярусов определяется сложностью схемы и нагрузочной способностью драйверов. Длины проводников в каждом ярусе по возможности выравниваются. Синхросигнал от источника доходит до каждого триггера через одинаковые элементы и линии связи, что обеспечивает минимальный разброс задержек фронтов импульсов. Описанный способ синхронизации напоминает построение H-дерева с существенно более разветвленной структурой. Корневой драйвер может располагаться как в центре, так и на периферии кристалла. В последнем случае также может быть использовано два варианта прокладки цепей: в первом случае сигнал заводится в центр кристалла и далее распределяется по младшим драйверам; во втором случае сигнал распределяется непосредственно по драйверам без завода его в центр кристалла. Однако второй вариант несколько усложняет временной анализ и может привести к увеличению разбросов по задержкам в различных частях кристалла.

Распределение тактового сигнала необходимо рассмотреть на начальных фазах разработки сложной схемы, поскольку это может повлиять на форму компоновочного плана кристалла. Если игнорировать цепь разводки тактовых сигналов на ранних фазах проекта и рассматривать ее только в конце цикла разработки, когда основная часть топологии кристалла уже зафиксирована, то будут иметь место неоптимальные цепи разводки тактовых импульсов и множество временных условий, которые снижают быстродействие конечной схемы. При внимательном планировании можно избежать многих подобных проблем, и распространение тактовых сигналов становится вполне управляемой операцией.

Анализ дерева синхронизации. Оптимизация задержек. Временная характеризация

Анализ дерева синхронизации применяется с целью выяснить возможные уровни задержек и оптимизировать топологию таким образом, чтобы задержки распространения фронтов тактового сигнала были минимальными, а отношение времени без переключений к периоду тактового сигнала стало максимальным. Для анализа задержек используются библиотечные данные, получаемые трассировщиком из двух файлов: lib-библиотеки, в которую включены данные по задержкам для каждого библиотечного элемента, и tbl-файла, содержащего таблицу задержек, представляющую собой список паразитных элементов, формирующихся в топологии при трассировке, и задержек, формируемых этими паразитными элементами.

При анализе учитывается время прихода фронта синхросигнала в каждую точку схемы. Для нормальной работы схемы все устройства, тактирующиеся синхросигналом, должны переключаться в течение положительного либо отрицательного полупериода тактового сигнала (в зависимости от принципа работы схемы). При этом для успешного захвата данных триггером они должны поступить на вход данных триггера за определенное время до прихода фронта тактового сигнала, называемого временем установления данных, и продержаться дополнительно некоторое время после окончания фронта сигнала, называемого временем удержания данных. Трассировщик анализирует все описанные выше процессы для каждого компонента схемы и оптимизирует задержки тактового сигнала с целью выполнения этих требований. Формирование задержек осуществляется с помощью встраивания в цепь синхронизации буферных элементов различной величины в зависимости от исходных данных. Тактируемые цепи, находящиеся рядом со схемой формирования тактового сигнала, требуют введения больших задержек относительно цепей, расположенных на максимальном удалении от формирователя.

Оптимизация происходит в несколько шагов, на каждом из которых оптимизатор изменяет конфигурацию дерева синхронизации, встраивает или убирает буферы задержек, улучшая общие показатели схемы по задержкам. При этом просчитываются все пути распространения тактового сигнала, и выявляется наиболее длинный и критичный путь. Таких путей может быть несколько, поэтому, как правило, данные выводятся для нескольких наихудших путей. Показателем качества оптимизации служит описанное выше значение отношения времени без переключения к периоду тактового сигнала. Данный коэффициент может быть выражен также в виде временного значения. Оптимизатор стремится сделать это значение максимальным. Программа оптимизации учитывает при проведении процесса оптимизации схемы наихудшие условия, возникающие в результате внешних воздействий и технологических отклонений, такие, как максимальные задержки элементов схемы, максимальные паразитные значения элементов трассировки и зависящие от них значения задержек.

Как было сказано выше, оптимизация выполняется в течение нескольких проходов, по окончании которых оптимизатор выдает сообщение об успешном завершении процесса либо сообщение о неудаче оптимизации. В случае неудачи заново должно быть выполнено переразмещение блоков и элементов схемы и трассировка. Дополнительно необходимо проанализировать список ограничений.

После успешного завершения трассировки и оптимизации создается список задержек, в который включаются задержки по всем элементам и цепям топологии. Список представляется в виде sdf-файла и содержит максимальные (наихудшие) значения задержек. После формирования списка осуществляется моделирование схемы, извлеченной из топологии в виде Verilog-нетлиста, с учетом выявленных задержек. При высоком уровне качества характеризации библиотеки точность результатов моделирования, как функциональных характеристик, так и электрических параметров схемы очень высока, что означает практически полное соответствие модели реальной схеме по перечисленным параметрам.

Описание работы топологии с помощью файла задержек, определение временных и электрических зависимостей по входам схемы называется временной характеризацией. При использовании разработанной топологии в качестве CФ-блока трассировщик и оптимизатор будут использовать заданные значения для формирования цепей питания, синхронизации, анализа и оптимизации топологии более высокого порядка, т.е. данный блок используется как обычный конструктивный библиотечный элемент, имеющий индивидуальный технологический lef-файл.