- •Введение

- •1. Программа учебной дисциплины «Проектирование цифровых устройств для 3d изделий»

- •2. Конспект лекций Лекция № 1. Методология проектирования цифровых устройств для 3d изделий

- •Лекция № 2. Описание цифрового устройства на hdl языках

- •Лекция № 3. Топологическое проектирование цифровых устройств для 3d изделий

- •Лекция № 4. Технологические правила для разработки топологии цифровых устройств

- •Лекция № 5. Трассировка межсоединений

- •Лекция № 6. Синхронизация цифровых устройств

- •Лекция № 7. Разводка питающих цепей Энергетическая оптимизация. Статический и динамический анализ питания

- •Лекция № 8. Физическая верификация топологии цифрового устройства

- •3. Методические указания по проведению вЕбинара

- •4. Контроль усвоенного материала. Тестовые вопросы

- •5. Методические указания по выполнению практических заданий Практическая работа № 1. Моделирование цифрового устройства на rtl уровне

- •Практическая работа № 2. Логический синтез цифрового устройства на основе отлаженного rtl кода

- •Практическая работа № 3. Физическая верификация топологии цифрового устройства

- •6. Методика дистанционного выполнения практических заданий

- •7. Методические указания преподавателям, ведущим занятия по дисциплине

- •8. Методические указания по самостоятельной работе слушателей

- •9. Методические указания слушателям по изучению дисциплины

- •10. Цифровые образовательные ресурсы

- •11. Вопросы самопроверки

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

Лекция № 2. Описание цифрового устройства на hdl языках

Стили описания, RTL-уровень. Моделирование цифровых устройств. Создание тестового окружения. Логический синтез электрической схемы

Языки описания аппаратуры (HDL – Hardware Description Language) являются языками высокого уровня, которые позволяют создавать модели электронных устройств. В настоящее время распространены два основных языка – VHDL и Verilog.

VHDL (Very High Speed Integrated Circuit Hardware Description Language – язык описания сверхскоростных ИС) был разработан в начале 80-х годов по заданию Министерства обороны США [3]. VHDL строго типизирован и синтаксически напоминает язык Pascal.

Язык Verilog был разработан в 1985 году фирмой Gateway Design Automaton, позднее поглощенной Cadence. Verilog базируется на языке C, не имеет возможности создания новых типов данных, но зато более прост в реализации и лаконичен, что позволяет уменьшить объем описания схем примерно в полтора раза по сравнению с VHDL.

Язык Verilog

Язык Verilog поддерживает три основных уровня абстракции: поведенческий, RTL-уровень (Register Transfer Level – уровень межрегистровых передач) и структурный. Поведенческий уровень описывает функционирование системы в целом без учета внутренней архитектуры. На RTL-уровне поведение схемы определяется в терминах потока данных между регистрами и логических операций над данными (комбинаторная логика). На структурном уровне проект представляется в виде иерархии компонентов. Рис. 2.3 иллюстрирует различные уровни абстракции.

а) б) в)

Рис. 2.3. Уровни абстракции: а) поведенческий; б) RTL-уровень;

в) структурный

Основной структурной единицей проекта на языке Verilog является модуль. Он описывается ключевыми словами module - endmodule, что соответствует entity - end в VHDL. Как правило, модуль содержит список портов — интерфейсных сигналов, которые служат для подключения его к другим модулям. Порты бывают трех типов: input - входы, output - выходы, inout - двунаправленные. Ниже приведен общий синтаксис модуля.

module имя_модуля [список портов];

[output // выходы

inout // двунаправленные порты

input] // входы

// Тело модуля

initial

begin

..

end

always

..

endmodule

Символами // обозначается однострочный комментарий. Verilog также поддерживает многострочный комментарий /* */.

В модуле используются процедурные блоки initial и always. Initial служит для описания действий, которые выполняются один раз (например, при запуске модели), а always обозначает действия, которые выполняются многократно, на протяжении всего времени. Средства синтеза не понимают блок initial. Ключевые слова begin – end служат для объединения последовательно выполняемых операторов в единый с точки зрения синтаксиса оператор (аналогично begin – end в языке Pascal или {} в C). В противоположность последовательному блоку begin – end блок fork – join объединяет параллельные операторы. Значения задержек в нем отсчитываются не относительно предыдущего оператора, а относительно начала блока.

Типы данных

Для моделирования аппаратных средств Verilog поддерживает 4-хзначную логику: 0, 1, z, x. Первые два значения соответствуют логическим уровням, третье – состоянию с высоким импедансом, четвертое означает неопределенное состояние и используется при моделировании неинициализированных сигналов, конфликтов, метастабильных состояний триггеров - во всех случаях, когда симулятор не может определить значение данного сигнала. В реальном приборе такого значения не бывает.

Все типы данных в языке Verilog можно разделить на две основных группы: переменные и цепи. Цепь представляет собой физическое соединение вентилей. Она не сохраняет данные (за исключением trireg): ее значение определяется непрерывным присваиванием (драйвером). Фактически цепь моделирует проводник, который переходит в третье состояние при отключении драйвера. Помимо упомянутой trireg к цепям относятся wire, wand, wor, supply1, supply0. Самой распространенной является wire.

Примеры:

wire net1; // для обычного межсоединения

wor a; // трактует соединение проводников по логике ИЛИ

wand b; // трактует соединение проводников по логике И

trireg c; // хранит последнее значение драйвера

В отличие от цепей переменные сохраняют значение до следующего присваивания. Verilog поддерживает следующие типы переменных:

- reg – беззнаковая переменная (до явного указания signed), самый распространенный тип;

- integer – 32-разрядная переменная со знаком;

- real, realtime – вещественные переменные двойной точности;

- time – 64-разрядная беззнаковая переменная, используется для сохранения времени моделирования.

Переменные reg, time и integer по умолчанию имеют неопределенное значение x, real и realtime – 0.0. Входы и двунаправленные порты модуля должны иметь тип wire, а выходы могут быть как wire, так и reg [2].

Wire и reg могут быть векторными величинами:

- reg [7:0] word; // 8-разрядный регистр, reg[7] - СЗР, reg[0] – МЗР;

- wire [0:4] ack; // 5-разрядная цепь, wire[0] – СЗР, wire[4] - МЗР.

Предпочтительнее задавать векторы в виде [СЗР:МЗР], старший значащий разряд располагать слева.

Цепь управляется непрерывным (continuous) присваиванием, которое задается вне процедурных блоков с помощью ключевого слова assign:

assign d = a & b & c; // d = abc.

Параметры

При описании цифровых схем возникает необходимость задания констант, определяющих какие-либо фиксированные параметры: задержки, разрядность шин. Но в то же время при различных включениях одного и того же модуля в модули верхнего уровня данные константы должны иметь возможность изменяться. Verilog позволяет сделать это с помощью параметров:

module param_example(bus_out, bus_in);

..

parameter bus_width = 32;

wire [width - 1:0] bus_out;

..

endmodule

При подстановке экземпляра модуля параметр можно изменить:

- param_example I1(bus_out, bus_in); // будут использованы значения по умолчанию;

- param_example #(16) I2(bus_out, bus_in); // 16-разрядная шина.

Временной и событийный контроль

Так как Verilog используется для моделирования физических систем, то большое внимание уделено привязке события к определенному моменту времени. Для этого используется механизм задержек. Конструкция # позволяет приостановить исполнение оператора на заданное время. Например, выражение #10 a = b присвоит переменной a значение b спустя 10 временных единиц. Вместо числа могут использоваться параметры, например, при задании тактового сигнала:

parameter real period = 10.0;

..

always @(posedge clk)

#(period / 2) clk = ~ clk;

Конструкция @ (список чувствительности) представляет собой событийный контроль, который задерживает исполнение последующих операторов до тех пор, пока не произойдет событие из списка чувствительности. В качестве событий могут использоваться изменения сигналов – цепей и переменных, положительный (posedge) или отрицательный (negedge) фронт сигнала. В случае использования фронтов сигнал должен быть одноразрядным. Список чувствительности также может содержать особый тип данных event – так называемое именованное событие (named event), срабатывание которого можно задать явно с использованием оператора ->. Использование event в блоках always или параллельных блоках fork - join позволяет эффективно управлять порядком исполнения операторов:

event data_transmitted; // объявление именованного события

always ..

begin

..

-> data_transmitted; // явное срабатывание события

end

always @( data_transmitted); // ожидание срабатывания

..

Оператор wait (expression) позволяет задержать исполнение последующих операторов, пока выражение expression не станет истинным. Если выражение уже истинно, то сразу выполняется следующий оператор.

Конструкции event и wait не поддерживаются средствами синтеза.

Поведенческое моделирование

Для описания устройства на высоком уровне абстракции Verilog предоставляет следующие поведенческие конструкции: условный оператор if-else, оператор выбора case и его разновидности, циклы for, forever, repeat, while.

Операторы if-else и for работают так же, как и в других языках программирования (в языке C). Оператор case (expression) позволяет сделать выбор из нескольких вариантов:

case (sel)

3: y = d;

2: y = c;

1: y = b;

default: y = a;

endcase // sel

Если ни одно из условий не совпадает, выполняется ветвь default. Рекомендуется всегда использовать default для обработки непредвиденных значений.

Цикл forever выполняется на протяжении всего времени моделирования, если не задан список чувствительности:

forever @(interrupt_event); // реагирует на каждое событие interrupt_event.

Цикл repeat исполняет следующий оператор заданное число раз:

repeat (10) @(posedge clk); // ожидаем в течение 10 периодов сигнала clk

Цикл while (expression) выполняет последующий оператор до тех пор, пока выражение expression истинно. Если выражение ложно изначально, то цикл не выполняется ни разу:

while (a > 0)

a <= a – 1;.

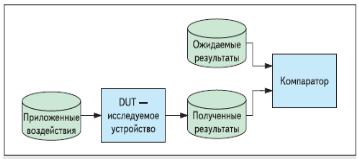

После написания RTL-кода устройства его необходимо проверить. Для верификации модели создается тестовое окружение (testbench) – это модуль верхнего уровня, в котором на испытываемое устройство (DUT – device under test или DUV – device under verification) подаются входные воздействия и проверяется реакция на эти воздействия на выходах. Обобщенная модель тестового окружения представлена на рис. 2.4.

Рис. 2.4. Обобщенная модель тестового окружения

В тестовом окружении можно использовать несинтезируемые конструкции: initial, wait, event и т. д.

Моделирование исходных файлов осуществляется с помощью симулятора. Заслуженной популярностью пользуются симуляторы фирмы Cadence - Verilog-XL и NC-Verilog. Оба являются событийными (event-based), то есть проводят вычисления только при изменении состояния схемы.

При моделировании проекта симулятор выполняет следующие шаги: 1) компиляция - симулятор считывает Verilog-описание, обрабатывает директивы и строит иерархию проекта. Этот шаг иногда разделяется на два этапа: собственно компиляцию и проработку (elaboration); 2) инициализация - на этом этапе инициализируются параметры модуля, соответствующие переменные (reg, time и integer) устанавливаются в неизвестное состояние, а неуправляемые цепи – в третье состояние; 3) симуляция - симулятор обрабатывает все события, расписанные на текущий момент времени моделирования, затем увеличивает время (второй параметр директивы `timescale) и продолжает вычисления. Моделирование останавливается, когда в очереди больше нет событий.

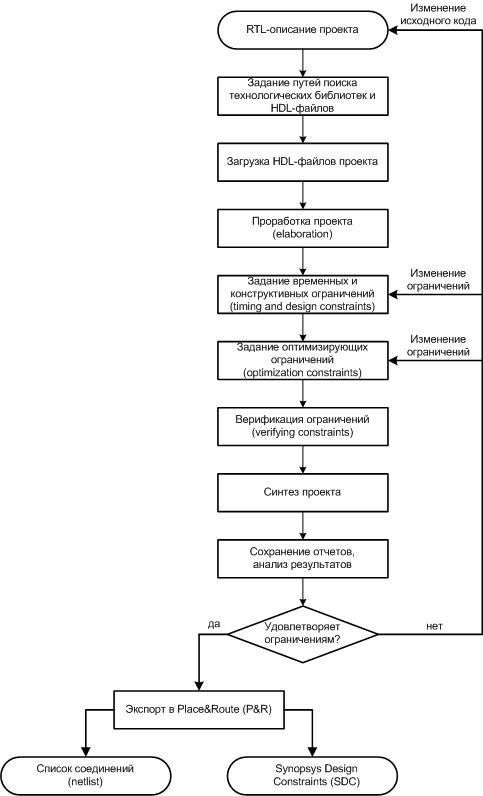

Рис. 2.5. Маршрут синтеза в инструменте RTL Compiler

Следующим этапом после написания и отладки проекта является логический синтез - процесс автоматизированного создания логической схемы на базе RTL-описания и библиотек элементов логического уровня от производителя СБИС. Здесь самыми известными продуктами являются RTL Compiler фирмы Cadence и Synopsys Design Compiler. Маршрут синтеза в инструменте RTL Compiler представлен на рис. 2.5.

Результатом логического синтеза является список соединений (netlist) – описание проекта в базовых элементах выбранной технологической библиотеки. Верификацию списка соединений проводят с использованием того же тестового окружения.