- •Введение

- •1. Программа учебной дисциплины «Проектирование цифровых устройств для 3d изделий»

- •2. Конспект лекций Лекция № 1. Методология проектирования цифровых устройств для 3d изделий

- •Лекция № 2. Описание цифрового устройства на hdl языках

- •Лекция № 3. Топологическое проектирование цифровых устройств для 3d изделий

- •Лекция № 4. Технологические правила для разработки топологии цифровых устройств

- •Лекция № 5. Трассировка межсоединений

- •Лекция № 6. Синхронизация цифровых устройств

- •Лекция № 7. Разводка питающих цепей Энергетическая оптимизация. Статический и динамический анализ питания

- •Лекция № 8. Физическая верификация топологии цифрового устройства

- •3. Методические указания по проведению вЕбинара

- •4. Контроль усвоенного материала. Тестовые вопросы

- •5. Методические указания по выполнению практических заданий Практическая работа № 1. Моделирование цифрового устройства на rtl уровне

- •Практическая работа № 2. Логический синтез цифрового устройства на основе отлаженного rtl кода

- •Практическая работа № 3. Физическая верификация топологии цифрового устройства

- •6. Методика дистанционного выполнения практических заданий

- •7. Методические указания преподавателям, ведущим занятия по дисциплине

- •8. Методические указания по самостоятельной работе слушателей

- •9. Методические указания слушателям по изучению дисциплины

- •10. Цифровые образовательные ресурсы

- •11. Вопросы самопроверки

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

Лекция № 4. Технологические правила для разработки топологии цифровых устройств

Классификация правил, состав, структура и физический (топологический) смысл. Правила для примитивов. Правила для блоков ввода/вывода, учет защиты от статического разряда. Правила для контактных площадок

Целью топологического проектирования является получение рабочей топологии устройства, обеспечивающей функциональные характеристики в диапазоне заданных условий (частота, температура и др.) и электрические параметры в соответствии с техническим заданием (напряжения, токи, нагрузочная способность и др.). Для получения качественных технических и функциональных характеристик требуется строгое соблюдение правил проектирования топологии.

Технологические правила для разработки топологии цифровых устройств. Классификация правил, состав и структура

Проектирование топологии цифровых устройств может осуществляться как в ручном, так и автоматизированном режиме. Но в обоих случаях разработанная топология должна соответствовать требованиям норм конструкторско-технологических требований. Однако есть и отличия между требованиями, предъявляемыми к топологии цифровых ячеек для ручного проектирования и для автоматического синтеза.

Технологические правила разработки топологии состоят из требований к внутрислойному проектированию (зазор, расстояние, ширина, длина) и межслойным нормам (наложение, расстояние, пересечение, выход одного слоя за габариты другого).

Структура правил:

- нормы для каждого слоя;

- нормы для группы слоев;

- нормы для приборов (транзисторы, диоды, емкости и др.);

- нормы для специальных образований, как например, контактная площадка, периферийное кольцо, метки совмещения шаблона и др.

Кроме требований к конфигурации топологических слоев предъявляются также дополнительные требования:

- минимальные/максимальные габариты прибора;

- минимальные/максимальные значения номиналов.

Топология, спроектированная с учетом требований КТТ, проверяется с помощью управляющего файла DRC проверки.

Правила для примитивов

В общий состав слоев добавляется дополнительный слой, необходимый синтезатору топологии для определения габаритов ячеек – это слой «boundary». Данный слой содержит любая библиотечная ячейка. Габариты слоя являются определяющими при размещении библиотечных ячеек и блока. Обычно габариты слоя полностью перекрывают топологию ячейки, но в некоторых случаях структуры ячейки могут выходить за габариты «boundary».

Существует градация ячеек по размеру, которая характеризуется кратностью к самой минимальной по габаритам ячейке. Высота любой ячейки библиотеки одинакова, варьируется лишь ширина. При этом определяется минимальная ширина ячейки, которая затем может умножаться на коэффициент два, три, четыре и т.д. Очень важно при самостоятельном проектировании библиотечного элемента соблюдать описанную закономерность.

Библиотечные элементы, используемые для синтеза, должны быть разработаны с применением не более одного – двух металлов. Наличие большего количества металлов в базовых ячейках существенно усложняет работу трассировщика топологии и может привести к многочисленным ошибкам трассировки или невозможности осуществления трассировки.

Правила для блоков ввода вывода, электростатическая защита

Все блоки ввода вывода обычно максимально удаляются от остальных частей схемы, это связано с наличием мощных переключающихся каскадов в топологической структуре блоков, способных навести существенные помехи на остальную часть схемы. Кроме того, каждый блок ввода/вывода должен быть обеспечен электростатической защитой.

Электростатические разряды – одна из основных причин отказов интегральных схем. Заряды возникают в результате явлений, приводящих к появлению разностей электрических потенциалов между отдельными элементами оборудования, которые соприкасаются со схемами, между человеком и изделием или оборудованием и т.п. Внезапные разряды приводят к протеканию импульсов токов, как правило, очень коротких по времени, но имеющих большую амплитуду и способных полностью или частично повредить внутреннюю структуру схемы.

Повышение быстродействия, снижение потребляемой мощности, уменьшение геометрических разрядов элементов полупроводниковых схем делают их еще более чувствительными к воздействию электрических полей и в особенности электростатического разряда.

Базовый принцип защиты схемы от воздействия электростатического заряда основан на замыкании выводов схемы, как сигнальных, так и питающих, между собой в момент возникновения разряда. При этом часть заряда рассеивается на входных резисторах цепей. Идеальная защита достигается, если сопротивление замыкающих элементов во включенном состоянии и время их включения равны нулю. В качестве таких шунтов применяются различные приборы: диоды, транзисторы и более сложные схемы.

Важное требование к защитным структурам – не ухудшать параметры защищаемой схемы. Кроме того, они должны иметь, по возможности, меньшую площадь, шунтировать напряжение и токи перегрузки, возникающие при электростатическом разряде, иметь максимально быстрое время отклика (срабатывания) и вносить минимальное время задержки в нормальную работу схемы.

Для современных КМОП технологий нижняя граница разрушающего потенциала составляет около 7 В, при преодолении ее начинаются необратимые разрушительные процессы.

При разработке цифровых устройств для 3D изделий применение электростатической защиты является обязательным при проектировании любой схемы, входящей в состав 3D сборки, т.к. незащищенная схема может стать причиной выхода из строя других комплектующих сборки.

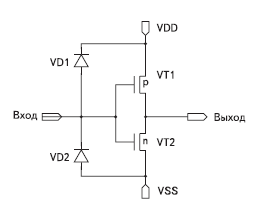

На рис. 2.7 представлена типовая схема защиты входных и выходных каскадов цифровых схем.

Рис. 2.7. Типовая защита стандартных выводов цифровой схемы

В качестве элементов защиты в этой схеме выступают диоды VD1 и VD2.

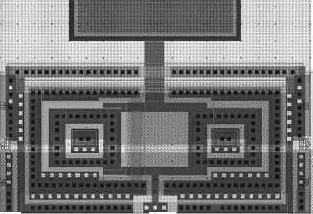

Ниже на рис. 2.8 представлен вариант топологии вывода с защитными диодами. На рисунке они выглядят как концентрические кольцевые структуры и размещены рядом с контактной площадкой.

Рис. 2.8. Пример топологии защитных входных структур

Более сложные схемы защиты детектируют электростатический разряд на периферийных шинах питания и земли и замыкают их между собой. Это так называемые Clamp-структуры. В качестве детектора электростатического разряда и элемента, запускающего включение схемы защиты, выступает емкость. При превышении порога напряжения мощный выходной транзистор открывается, замыкая при этом выводы питания и земли. Замыкание шин между собой приводит к уменьшению разности потенциалов между выводами схемы. Также эта схема работает и при превышении напряжения питания. Для надежной защиты схемы ячейки электростатической защиты располагаются по периферии кристалла с определенным шагом, а также в углах кристалла. Все ячейки защиты связываются сигнальной линией. При наличии управляющего сигнала на выходе одной из ячеек все остальные ячейки переходят в активный режим, замыкая выводы.

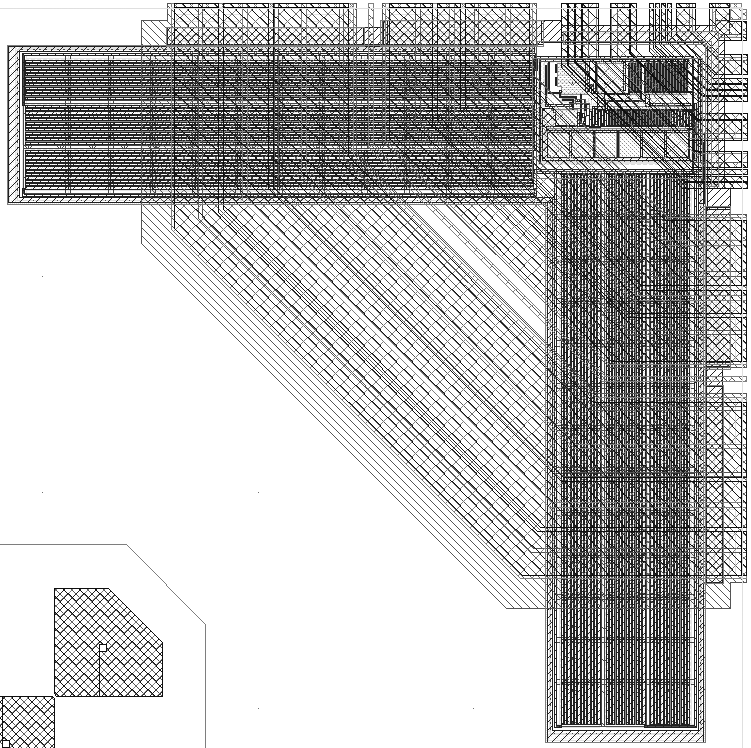

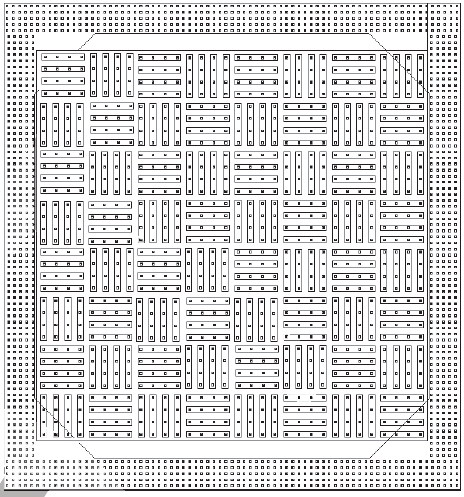

На рис. 2.9 представлен вариант топологии защитной Clamp-структуры. Это угловой вариант, располагается под периферийными шинами питания и земли. Вытянутые в горизонтальном и вертикальном направлениях структуры являются мощными транзисторами, замыкающими шины питания и земли. Данная ячейка защищает схему от статического разряда до 4 киловольт, а также включается и при обычном кратковременном повышении напряжения питания.

Рис. 2.9. Топология защитной Clamp-ячейки

Данная топология спроектирована с учетом технологических норм 90 нм технологии.

Правила для контактных площадок

Проектирование контактных площадок является ответственной частью работы по созданию топологии схемы, что связано с требованиями по помехоустойчивости проектируемой схемы, требованиями к конструкции для процесса разварки и многими другими факторами.

Использование схем в 3D конструкциях предопределяет расположение контактных площадок на площади кристалла. В этом случае возможны два типа расположения площадок:

- по периферии кристалла;

- в любом месте кристалла.

Контактные площадки, расположенные по периферии кристалла, обеспечивают разварку кристалла к стандартным выводам микросхемы металлическими траверсами.

Контактные площадки, расположенные внутри кристалла, позволяют создавать «этажерки» из кристаллов путем создания вертикальных соединений.

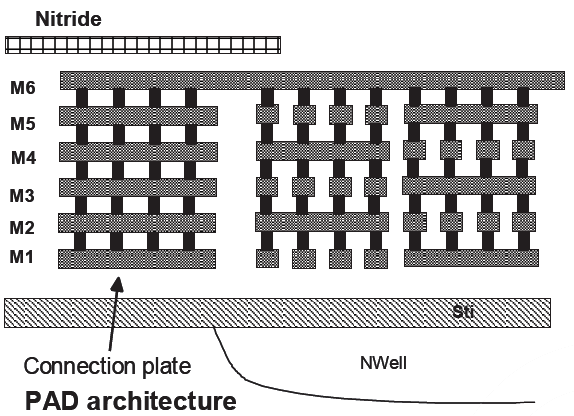

Конструкции представленных типов площадок должны соответствовать требованиям технологических норм проектирования. На рис. 2.10 представлена конструкция контактной площадки, выполненной по нормам 130 нм с применением шести металлов. Под контактной площадкой расположен n-карман для уменьшения влияния подложки.

Рис. 2.10. Конструкция контактной площадки

Конструкция представленной площадки обеспечивает хорошую изоляцию от влияния шумов подложки и надежное межслойное контактирование.