6.Тригери Лабораторна робота №5

Мета роботи: вивчити принцип роботи тригерів.

6.1.Короткі теоретичні відомості

6.1.1.Тригери – це комп’ютерні вузли пам’яті з двома стійкими станами - лог. 0 або лог. 1, які визначаються за рівнем логічного сигналу на їхньому виході, тобто тригери можуть зберігати один двійковий розряд (біт) інформації і представляють собою елементарний вузол (елемент) комп’ютерної пам’яті.

Існує цілий ряд різновидів тригерів, які відрізняються між собою схемою побудови і функціональністю, це, зокрема,

RS-тригери, D-тригери, лічильні Т-тригери, JK-тригери та інші. Спільною основою побудови всіх тригерів є наявність в них найпростішого тригера - RS-тригера.

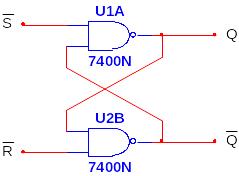

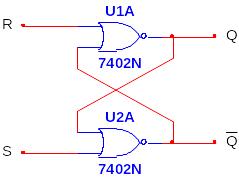

На рис.6.1. показані варіанти

схеми побудови RS-тригера,

їхні таблиці істинності та його умовне

графічне позначення : а) на елементах

2І-НЕ, b)

на елементах 2АБО-НЕ,

-стан тригера в моменти часу до зміни

вхідних сигналів,

-стан тригера в моменти часу до зміни

вхідних сигналів,

- стан тригера після зміни вхідних

сигналів.

- стан тригера після зміни вхідних

сигналів.

S |

R |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

x |

1 |

1 |

1 |

x |

S |

T |

|

|

|

|

R |

|

a)

S |

R |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

x |

1 |

1 |

1 |

x |

b)

Рис.6.1.

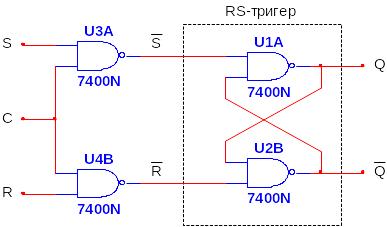

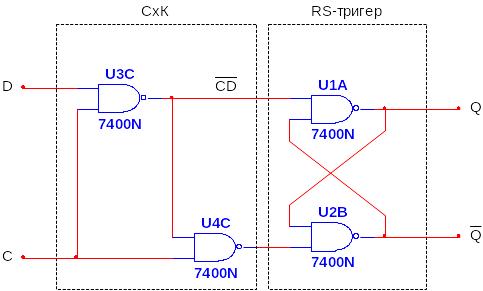

Усі інші тригери складаються із RS-тригера, як елемента пам’яті (ЕП), та деякої схеми керування (СхК), як показано на узагальненій схемі на рис.6.2.

Рис.6.2.

Тригери є основою побудови багаторозрядних базових функціональних вузлів комп'ютерів з пам’яттю, зокрема, регістрів, лічильників, накопичувальних суматорів.

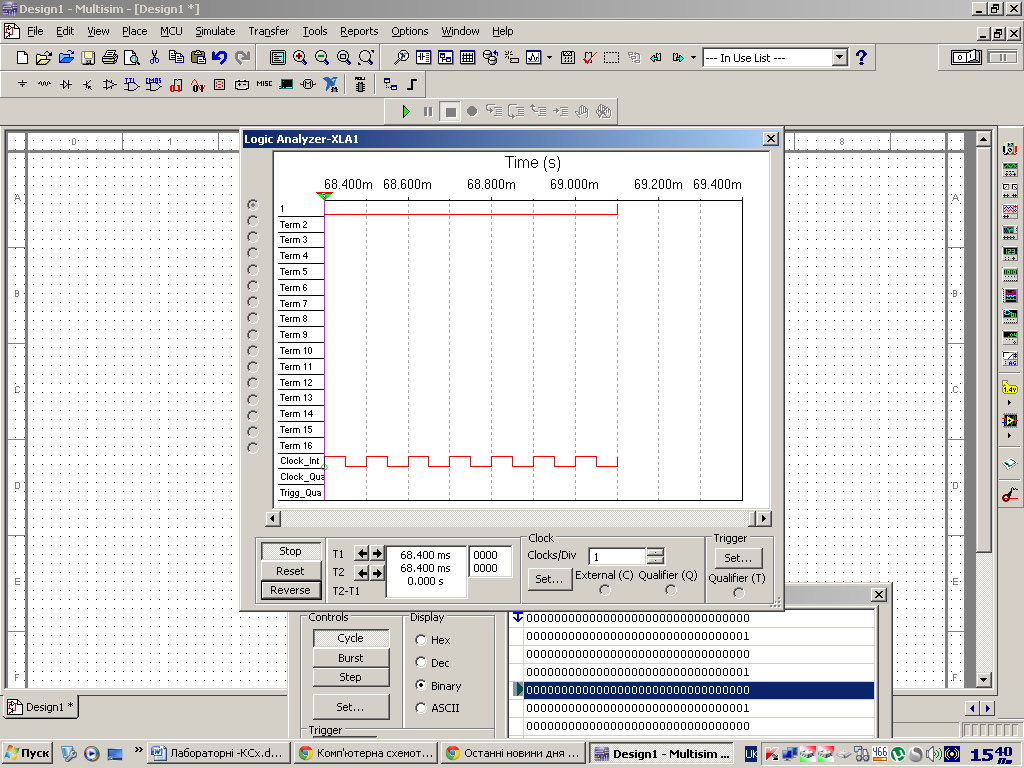

6.1.2.Синхронний RS–тригер. Для часової синхронізації реакції тригера на дію вхідних R і S сигналів із зовнішнім синхронізуючим сигналом С використовуються тригери зі схемою побудови як показано на рис.6.3. Як правило, синхросигнал С –це меандровий сигнал, як на рис.6.3b, при цьому тригер може змінювати свій стан лише тоді, коли сигнал С приймає значення логічної 1. Тому цей сигнал ще називають стробуючим.

СхК

b)

Рис.6.3

6.1.3.D–тригер. Функцією D–тригера є запам’ятовування на його виході стану вхідного логічного сигналу на D–вході на інтервалі часу дії логічної 1 на синхронізуючому С-вході, при цьому на інтервалі часу дії логічного 0 на С-вході, стан тригера «заморожується». Приклад схеми D-тригера, його таблиці істинності і умовне графічне позначення показано на рис. 6.4.

D |

Т |

Q |

|

|

|

C |

|

D |

C |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Рис.6.4

6.1.4.Лічильний тригер (Т-тригер). Це D-тригер, в якому замість сигналу D на вхід подається сигнал . Тепер, при кожній зміні синхросигналу C із логічного 0 в логічну 1 стан тригера змінюється на протилежний. Зауважимо, що стан D-тригера на інтервалах часу, коли сигнал С дорівнює логічній 1 тотожний сигналу D із невеликою затримкою, тобто зміни сигналу D призводять до синхронної зміни стану D-тригера.

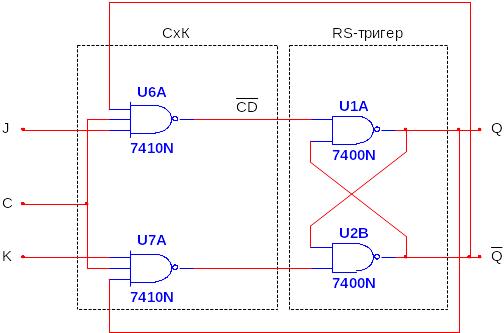

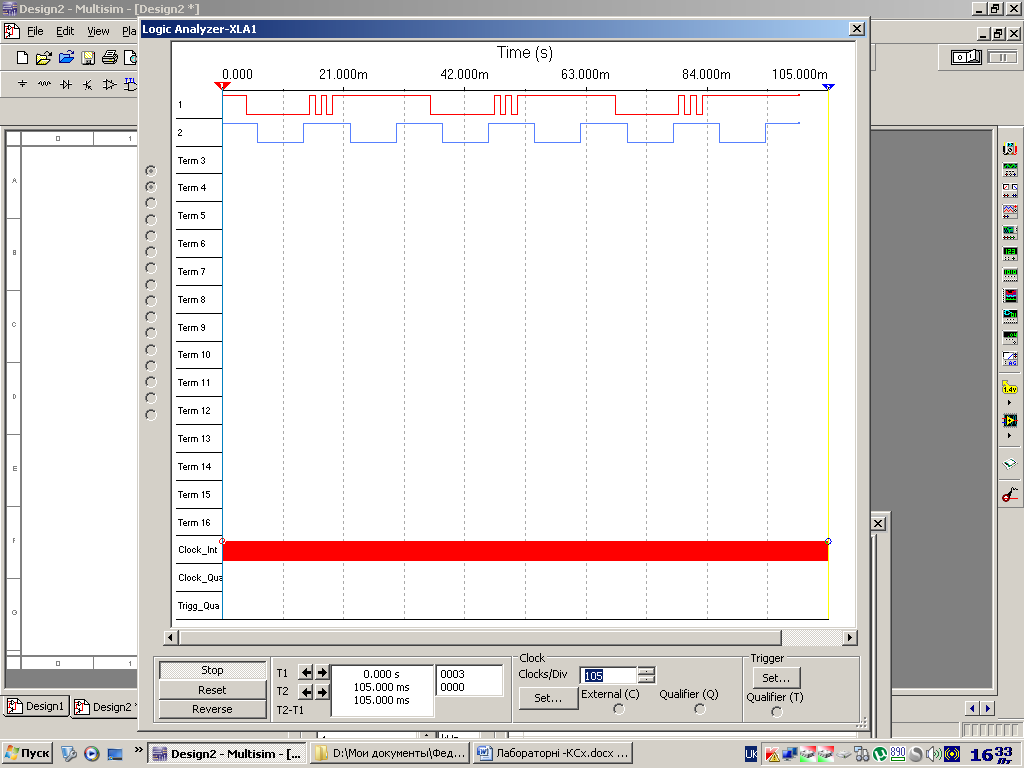

6.1.5.JK-тригер. Це універсальний тип тригера: на цьому типі тригері можна реалізувати будь який інший із розглянутих вище типів тригерів. На рис. 6.5 показаний приклад схеми JK-тригера, його таблиця істинності та умовне графічне позначення.

С |

J |

K |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

J |

T |

|

C |

|

|

K |

|

Рис.6.5

6.1.6. Динамічні тригери. Всі вище розглянуті типи тригерів відносяться до так званих статичних тригерів. Недоліком статичних тригерів, наприклад, D-тригера, є чутливість їхнього стану до короткочасних перехідних «тремтінь» інформаційного сигналу при його зміні із 0 в 1 або навпаки із 1 в 0, на інтервалах часу, коли синхросигнал С знаходиться в стані логічної 1 як це показано на рис.6.6.

С

D

Рис.6.6.

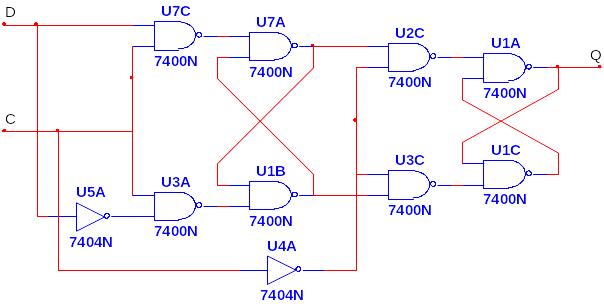

Найпростіша схема динамічного D-тригера показана на рис.6.7.

Рис.6.7

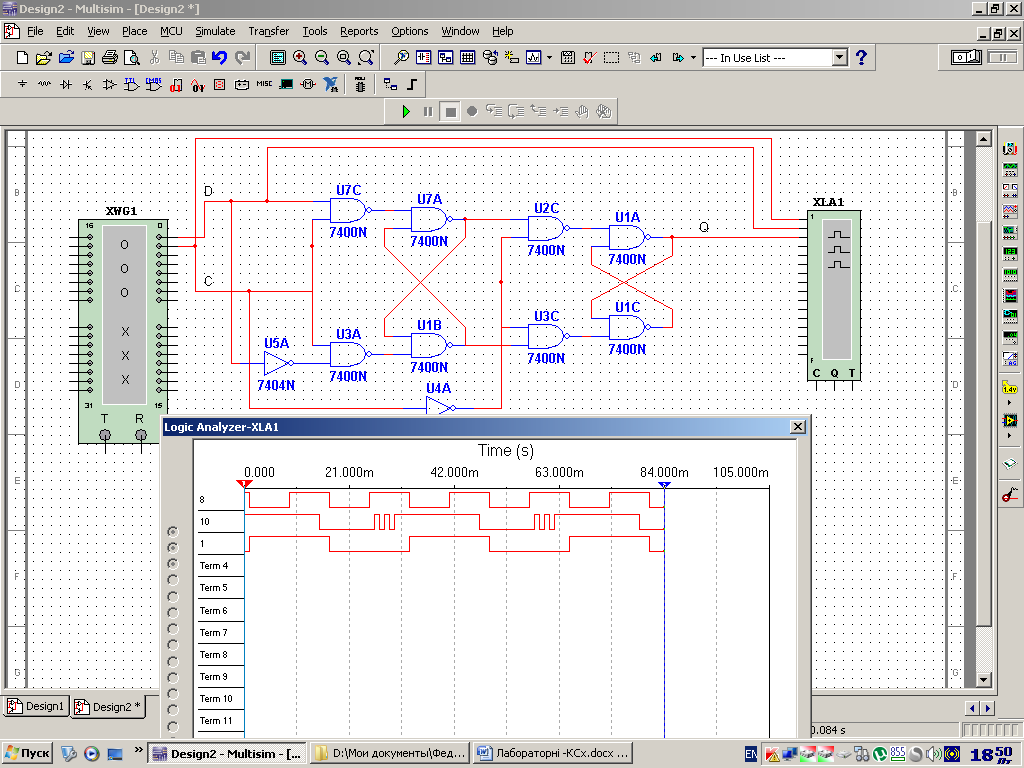

Даний D -тригер складається із двох асинхронних статичних RS-тригерів: вихідного (на елементах U1A i U1C) та вхідного (на елементах U7A i U1B) та додаткової логіки. При відсутності додаткового вхідного тригера, вихідний стан тригера повторював би вхідний інформаційний сигнал D на час дії високого рівня синхросигналу С. Роль додаткового RS-тригера в проміжковому запам’ятовуванні інформаційного сигналу D з подальшою установкою вихідного тригера по спаду синхросигналу С вихідним сигналом додаткового вхідного тригера. Часові діаграми роботи динамічного D –тригера рис.6.7 показані на рис.6.8.

С

D

Q

Рис.6.8

Як видно із цих діаграм, стан тригера змінюється по спаду сигналу С.

Аналогічно, може бути синтезована схема динамічного JK-тригера, загальна схема і умовне графічне позначення якого показано на рис.6.9.

Рис.6.9