Вх2

Вх2Логическое устройство

t

Вых

t

а

ВхA1

t

t

t

t

ВхA2

t

ВхA1

ВхA2

ВхB1

ВхB2

Вых1

Вых2

ВхB2

ВхB1

Логическое устройство

t

ВхB2

t

t

t

Вых1

Вых2

б

а – последовательное

логическое устройство и диаграммы его

работы, б – параллельное логическое

устройство и диаграммы его работы

Рисунок 3.1 –

Последовательное и параллельное

логические устройства

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Для потенциального способа (используются напряжения двух уровней условно принятых за уровень «логического нуля» и «логической единицы» - см. раздел 1.1) среди элементарных логических устройств по функциональным особенностям (реализуемой функции) можно выделить следующие элементы:

- элемент ИЛИ (логическое сложение - Увых= Х1 + Х2 + … +Хn);

- элемент И (логическое умножение - Увых= Х1 ∙ Х2 ∙ … ∙Хn);

- элемент НЕ

(логическоя отрицание, инверсия -

![]() );

);

- повторитель (Увых= Х).

Обозначение на принципиальных схемах элементов, реализующих выше представленные функции, приведено на рисунке 4.1.

1

1

&

Х1

Х2

У

У

Х1

У

«ИЛИ»

1

У

Х

Х2

«И»

«НЕ»

Рисунок 4.1 –

Простейшие логические элементы

4.1 Основные параметры логический элементов

Наиболее часто в цифровой технике используются следующие характеристики логических элементов:

- коэффициент объединения по входу;

- нагрузочная способность;

- быстродействие;

- помехоустойчивость.

Коэффициент объединения по входу определяет число входов элемента способных принимать логические переменные. Этот параметр характеризует потенциальные возможности: чем он больше, тем шире функциональная характеристика элемента.

Нагрузочная способность (коэффициент разветвления по выходу) говорит о числе логических входов (однотипных), на которые одновременно (параллельно) может подаваться выходной сигнал. От нагрузочной способности зависит число элементов, входящих в законченное цифровой устройство.

Быстродействие можно отнести к важнейшим показателям функционирования логического элемента. Этот параметр зависит от времени задержки передачи сигнала с входа на выход. Иными словами, быстродействие определяется временем между изменением сигнала на входе до появления функционально соответствующих изменений выходного логического сигнала. Задержка сигнала с учетом параметров формы импульса (см. рисунок 1.2) в полной мере связана с соотношением tИ , tФ и tС. Чем больше tФ и tС , тем ниже быстродействие. Время задержки рассчитывается по справочным характеристикам. На рисунке 4.2 представлены идеализированный пример формы входного и выходного сигналов обычного инвертора.

t

t

tЗ1,0

tЗ0,1

Рисунок 4.2 –

Параметры задержки импульсных элементов

tЗ1,0 – время задержки переключения элемента из состояния лог.1 в состояние лог.0.

tЗ0,1– время задержки переключения элемента из состояния лог.0 в состояние лог.1.

Среднее время

задержки определяется как

![]()

Среднее время задержки используется при расчете суммарного времени распространения сигналов в сложных цифровых схемах.

Помехоустойчивость – есть максимальное значение внешнего фактора, не вызывающего нарушения работы логического элемента в статическом режиме.

U1

U0вых

Uвх

U0п

U1п

U1вых

Рисунок 4.3 –

Диапазон помехоустойчивости дискретного

элемента

На рисунке 4.3 изображена форма зависимости выходного сигнала инверсного логического устройства от уровня входного напряжения. В статическом режиме при увеличении Uвх до U0п выходное напряжение незначительно падает. В интервале U0п < Uвх < U1п выходной сигнал резко меняет свою амплитуду U1вых < Uвых < U0вых.

Таким образом, амплитуда помехи, не приводящая к изменению статического состояния элемента без изменения входной информационной составляющей (например, при короткозамкнутых входных цепях) называется предельной.

Помехозащищенность характеризуется предельной амплитудой помехи.

4.2 Диодные ключи

Импульсные сигналы получают путем коммутации электрических цепей. При этом в качестве коммутирующих электронных элементов применяют:

- диоды;

- биполярные транзисторы;

- полевые транзисторы.

Основное достоинство диодных матриц – их простота – при интегральной технологии не дает никаких преимуществ. На практике подобные схемные решения применяют при использовании навесного монтажа РЭА и в случае вынужденной замены вышедших из строя простейших логических элементов.

На рисунке 4.4 изображен диодный логический элемент, реализующий функцию «И». Разрядный разомкнутый переключатель формирует на катоде соответствующего диода запирающий потенциал. В этом случае при Rн >> R, все напряжение источника питания Uп приложено к активно-емкостной нагрузке, форма сигнала на которой будет определяться постоянной времени заряда зар = R Cн (ток через закрытый диод не проходит). Если разрядный переключатель соединить с общим проводом, диод откроется и емкость нагрузки Сн начнет разряжаться через малое сопротивление открытого диода rd (rd << Rн). Форма спада формируется постоянной времени цепи разряда раз = rd Cн . Наличие хотя бы одного нулевого уровня на входных клеммах приведет к шунтированию Rн малым входным сопротивлением источника и, как следствие, нулевому сигналу на выходе (напряжение питания будет падать на R). Единичный уровень, поданный на все разрядные входы (все переключатели разомкнуты) приведет к появлению единицы на выходе – классический пример реализации логической функции «И» («1» на выходе появляется только тогда, когда в состоянии «1» находится И 1-ый вход, И 2-ой вход И … n – ый вход) .

Диодный логический элемент «ИЛИ» представлен на рисунке 4.5. Посредством разомкнутого многоразрядного переключателя единичный информационный уровень подается на диодную матрицу. Появление хотя бы одного единичного сигнала на любом из разрядов откроет соответствующий диод и единица с учетом постоянной времени заряда цепи нагрузки (ЗАР = RНСН) через открытый диод установится на выходе элемента. Нулевой выходной сигнал будет сформирован только после размыкания всех переключателей и разряда нагрузочной емкости через сопротивления RБ и RН). Форма спада определяется постоянной времени цепи разряда (раз = CН RН RБ /( RН + RБ)).

+Uп

Uвх1

VD1

Uвх2

VD2

Uвых

(Rн,

Сн)

Uвх

VDn

Uвхn

а

Uвых

Uвхn

t

б

а – принципиальная

схема; б – форма выходного сигнала

Рисунок 4.4 –

Диодный элемент «И»

Uвх1

VDn

VD1

Uвых

(Rн,

Сн)

Uвых

t

а

Uвх2

VD2

Uвхn

+Uп

Uвых

зар

Uвхn

раз

б

а – принципиальная

схема; б – форма выходного сигнала

Рисунок

4.5 – Диодная схема «ИЛИ»

Инвертор (элемент «НЕ», см. рисунок 4.6) образуют ключевым транзисторным инвертирующим каскадом. При низком уровне входного напряжения на выходе присутствует единица (транзистор закрыт, все напряжение питания приложено к нему) и, наоборот, при единичном входном воздействии на коллекторе транзистора установится ноль (транзистор входит в зону насыщения, напряжение питания падает на RК).

+Uп

Uвх

Uвых

RК

а

0

1

0

1

0

Uвх

Uвх

Uвых

0

t

1

0

1

1

б

t

а – принципиальная

схема; б – рабочая диаграмма

Рисунок

4.6 – Транзисторный элемент «НЕ»

4.3 Классификация основных типов логических элементов

Кроме рассмотренных в предыдущем разделе диодных логических элементов существует исторически сложившаяся схемотехническая классификация основных типов транзисторных логических элементов.

В ней выделены следующие классы (типы логики) элементов:

- транзисторно-транзисторная логика (ТТЛ);

- эмиттерно-связанная логика (ЭСЛ);

- транзисторно-транзисторная логика с диодами Шотки (ТТЛШ);

- логика на полевых транзисторах (каналы n-МДП, p-МДП; комплементарные ключи на МДП-транзисторах – КМДП, КМОП);

- интегрально-инжекционная логика (И2Л);

- логика на основе полупроводника из арсенида галлия (GaAs).

Наиболее широко в настоящее время используются ТТЛ, ТТЛШ, КМОП, ЭСЛ. Перспективными сериями являются КМОП и GaAs технологии.

Серии на полевых транзисторах характеризуются малым потреблением энергии, что крайне актуально сегодня. Кроме того, хотя они и уступают ТТЛ и ТТЛШ логике в быстродействии, но имеют преимущество в помехозащищенности и перспективном потенциале.

В ближайшие годы серьезное внимание уделяется развитию технологии изготовления интегральных микросхем (ИМС) на арсениде галлия. Впятеро большая подвижность электронов в монокристаллах этого двухэлементного полупроводника, чем в кремнии, позволяет создавать в объеме арсенида галлия активные структуры с кратно более высоким быстродействием. Преимущество в быстродействии востребовано, прежде всего, в маломощных больших интегральных схемах (БИС). Широкому внедрению арсенида галлия в производство ИМС препятствуют трудности, связанные с обеспечением переноса параметров элементов на кристаллические структуры. Разброс характеристик получается намного больше, чем в случае использования кремния. Для сравнения: минимальное время задержки сигнала на КМОП структурах с диодами Шоттки составляет 0,12 нс, на арсениде галлия – 0,019нс.

Логические элементы и другие цифровые электронные устройства выпускаются в составе серий интегральных микросхем. Серия – это совокупность цифровых элементов, которые характеризуются общими технологическими и схемотехническими решениями, а также уровнями электрических сигналов и напряжений питания.

В обозначении серий логических элементов заключается ряд ключевых параметров. Для интегральных схем широкого применения перед обозначением серии ставится буква К, например, К561ЛА7.

Следующая за буквой цифра, в примере это 5, говорит о технологии производства интегральной микросхемы (ИМС). 1, 5, 6, 7 – полупроводниковые ИМС; 2, 4, 8 – гибридные; 3 – прочие.

Второй цифровой элемент (три цифры) обозначает порядковый номер разработки серии (от 000 до 999).

Третий элемент – две буквы, обозначающие подгруппу соответствующую функциональным особенностям элемента.

Четвертый элемент – условный номер разработки микросхемы по функциональному признаку.

И наконец замыкает ряд обозначений буква, характеризующая функциональные особенности, например, К573ПВ1А (Б,В). Данная ИМС (АЦП) с буквой «А» имеют линейность преобразования 0,1%, Б–1%, В–3%.

Транзисторно-транзисторные интегральные микросхемы – один из самых распространенных типов ИМС. Существует много разновидностей ТТЛ схем, однако, несмотря на некоторые различия, их объединяет принцип работы и основные характеристики. Упрощенная схема базового ТТЛ элемента приведена на рисунке 4.7.

VT1

VT2

Uвх1

Uвх2

VD2

R

RК

Uвх3

E

VD3

1

&

Х1

Х2

У

Рисунок 5.3–

Приоритетный шифратор К555ИВ1

VD1

Х3

a

б

а –

принципиальная схема ЛЭ «3И – НЕ» ТТЛ,

б – условное обозначение

Рисунок 4.7 –

Базовый элемент ТТЛ

На схеме можно выделить два основных каскада: входной на много эмиттерном транзисторе VT1, реализующем функцию «И» и усилительный с инвертированием на VT2. Если на всех входах присутствует логическая единица, эмиттерный переход VT1 оказывается смещенным в обратном направлении, на базе транзистора VT2 появляется ток через резистор R и смещенный в прямом направлении переход коллектора VT1, что открывает транзистор VT2 и потенциал его коллектора падает до нуля. При нулевом уровне хотя бы одного входного разряда соответствующий p-n переход шунтирует остальные переходы и нулевой сигнал снижает ток базы VT2, закрывая его и устанавливая на выходе единицу.

Диодные элементы во входных цепях защищают транзистор VT1 от пробоя. На рисунке 4.8 представлена форма входного тока в зависимости от уровня входного напряжения.

IВХ, mA

1

UВХ, В

-2

0

2

4

-1

-2

Рисунок 4.8 –

Входная характеристика базового ЛЭ

ТТЛ для Uп

= 5 В

При единичном входном сигнале величина входного тока незначительна, т.к. эмиттерный переход смещен в обратном направлении вплоть до значения напряжения 5 В. При напряжении более 5,5 В на входе ток резко возрастает и достигает величины 1 мА. Это предельное значение тока, а следовательно и входного напряжения. Поэтому питание элементов ТТЛ ограничено значением UП = 5В 10% . Аналогично идет рост входного тока при наличии отрицательного входного потенциала. Для большинства ТТЛ ИМС эта величина не может превышать значение UВХ > - 0,4В. Для защиты эмиттера входного транзистора от выбросов отрицательного потенциала устанавливаются демпфирующие диоды VD1÷VD3.

В динамическом режиме (tФ и tС) в оконечных каскадах реальных ТТЛ элементов существует момент короткого замыкания, объясняемый задержками переключения активных структур. В это время от источника потребляется большой ток. Следовательно, чем выше частота цифрового сигнала, тем выше энергопотребление. Кроме того броски тока вносят помехи в информационные сигналы. С целью защиты от помех такого рода цепи питания ТТЛ микросхем шунтируют емкостями СШ 100 нФ на каждый корпус.

Микросхемы эмиттерно-связанной логики (ИМС ЭСЛ) представляют собой транзисторные переключательные схемы с объединенными эмиттерами и обладают по сравнению с другими типами цифровых ключей наибольшим быстродействием и большой потребляемой мощностью. Большое быстродействие (малое tСР) определяется работой активных элементов в ненасыщенном (линейном) режиме, ограничения перепада выходного логического сигнала, включения в выходных каскадах эмиттерных повторителей [ 3 ]. Из разработанных ИМС ЭСЛ наиболее широкое распространение получили серии 100 и К500 являющиеся аналогами импортной серии МС 10000 фирмы Motorola.

Рисунок 4.9 –

Элемент ЭСЛ «ИЛИ-НЕ, ИЛИ»

Питание ЭСЛ осуществляется от источника напряжения UП = -5В, (см. рисунок 4.9) коллекторные цепи заземляются. Такое включение обеспечивает меньшую зависимость выходного сигнала от наводок по цепи питания и лучшую помехоустойчивость. Уровень логического нуля лежит в пределах U0 = - 1,7 B, логической единицы - U1 = - 0,9 B (ЭСЛ считается положительной логикой). Значение перепада напряжения для ЭСЛ составляет 0,7-0,8 В. Отрицательные и малые перепады уровней требуют для стыковки с элементами серии ТТЛ применения специальных схем (преобразователи уровней), которые входят в состав всех указанных серий ЭСЛ.

На примере элемента «ИЛИ-НЕ и ИЛИ» (см. рисунок 4.9) представлен принцип работы ключа ЭСЛ. Схема состоит из сложного дифференциального каскада, собранного на транзисторах VT1-VTn, VTд. В этом каскаде потенциал VTд базы определяется напряжением смещения (UОП = - 2В), которое стабилизируется каскадом (VTэс, Rc1, VD1, VD2, Rэс) эмиттерного повторителя с элементами термостабилизированной цепи в базе транзистора. При напряжении на входных транзисторах большем напряжения смещения VT1-VTn будут закрыты, а транзистор VTд будет открыт и его коллекторный потенциал низкого уровня (U0 = - 1,7 B) будет через выходной эмиттерный повторитель (VTэ2) присутствовать на прямом выходе «Вых. ИЛИ» элемента. Если хотя бы на одном входном транзисторе появиться уровень логической единицы (U1 = - 0,9 B), он откроется и за счет ООС на Rэ закроет VTд. На выходе первого эмиттерного повторителя VTэ1 появится сигнал инверсный входному (U0 = - 1,7 B), VTэ2 установит сигнал единицы (U1 = - 0,9 B).

Выходные эмиттерные повторители подключаются к источнику смещения (UСМ = - 2,0 B 5%) через внешние нагрузочные резисторы RН1 и RН2 с номиналом 51 Ом. Малое выходное сопротивление элемента обеспечивает согласование выходных и входных напряжений уровней логических элементов при их совместной работе и возможность непосредственно подавать сигналы в коаксиальный кабель с волновым сопротивлением 50 Ом.

Функциональные возможности серий ЭСЛ не уступают другим сериям. В их состав входят элементарные логические элементы («И», «ИЛИ») дешифраторы, мультиплексеры, запоминающие и арифметические устройства.

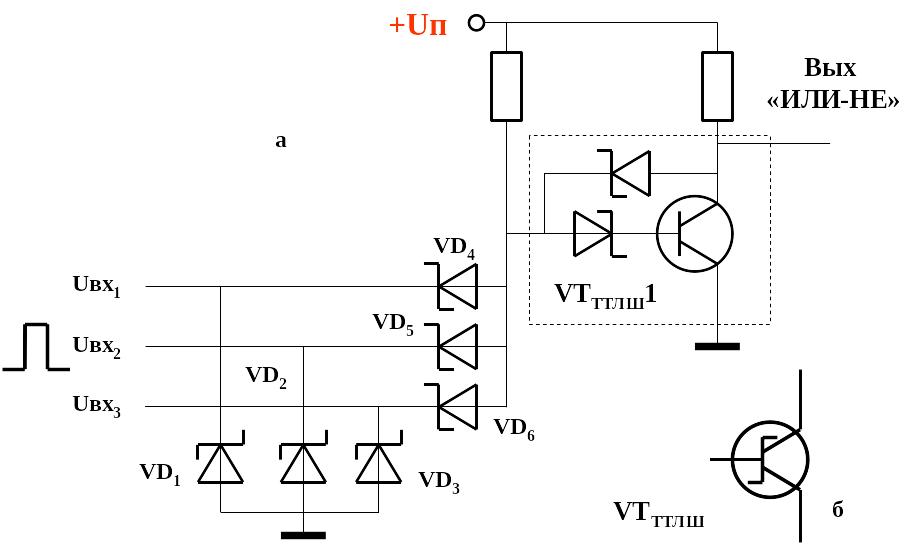

Транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ) уменьшает время переключения элементов ТТЛ до единиц наносекунд. Это быстродействие достигается введением в схему диодов Шоттки, у которых практически отсутствует диффузионная емкость р-n перехода, что поднимает частотный диапазон подобных полупроводниковых диодов до десятков ГГЦ. Диоды Шоттки добавляются в обычный базовый элемент ТТЛ (см. рисунок 4.10). Включение диодов в обратном направлении параллельно коллекторному переходу транзистора и такого же диода в цепь базы в прямом направлении (для компенсации падения напряжения на открытом диоде) позволяет избежать насыщения транзистора, свести время рассасывания к нулю и тем самым значительно увеличить быстродействие элемента.

К серии ТТЛШ микросхем относятся ИМС К1533, К530, К531, К555. Все они характеризуются следующими параметрами:

- напряжение питания + 5 В;

- напряжение низкого уровня не более 0,4 В;

а – принципиальная

схема каскада, б – изображение на схеме

транзистора Шотки

Рисунок 4.10 –

Входной каскад базового ТТЛШ элемента

- напряжение высокого уровня не менее 2,4 В;

- среднее время задержки распространения сигнала tСР 5нс;

- максимальная частота 50 МГц.

ИМС ТТЛШ совместимы по уровню с микросхемами ТТЛ. Мощность потребляемая ТТЛШ элементами меньше соответствующих ТТЛ схем в 5-10 раз.

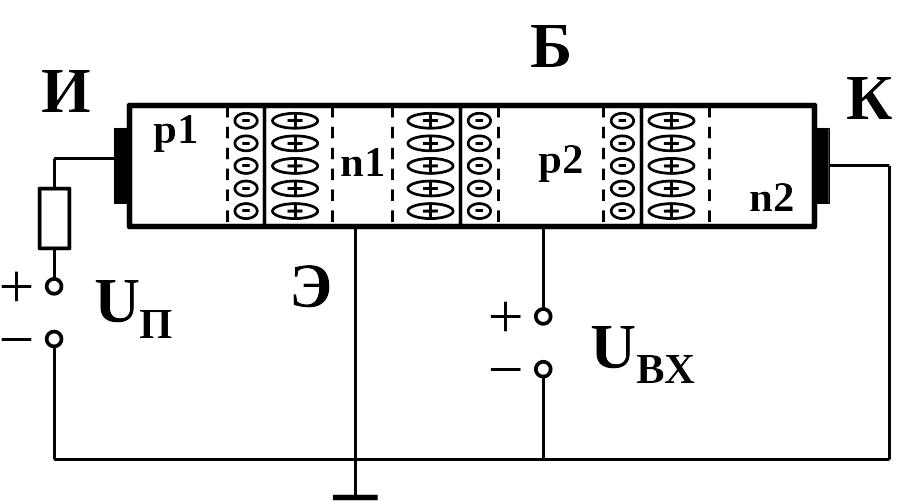

Интегрально-инжекционная логика (И2Л) построена на основе биполярных транзисторов с непосредственными связями. Элементы И2Л отличаются относительно высоким быстродействием (tСР 5-7нс), низкими уровнями питания (0,5-0,9 В) и логических сигналов, очень малым перепадом напряжения переключения.

Логика функционирует на транзисторах с инжекционным питанием. Подобные полупроводниковые структуры реализованы только в интегральном исполнении и не имеют аналогичных решений в дискретной схемотехнике.

Инжекционные схемы питаются через инжекторный переход смещенный в прямом направлении, что дает возможность снизить напряжение питания до 0,6-0,7 В для кремниевых и 0,3-0,4 В для германиевых структур. Число внутрисхемных соединений в элементах с инжекционным питанием ниже, чем в остальных сериях, что приводит к повышению надежности устройств. Схемы с инжекторным питанием могут нормально работать при изменении тока инжектора в пределах нескольких порядков, следовательно, допускают большие колебания напряжения питания.

На рисунке 4.10 изображен инжекторный транзистор, у которого можно выделить две транзисторные структуры, имеющие общие области. Первым транзистором является Р1-N1-P2, вторым – N1-P2-N2. Область Р1 является инжектором носителей (дырок) для области N1 (переход р1-n1 смещен в прямом направлении).

Рисунок 4.10 –

Инжекторный транзистор

При подключении к инжектору плюсового полюса источника питания и подаче единичного логического уровня на «Б» транзистор оказывается в насыщенном состоянии. Уровень нуля составляет U0 0,02 В, уровень U1 0,4 В.

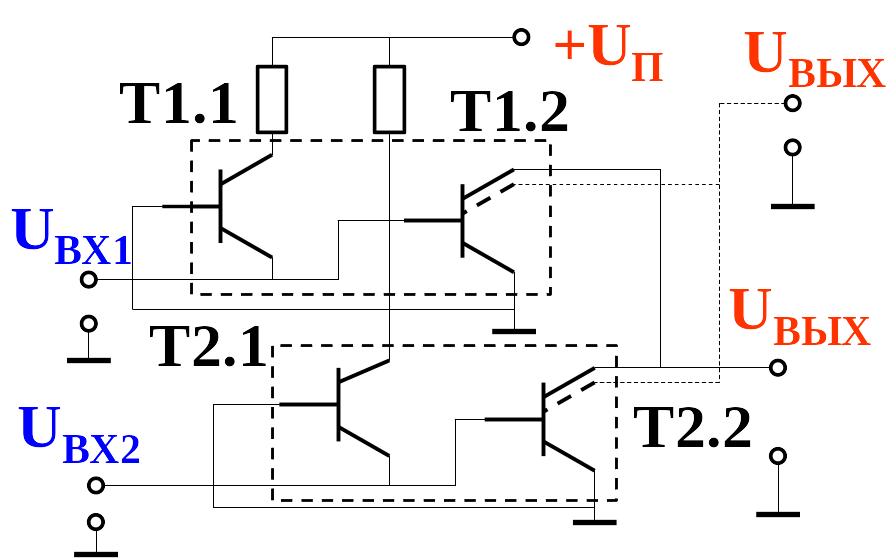

На рисунке 4.11 приведена в упрощенном виде принципиальная схема «ИЛИ-НЕ» структуры для И2Л. Отличительной особенностью базовых элементов И2Л является многоколлекторный транзистор (на рисунке коллекторы показаны пунктиром), используемый для улучшения развязки при подаче выходного сигнала на несколько входных каскадов (повышение коэффициента разветвления по выходу).

При нулевом Uвх1 ток транзистора Т1.1 не протекает в базу Т1.2, (входной ноль шунтирует р-n переход «база-эмиттер» транзистора Т1.2) закрывая и устанавливая его в единичное состояние. Подобно действует и второй инжекционный транзистор. Если на оба транзистора подано нулевое напряжение – на выходе будет протекать в нагрузку единичный инжекционный ток, в случае наличия на выходе хотя бы одного открытого транзистора (любого), он будет шунтировать второй, фиксируя сигнал нуля на выходе ЛЭ.

И2Л применяются в микропроцессорах, запоминающих устройствах с произвольной выборкой, в ЦАП и АЦП, в бытовых приборах (электронные часы, калькуляторы, электронные затворы для фотоаппаратов). Перспективно применение И2Л ИМС в устройствах и системах с автономных питанием.

Рисунок 4.11 –

Базовый элемент «ИЛИ-НЕ» инжекционной

логики

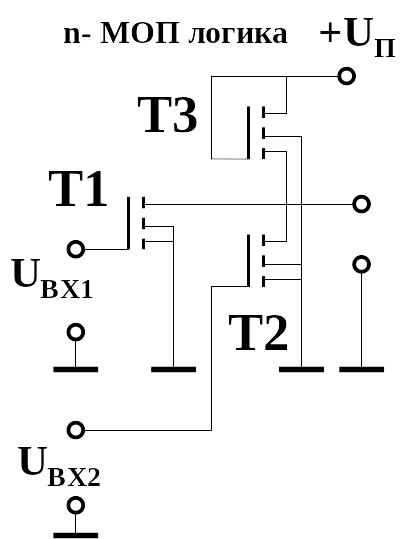

Цифровые ИМС на МОП структурах. В цифровой интегральной схемотехнике применение нашли полевые транзисторы с изолированным затвором. Как известно, подобные транзисторы делятся на два вида: с встроенным и индуцированным (наведенным) каналами (n-типа, р-типа). В отличие от биполярных транзисторов ток в канале полевого переносится основными носителями. В зависимости от напряжения, поданного на управляющий электрод (затвор) ток в канале можно легко изменить, а значит изменить и его сопротивление. Входной ток полевого транзистора практически равен нулю, т.е. он, как аналог электронной лампы, управляется напряжением.

Большинство выпускаемых в настоящее время цифровых интегральных схем (ЦИС) на МОП структурах базируется на транзисторах с индуцированным каналом.

UВЫХ

б

а

UВЫХ

Т2

а – с индуцированным

каналом n-типа;

б – на комплементарных транзисторах

Рисунок 4.12 –

Базовый ЛЭ «ИЛИ-НЕ на МОП транзисторах

Пример реализации функции «ИЛИ-НЕ» на МОП транзисторах с n-каналом представлен на рисунке 4.12а. ЛЭ состоит из нагрузочного Т3 (активная нагрузка) и двух управляющих Т1 и Т2 транзисторов. Когда Т1 и Т2 закрыты (входной сигнал логического «0») на UВЫХ устанавливается высокий уровень. Если UВХ1 или UВХ2 имеют единицу на входе UВЫХ будет нулевым.

Для получения функции «И-НЕ» управляющие транзисторы включаются не параллельно, а последовательно по цепи исток-сток.

Для снижения мощности, потребляемой элементами в статическом режиме используются комплементарные МОП структуры, имеющие обозначение КМОП-логика.

На рисунке 4.12б представлена принципиальная схем базового КМОП-элемента с функцией «ИЛИ-НЕ».

При закрытых Т1 и Т2 транзисторах (низкий уровень входа) Т3 и Т4 открыты и на выходе ЛЭ присутствует логическая «1», если на Т1 или Т2 – «1», на истоке-затворе либо Т3, либо Т4 малое напряжение закрывает один или оба транзистора с установкой выходного сигнала в нулевой уровень.

Достоинствами КМОП –логики по отношению к ТТЛ являются:

- низкая потребляемая мощность в статическом режиме;

- очень высокое входное сопротивление;

- большая нагрузочная способность (коэффициент разветвления 50-100);

-большой диапазон напряжения питания (3-15 В);

- малая зависимость характеристик от температуры;

- технологичность в производстве.

В числе недостатков следует отметить повышенное выходное сопротивление и сравнительно низкий частотный диапазон (до 5 МГц).

Среди известных серий микросхем на КМОП структурах следует отметить К176 и более раннюю 564. Предельная частота сигнала для этих серий составляет 1 МГц. Напряжение питания - 8÷15В.

Более современной серией является К561, для которой предельная частота доходит до 5 МГц, а UП лежит в пределах 3-15 В, при этом выход ИМС К561 серии можно нагружать на ТТЛ логику (в определенном ограничении).

Логика на основе полупроводника из арсенида галлия (GaAs) в сравнении с кремниевыми структурами обладает более высоким быстродействием (в 3-6 раз), определяемым подвижностью электронов. Верхняя граница частоты ИМС на GaAs лежит в пределах 10 ГГц и более.

В таблице 4.1 приведены сравнительные параметры ЛЭ по основным своим характеристикам. «1» условно присвоена лучшему значению параметра, 7 – худшему [ 1 ].

При разработке цифрового устройства выбор типа ИМС зависит от того, какой параметр, из перечисленных в таблице, является определяющим, а чем можно поступиться. В последнем столбце сведена сумма условных оценок, минимум которой характеризует обобщенное относительное превосходство соответствующего типа микросхем. Первое второе и третье места занимают ЛЭ на полевых структурах.

Таблица 4.1 – Сравнительные характеристики ЛЭ