Комбинационные цифровые устройства

Цифровые устройства, построенные на основе элементарных (базовых) ЛЭ можно разделить на два класса: комбинационные и последовательностные.

Комбинационными называются устройства, если его выходные сигналы в каждый момент времени однозначно определяются входными сигналами в этот момент времени.

Все другие конструкции следует отнести к последовательностным устройствам. Данный тип устройств обязательно имеет память. Его выходная информация зависит не только от параметров входных сигналов в данный момент времени, но также от предыстории.

5.1 Шифраторы, дешифраторы, преобразователи кодов

Шифратор (кодер)

– цифровой комбинационный элемент

преобразующий число из десятичной

системы счисления в двоичную. Входам

шифратора последовательно присваивается

значения десятичных чисел, поэтому

подача единичного логического сигнала

на соответствующий вход воспринимается

шифратором как подача определенного

десятичного числа. На выходе шифратора

устанавливается двоичный код. Число

выходов и входов шифратора связано

равенством:

![]() ,

где Х – число входных разрядов, Y

– выходных. Если количество входов

меньше, чем возможная информационная

емкость выходных, такой шифратор

называется неполным,

при

соответствии числа разрядов на входе

информационному пределу выходных

шифратор называется

полным.

Например, 10 разрядов на входе и 4 на

выходе образуют неполный шифратор.

Полным будет шифратор с числом входных

разрядов равным 16.

,

где Х – число входных разрядов, Y

– выходных. Если количество входов

меньше, чем возможная информационная

емкость выходных, такой шифратор

называется неполным,

при

соответствии числа разрядов на входе

информационному пределу выходных

шифратор называется

полным.

Например, 10 разрядов на входе и 4 на

выходе образуют неполный шифратор.

Полным будет шифратор с числом входных

разрядов равным 16.

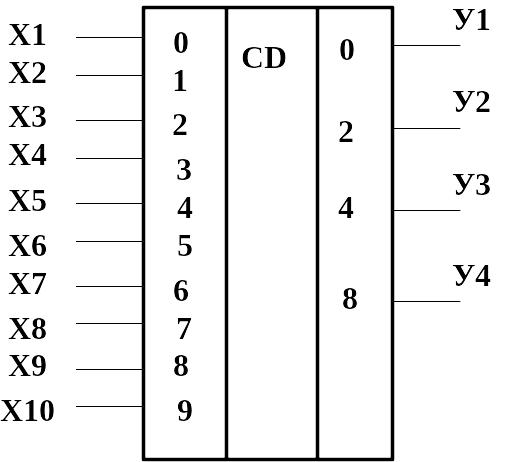

Обозначение шифратора на принципиальных схемах представлено на рисунке 5.1.

Рисунок 5.1 –

Неполный шифратор 10 х 4

По таблице соответствия (см. таблицу 5.1) легко проследить значение выходного сигнала при наличии единичного уровня на любом из входов шифратора (сигнал логической единицы в каждый момент времени подается только на один вход). На выходе У1 единица будет только тогда когда логическая единица будет присутствовать ИЛИ на входе Х1, ИЛИ Х3, ИЛИ Х5, ИЛИ Х7, ИЛИ Х9. В виде математической модели :

У1 = Х1+Х3+Х5+Х7+Х9,

У2 = Х2+Х3+Х6+Х7,

У3 = Х4+Х5+Х6+Х7,

У4 = Х8+Х9.

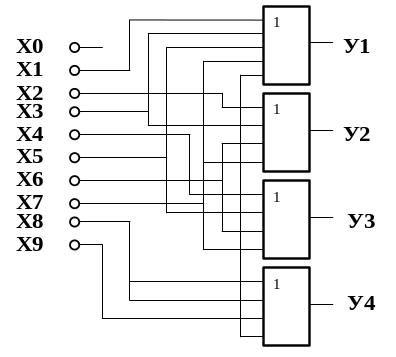

С учетом вышеприведенных соотношений можно устройство шифратора представить в виде совокупности элементарных ЛЭ «4 ИЛИ» (см. рисунок 5.2).

На практике находит применение шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему коду, присутствующему на входе, т.е. на входные разряды допускается одновременно подавать любое число «1», но он выставляет на выходе код числа соответствующего старшего разряда.

Таблица 5.1 – Таблица истинности для неполного шифратора 10 х 4

Десятичное

число

Двоичный код

8-4-2-1

У4

У3

У2

У1

0

0

0

0

0

1

0

0

0

1

2

0

0

1

0

3

0

0

1

1

4

0

1

0

0

5

0

1

0

1

6

0

1

1

0

7

0

1

1

1

8

1

0

0

0

9

1

0

0

1

Рисунок 5.2 –

Шифратор 10 х 4 на ЛЭ «ИЛИ»

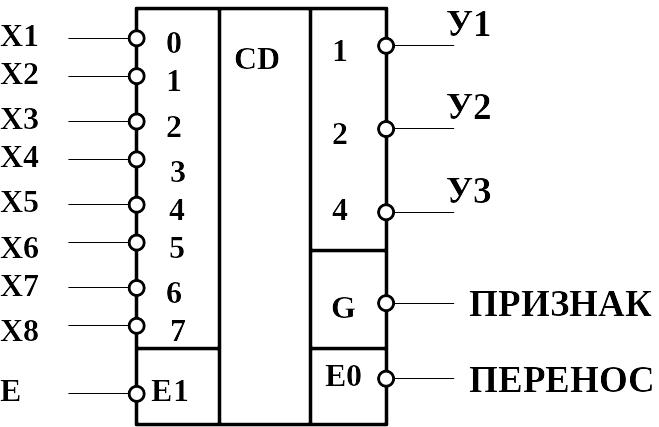

Практическое использование шифраторов – преобразование порядкового номера объекта (датчик, кнопка клавиатуры и т.д.) в двоичный код. При необходимости преобразовать большее десятичное число (наращивание входных разрядов) существуют шифраторы с дополнительными входами разрешения выборки. Например, микросхема К555ИВ1 (см. рисунок 5.3) представляет собой приоритетный полный шифратор 8 х 3 с восемью инверсными входами и тремя инверсными выходами. Кроме инверсного разряда выборки ЕI со стороны входов, со стороны выхода имеются разряды переполнения Е0 и признака наличия ненулевого входного кода G.

Рисунок 5.3–

Приоритетный шифратор К555ИВ1

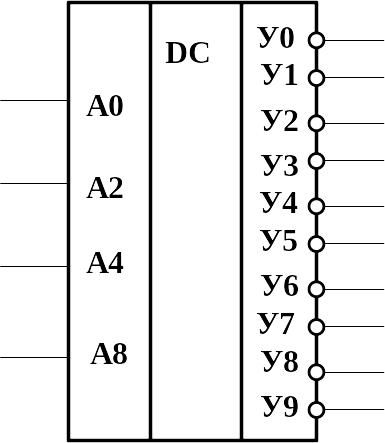

Дешифратором называется комбинационное устройство, предназначенное для преобразования входного двоичного кода в десятичный. По аналогии с шифраторами дешифраторы могут быть полными и неполными. В полном дешифраторе максимальное десятичное число равно пределу информационной емкости входных двоичных разрядов. В противном случае дешифратор называют неполным. Например, дешифратор 3 х 8 будет полным, но 4 х 10 – неполным.

В обозначении ЛЭ реализующего функцию дешифратора используют латинские буквы «DC». На рисунке 5.4 представлено обозначение на принципиальной схеме дешифратора К555ИД6. Он, имея четыре прямых входа и десять инверсных выходов, является неполным дешифратором.

На выходе У0 активный уровень (ноль) будет присутствовать в момент наличия нулевого уровня на всех входных разрядах, при этом на всех остальных выходных разрядах будет логическая единица. Появление единицы на любом входе приведет к появлению нуля на соответствующем двоичному коду десятичном выходе. Если на входе появится двоичный код превышающий цифру «9» (например, двоичный код «1101» – десятичный код «13»), во всех выходных разрядах будет «1».

Рисунок 5.4 – Вид

дешифратора К555ИД6 на принципиальной

схеме

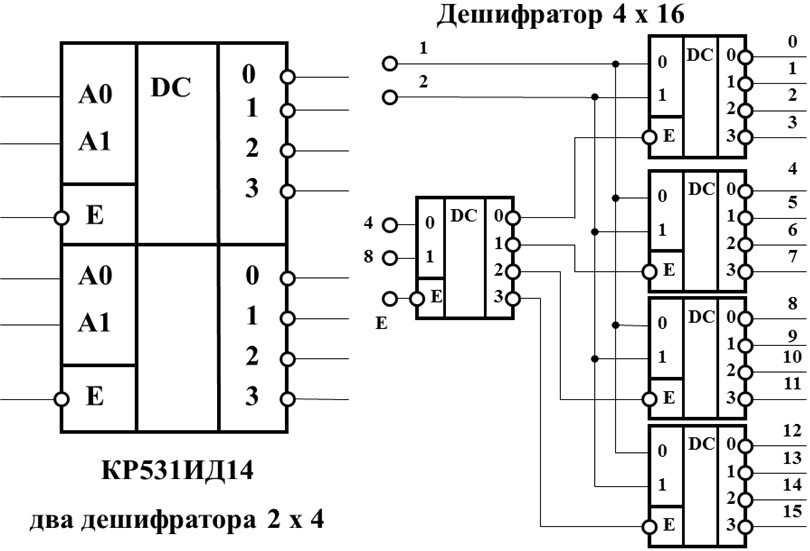

Помимо информационных входов в дешифраторе может встраиваться вход разрешения считывания. Например, в ИМС К531ИД14 (см. рисунок 5.5 а), состоящей из двух полных дешифраторов 2 х 4, в каждом из которых имеется инверсный вход «Е», позволяющий дешифрировать входной сигнал только при разрешающем нулевом уровне. Если на входе «Е» находится логическая единица, независимо от состояния входных информационных разрядов на инверсных выходах будет присутствовать единица. Наличие входа разрешения позволяет наращивать размерность дешифратора. Например, из нескольких дешифраторов с размерностью 2 х 4 можно легко сформировать дешифратор 4 х 16 (см. рисунок 5.5 б).

Дешифраторы применяются в сложных цифровых устройствах для:

- преобразования двоичной информации (например, кода адреса внешнего блока, датчика и т.д., с которого необходимо получить данные или направить сигнал управления), формируемой вычислительным модулем (например, контроллером);

- преобразования кода (например, из двухразрядного в трехразрядный);

а

б

Рисунок 5.5 –

Дешифратор К531ИД14 (а) и его схемотехнические

возможности (б).

- мультиплексирования (объединения) и демультиплексирования (разветвления) цифровых сигналов.

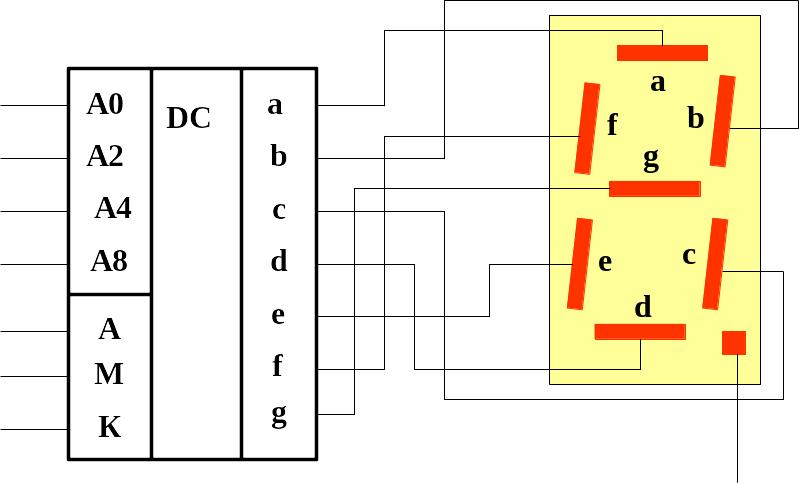

Преобразователь кода – в общем случае, устройство, служащее для преобразования одного кода в другой (рассмотренные выше устройства дешифрации есть ни что иное, как преобразователи кода двоичного в десятичный). Функцию преобразования кода обозначают через Х / У.

Преобразователи кода широко применяют, например, в устройствах цифрового отображения информации, где в качестве элементов индикации используют семисегментные индикаторы (люминесцентные или светодиодные). На рисунке 5.6 представлен вариант принципиальной схемы вывода двоичного числа на светодиодный индикатор в виде десятичной цифры.

Кроме информационных двоичных разрядов преобразователь кода К176ИД2 содержит дополнительные входы управления. Вход «А» - разрешения индикации, нулевой уровень которого гасит индикаторы, единичный отображает входное двоичное число. Вход «М» - позволяет выбрать вид входной кодировки: в прямом или дополнительном коде представлена входная информация. Вход «К» - передает информацию с внутреннего накопительного регистра на выход, что позволяет избавиться от эффекта мелькания цифр при реализации индикации методом досчета: коротким единичным импульсом данные переписываются на выход микросхемы.

Рисунок 5.6 –

Дешифратор К176ИД2 в роли преобразователя

кода 4 / 7 для вывода информации на

светодиодную матрицу с общими катодами

При построении преобразователя кода требуемой размерности первоначально формируют таблицу истинности. Для примера рассмотрим построение преобразователя 2 / 3. Соответствие кодов сведено в таблицу 5.2.

Таблица 5.2 – Таблица истинности преобразования кода 2 / 3

N п/п

|

Х1 |

Х2 |

У1 |

У2 |

У3 |

1 |

0 |

0 |

0 |

1 |

1 |

2 |

1 |

0 |

1 |

0 |

0 |

3 |

0 |

1 |

1 |

1 |

0 |

4 |

1 |

1 |

0 |

0 |

1 |

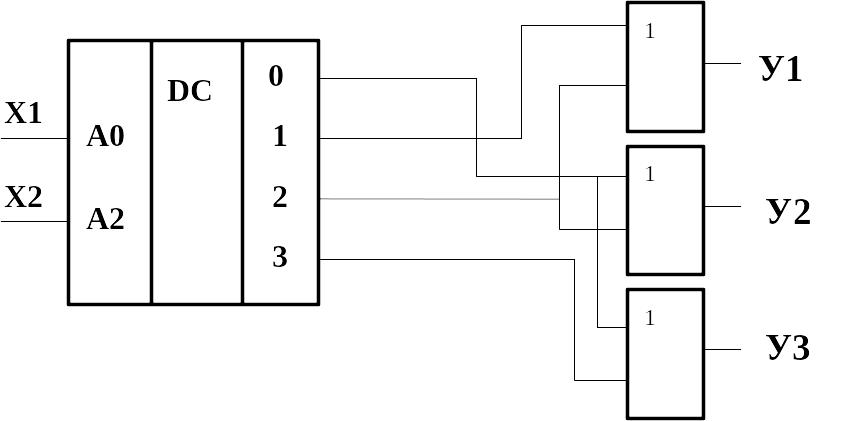

Устройство, реализующее условия таблицы истинности, представлено на рисунке 5.7. Для этих целей использован дешифратор К531ИД14 и три ЛЭ «3 ИЛИ».

5.2 Мультиплексоры, демультиплексоры.

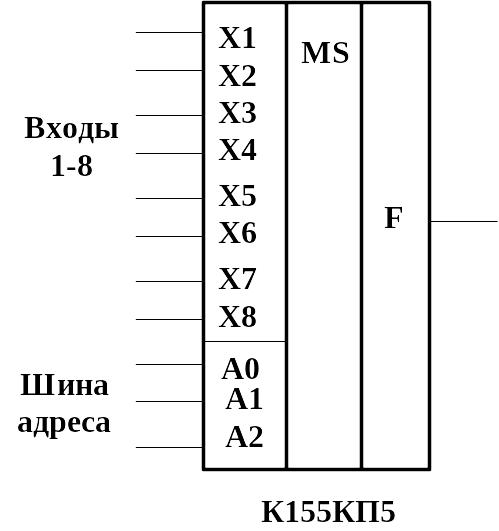

Мультиплексор – комбинационное устройство, обеспечивающее передачу в требуемом порядке цифровой информации с нескольких входных разрядов на один выходной. Функцию мультиплексирования обозначают «MS» или «MUX». По своим функциональным особенностям мультиплексор аналогичен многоразрядному коммутатору-переключателю, который последовательно соединяет один из нескольких входов по заданному алгоритму с единственным выходным разрядом.

Рисунок 5.7 –

Принципиальная схема преобразователя

кода, соответствующая таблице истинности

5.2

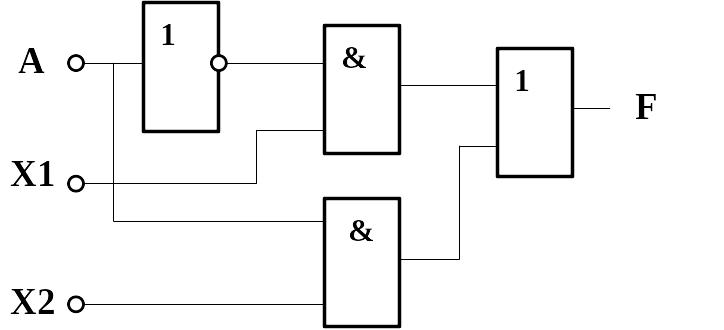

Кроме информационных входных разрядов в мультиплексоре имеются адресные входы, предназначенные для выбора того входного разряда, информация которого передается на выход «F». По аналогии мультиплексор называется полным, если число входных разрядов соответствует максимальной емкости шины адреса, который, как правило, формируется в двоичном коде, в противном случае мультиплексор называют неполным. На рисунке 5.8 показана принципиальная схема коммутатора

Рисунок 5.8 –

Принципиальная схема мультиплексора

21

на базовых ЛЭ «НЕ», «2-И» и «2-ИЛИ»

2 1, организующего передачу входной цифровой информации с двух входов (Х1 и Х2) на один выход (F). В обозначении типа микросхемы- мультиплексора используются буквы КП.

На рисунке 5.9 приводится изображение мультиплексора К155КП5 на принципиальных схемах.

Рисунок 5.9 –

Мультиплексор К155КП5 формата 8

1

Мультиплексоры являются универсальными логическими устройствами, на основе которых создаются различные комбинационные и последовательностные схемы. Часто используют мультиплексоры для преобразования двоичного параллельного кода в последовательный. Для этого на информационные входные разряды подается информация, а посредством шины адреса, по очереди каждый разряд коммутируется на единственный выход. По такому принципу работают сдвигающие регистры, о которых речь пойдет несколько позже.

Все серии ИМС широкого применения имеют в своем составе мультиплексоры: К155КП1, К555КП17, К561КП3, К531КП18 и т.д.

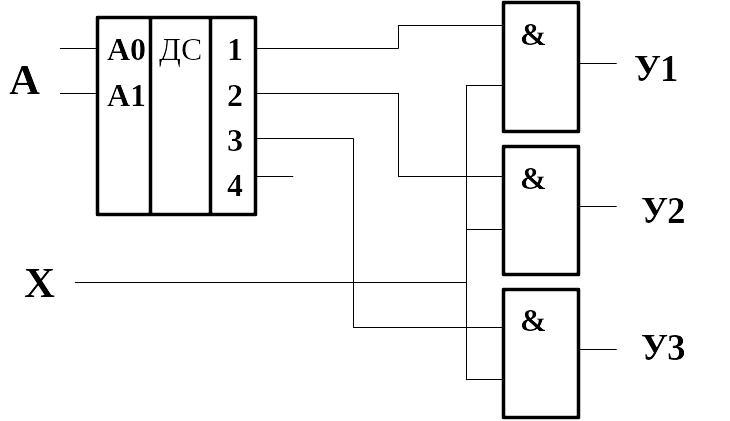

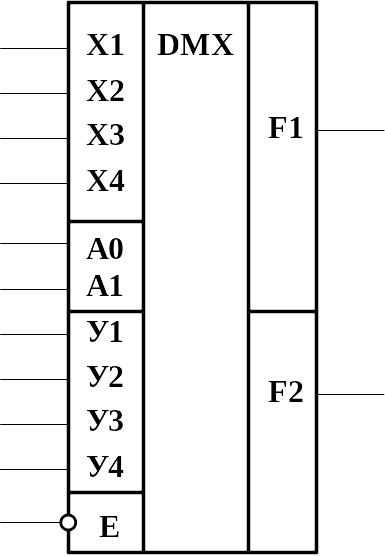

Демультиплексором называется комбинационное устройство, предназначенное для передачи одного цифрового сигнала на один из нескольких выходов, согласно коду адресной шины. Демультиплексор противоположен по реализуемой функции, обозначаемой DMХ или DMS, мультиплексору.

Демультиплексор может быть полным, в случае равенства числа выходов, максимальной емкости адресной шины и неполным при меньшем числе выходов.

Реализация демультиплексора на основе базовых ЛЭ («ИЛИ» и дешифратора 2 х 4) представлена на рисунке 5.10.

Рисунок 5.9 –

Функциональная схема демультиплексора

формата 1

3

Работа демультиплексора очень схожа по функциональным особенностям с дешифратором. Поэтому в обозначении демультиплексоров используются те же буквы ИД. В описании названия ИМС в этом случае функции дешифратора и демультиплексора объединяют, например известны дешифратор-демультиплексор (дешифратор 4 х 16 или демультиплексор 1 16) К155ИД3, или К531ИД7(дешифратор 3 х 8 или демультиплексор 1 8), в которых для организации функции демультиплексирования в качестве адресных шин используют информационные разряды, а входной разряд – вход разрешения Е.

При использовании КМОП-технологии организация мультиплексирования-демультиплексирования становится возможной на основе двунаправленных ключей, управляемых адресными сигналами. При этом поток информации, передаваемой с входа на выход, может быть как цифровым, так и аналоговым. Благодаря такой возможности функции мультиплексора-демультиплексора реализуются одной ИМС, например, К561КП1.

Данная ИМС содержит два мультиплексора-демультиплексора 4↔1 в корпусе(см. рисунок 5.10), имеет общие адресные шины и один инверсный разряд выбора (Е). Соединение входа и выхода осуществляется на основе соответствующего разряда шины адреса и, обязательно, нулевого активного уровня на входе Е. Поскольку передача информации осуществляется через аналоговый ключ, при неактивном уровне на входе Е выходной разряд оказывается в особом состоянии, который носит название Z-состояние или высокоимпедансное состояние (третье состояние). Подобные ИМС входят в состав серий на основе КМОП структур: К561, К564, К590, К176, К591, К1564.

Рисунок 5.10 –

Сдвоенный мультиплексор-демультиплексор

К561КП1 формата 4 ↔

1 со входом выборки микросхемы (Е).

5.4 Арифметико-логические устройства

Арифметико-логическим устройством (АЛУ) называется функционально законченный узел ЭВМ, предназначенный для реализации логических и арифметических операций с входной информацией. АЛУ является одним из основных узлов ЭВМ.

Анализ работы вычислительных машин показал, что 50% выполняемых ими операций – операции арифметического умножения, в то время как арифметическому сложению отводится 45%. Важность этих операций подтверждается тем, что при описании характеристик ЭВМ указывают продолжительность именно этих процессов.

Выполнение арифметических действий в ЭВМ осуществляется аппаратным и программным путем. В данном курсе рассматриваются только аппаратные способы.

Сумматоры, цифровые компараторы.

Сумматором называется комбинационное логическое устройство, предназначенное для выполнения операции арифметического сложения двоичных чисел. Сумматоры – один из основных блоков арифметико-логического устройства.

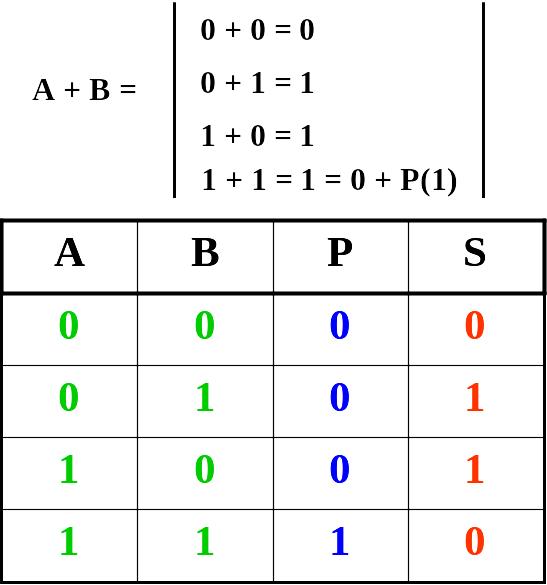

Чтобы понять принцип аппаратной реализации процесса арифметического сложения двух двоичных чисел рассмотрим таблицу истинности операции их сложения. Для простоты возьмем два одноразрядных числа А и В (см. рисунок 5.11).

Рисунок 5.11 –

Принцип сложения двоичных чисел и

таблица истинности.

Операция логического сложения двух одноразрядных чисел в двоичном коде характеризуется следующими правилами:

- ноль плюс единица = единица;

- единица плюс ноль = единица:

- ноль плюс ноль = ноль

- единица плюс единица = ноль плюс единица в разряде переполнения (переносится в следующий старший разряд).

Сказанное выше сведено в таблицу состояния (истинности), где за А и В обозначены логические переменные, S – разряд результата сложения и Р – разряд переполнения на выходе ЛЭ. Особенностью устройств логического сложения многоразрядных переменных является поразрядное выполнение сложения с формированием сигнала переноса (Р) для каждого разряда (см. рисунок 5.12).

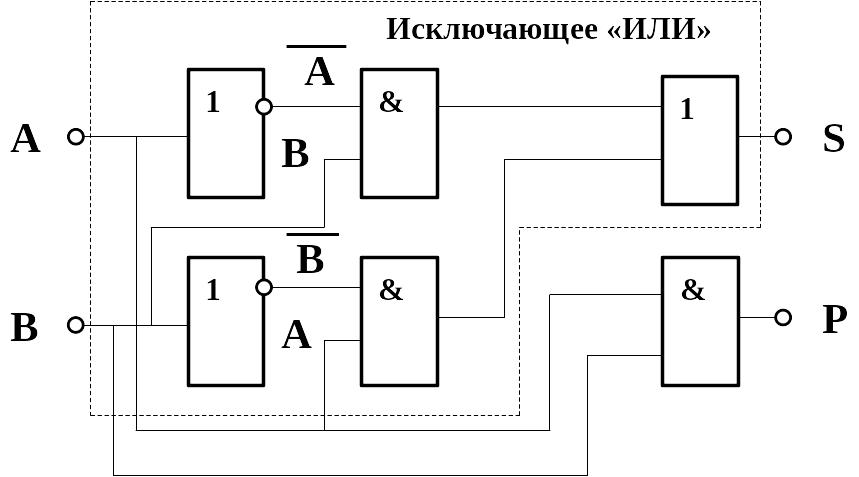

При рассмотрении таблицы рисунка 5.11 столбец S есть, не что иное как реализация логической функции «ИСКЛЮЧАЮЩЕЕ ИЛИ» , а столбец Р – результат умножения переменных, т.е. S = A B, Р = АВ.

Рисунок 5.12 –

Принципиальная схема одноразрядного

полусумматора

Устройство, выполняющее таблицу истинности (см. рисунок 5.11), называемое полусумматором, изображено на рисунке 5.12. Полусумматор, как устройство, имеющее только два входа, может использоваться для сложения лишь младших разрядов.

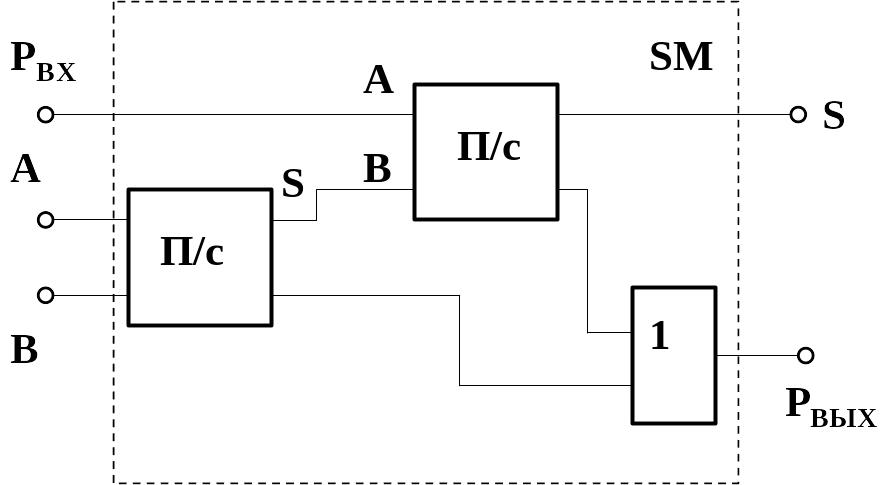

Суммирование двух многоразрядных двоичных чисел производится поразрядно с применением дополнительного входа, куда подается выходной сигнал от разряда переполнения суммирования в предыдущем разряде. Функциональная схема такого устройства приведена на рисунке 5.13 на основе уже рассмотренного полусумматора и ЛЭ «ИЛИ».

Рисунок 5.13 –

Принципиальная схема одноразрядного

сумматора

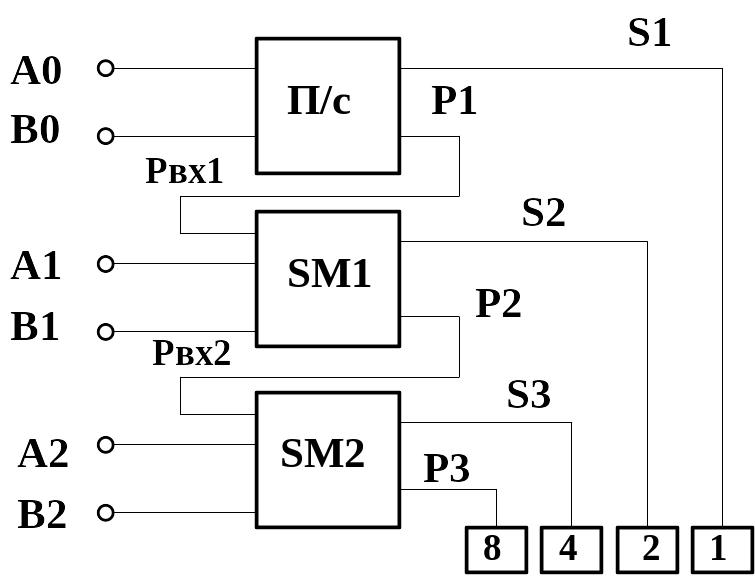

Для того, чтобы суммировать аппаратно два многоразрядных числа, необходимо обвязать полные сумматоры и один полусумматор (для младшего разряда). Пример выполнения суммирования двух трехразрядных чисел с применением вышеперечисленных средств представлен на рисунке 5.14.

Рисунок 5.14 –

Принципиальная схема трехразрядного

сумматора

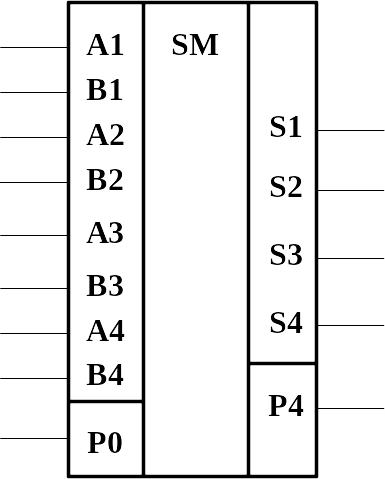

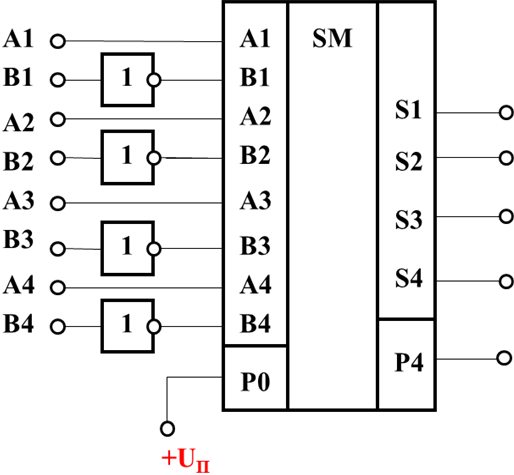

В интегральном исполнении выпускают одноразрядные, двухразрядные и четырехразрядные двоичные сумматоры. Примером четырехразрядного сумматора является ИМС К155ИМ3 (см. рисунок 5.15). Функция суммирования обозначается SM

Рисунок 5.15 –

Четырехразрядный двоичный сумматор

К155ИМ3

При наращивании разрядности суммируемых чисел сумматоры соединяются последовательно. При этом выходные разряды переноса соединяют с Р0 сумматора более высоких разрядов.

На вход Р0 первого в иерархии сумматоров подают уровень нуля (соединяют с общим проводом).

Рассмотренные сумматоры могут легко применяться для построения схем вычитания двоичных чисел. Операция вычитания заменяется операцией сложения, путем представления вычитаемого в дополнительном коде:

![]()

Рассмотрим, например процедуру вычитания: А = 12, В = 7. Двоичный код числа А (12) – 1100, числа В (7) – 0111. Дополнительный код числа ВДОП (9) – 1001, ВОБР – 1000.

Следовательно, разность А – В будет равна:

1100 – 0111 = 1100 + 1001 = 1100 + 1000 + 1 = 0101(1) (десятичное число 5, (1) – говорит о наличии единицы, переносимой в пятый старший разряд).

В данном примере сложение двух единиц старшего разряда дает единицу в разряде переполнения – это говорит только о том, что число А больше чем В, т.е. результат вычитания есть положительное число. В случае, когда в разряде переполнения результата замены вычитания сложением остается ноль – число В больше А и перед разностью ставится знак минус, но при этом число результата выражено в дополнительном коде. Например, пусть А = 6, а В = 24.

А – В = 00110 – 11000 = 00110 + 00111 + 1 = 01110(0) (дополнительный код десятичного числа – 18). Процедура восстановления прямого кода по обратному достаточно проста: дополнительное число рассматривают с младшего разряда, все нули и первую встретившуюся единицу переписывают, остальное инвертируют. В последнем примере прямой код результата вычисления разности получается из дополнительного: 01110(0) 10010 и знак минус перед разностью (-18). Второй способ получения прямого кода из дополнительного – двоичное число, выраженное дополнительным кодом инвертируют и прибавляют к нему единицу: 01110 10001 + 1 = 10010 (-18).

Реализация вычитания двух 4-х разрядных чисел на сумматоре К155ИМ3 представлена на рисунке 5.16.

На входы А подается код уменьшаемого, В – вычитаемого. С разряда переполнения Р4 единица поступает на вход Р0 (прибавляется единица в преобразовании прямого кода числа В в дополнительный код). Посредством инверторов на входах В на входы сумматора поступают инверсные сигналы (для преобразования прямого кода числа В в дополнительный код).

Таким образом, если на выходе Р4 появляется единица – число А больше чем В и на выходах сумматора код разницы представлен прямым кодом. В случае наличия нуля на выходе переполнения - число А меньше числа В, а код результата является дополнительным.

Рисунок 5.16 –

Четырехразрядный двоичный

сумматор-вычитатель (для А > В) на

основе К155ИМ3

Рассмотренные сумматоры применяют и для аппаратного умножения двоичных чисел, хотя раньше традиционно эти операции выполнялись программно. Применение специализированных ИМС позволило значительно увеличить быстродействие.

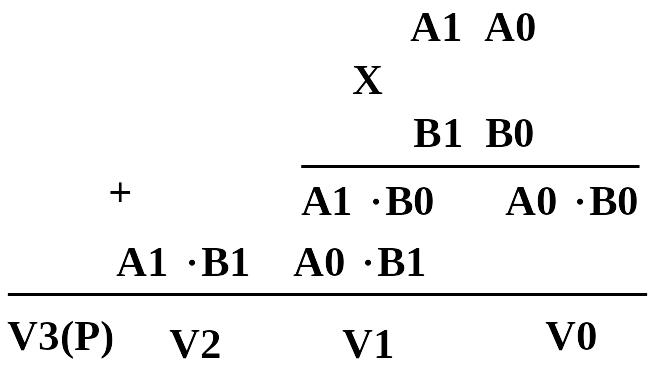

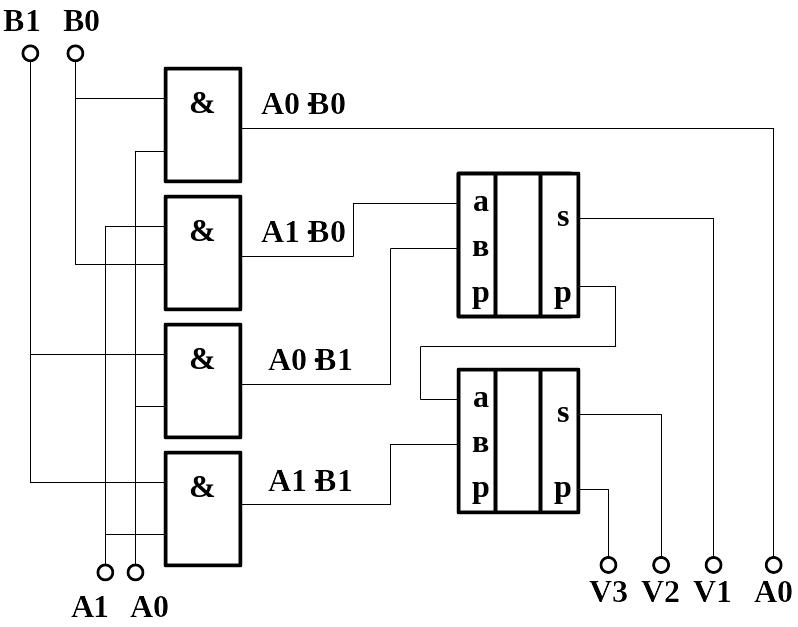

На рисунке 5.17 представлена блок-схема реализации арифметического умножения двух двухразрядных чисел А и В с использованием одноразрядных сумматоров.

Рисунок 5.17 – Блок

схема умножения двух двухразрядных

чисел

Процедура умножения является стандартной, какой пользуются повсеместно – умножение столбиком. Операция проводится поразрядно. Формируются парные произведения, которые с учетом веса перемножаемых разрядов складываются. В результате получается новое число.

Структурная схема устройства приводится на рисунке 5.18.

Рисунок 5.18 –

Структурная схема умножителя двухразрядных

чисел.

Цифровые компараторы

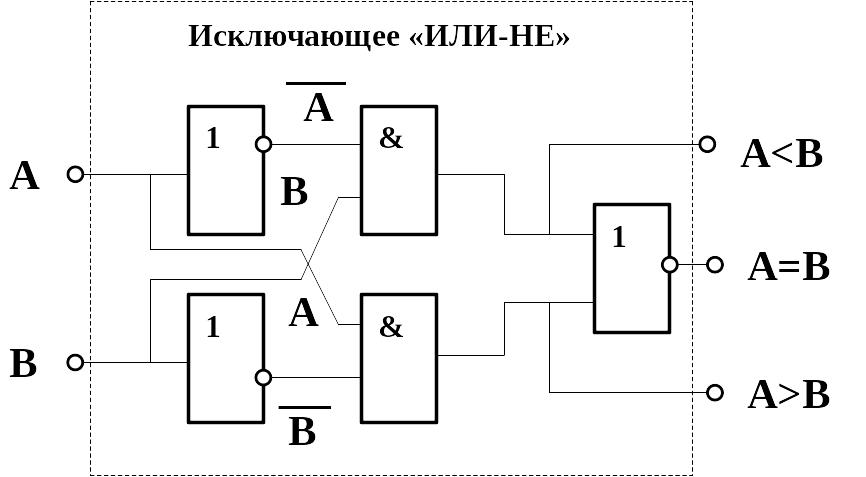

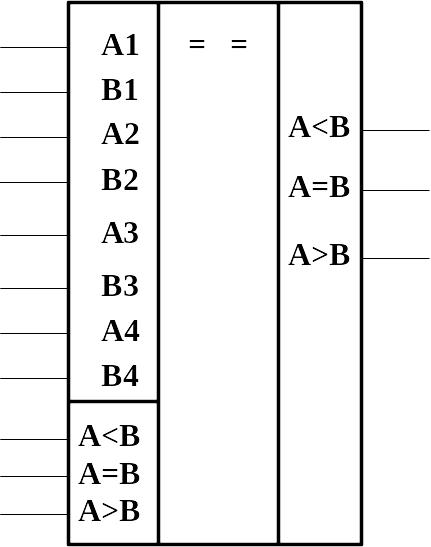

Цифровые компараторы предназначены для сравнения двух чисел выраженных в двоичном коде. Сравнение производится для двух двоичных чисел с одинаковым числом разрядов. Выходной сигнал компаратора содержит три информационных разряда: разряд равенства двух чисел (например, А = В) и два разряда неравенства (А > В, А < В, см. рисунок 5.19).

Рисунок 5.19 –

Цифровой одноразрядный компаратор на

базовых логических элементах

Цифровой одноразрядный компаратор представляет собой логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ» с дополнительными информационными выходами.

В обозначении функции сравнения используется двойной знак равенства « = = ».

Промышленностью цифровые компараторы выпускаются в виде самостоятельных микросхем, например К561ИП2 – четырехразрядный компаратор (см. рисунок 5.20).

Рисунок 5.20 –

Четырех разрядный компаратор К561ИП2

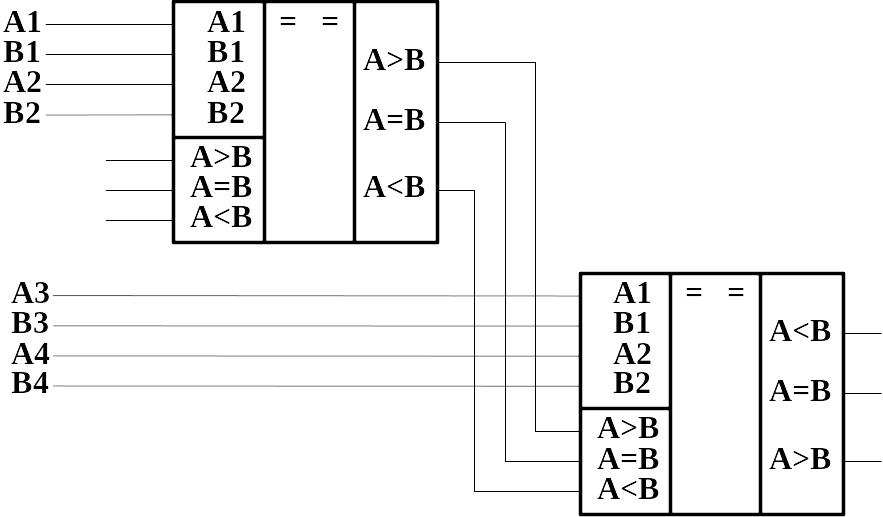

При необходимости наращивания разрядов сравниваемых двоичных чисел компараторы включают каскадно, при этом выходные разряды предыдущего компаратора (сравнение младших разрядов) подают на соответствующие входы последующего (сравнение старших разрядов). Вариант включения двухразрядного компаратора для сравнения четырехразрядных кодов представлен на рисунке 5.21.

Рисунок 5.21 – Двух

разрядный компаратор в каскадном

включении