- •Глава 4 Элементы компьютерной схемотехники

- •Глава 4

- •4.1 Основные характеристики цифровых микросхем

- •4.1.1 Понятие элементов, узлов и устройств в схемотехнике

- •4.1.2 Характеристики логических элементов

- •4.1.1 Понятие элементов, узлов и устройств в схемотехнике

- •4.1.2 Характеристики логических элементов

- •Контрольные вопросы

- •4.2 Логические элементы – диодные, транзисторные

- •4.2.1 Диодные логические элементы

- •4.2.2 Элементы дтл

- •4.2.3 Транзисторная логика (тл)

- •4.2.4 Интегральная инжекционная логика

- •4.2.5 Транзисторно-транзисторные логические элементы

- •4.3 Асинхронные и синхронные rs-триггеры

- •4.4 Триггеры типов jk, t, d и dv

- •4.4.2 Двухступенчатые т-триггеры

4.4 Триггеры типов jk, t, d и dv

4.4.1 Триггеры типа JK

4.4.2 Двухступенчатые Т-триггеры

4.4.3 D-триггеры с динамическим управлением

Используемая литература: Н.П.Бабич, И.А.Жуков Компьютерная Схемотехника. Методы построения и проектирования: Учебное пособие. - «МК-Пресс» Киев, 2004. 576 с.

4.4.1 Триггеры типа JK

Триггером типа JK называется запоминающий элемент с двумя устойчивыми состояниями и информационными входами J (аналог S) и К (аналог R), которые обеспечивают соответственно раздельную установку состояний "1" и "0".

Он функционирует подобно RS-триггеру, однако при совпадении сигналов J = 1 переключается в противоположное состояние, то есть реализует сложение сигналов по модулю два.

Таким образом, JK-триггер не имеет запрещенных комбинаций входных сигналов.

Триггер типа JK является универсальным, поскольку может выполнять функции RS-триггера (при раздельном поступлении сигналов J и К), Т-триггера (при одновременной подаче сигналов J и К), D-триггера (при подаче сигнала от входа J через инвертор на вход К).

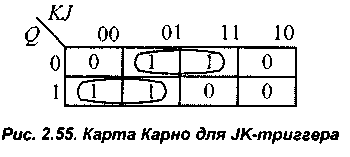

И зменение состояний JK-триггера приведено в табл. 4.7; с помощью карты Карно (рис. 4.34) получаем следующее уравнение для триггера:

Qt+1 = Kt ∙ Qt Jt ∙ Qt (4.7)

Табл. 4.7

Кt |

Jt |

Qt |

Qt+1 |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

Рисунок 4.34-Карта Карно для JK-триггера |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

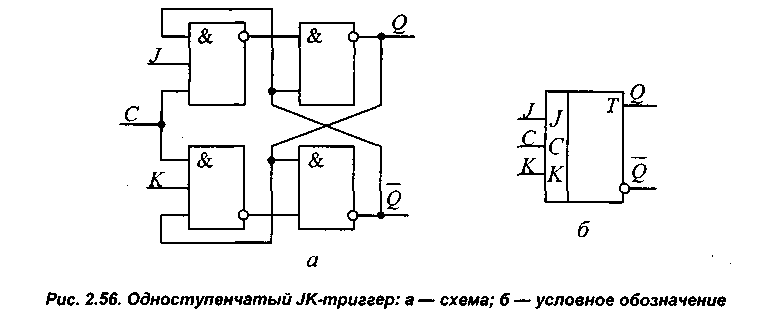

Рисунок 4.35 –Одноступенчатый JK-триггер: а –схема; б –условное обозначение

Для построения одноступенчатого синхронного JK-триггера на элементах НЕ-И требуется заменить в уравнении (4.7) переменные К и J на сочетания СК и JK, после чего выполнить преобразования на основе правил двойной инверсии и правил де Моргана:

Qt+1 = C∙ K∙ Q C∙ J ∙ Q = C∙ K∙ Q ∙ C∙ J ∙ Q (4.8)

Схема одноступенчатого JK-триггера с логическими связями на основе уравнения (4.8) показана на рис. 4.35.

В схемотехнике потенциальных триггеров в основном применяют двухступенчатые синхронные JK-триггеры на элементах НЕ-И (рис. 4.36).

Новая информация снимается с выходов Q* основной М-ступени, а старая — с выходов Q вспомогательной S-ступени.

Из временных диаграмм (рис. 4.36, б) следует:

-при использовании JK-триггера для хранения информации сигналы на входы J и К подаются поочередно;

-при совпадении сигналов на входах J и К реализуется счетный триггер (на практике эти входы часто монтажно объединяются).

Время переключения JK-триггера определяется суммой задержек первой и второй ступеней и составляет tП.ТТ = 7tр.

На выходе S-ступени новая информация возникает после спада сигнала С.

Рисунок 4.36 –Двухступенчатый JK-триггер на элементах НЕ-И:

а –схема; б –временные диаграммы; в –условное графическое обозначение