- •Глава 4 Элементы компьютерной схемотехники

- •Глава 4

- •4.1 Основные характеристики цифровых микросхем

- •4.1.1 Понятие элементов, узлов и устройств в схемотехнике

- •4.1.2 Характеристики логических элементов

- •4.1.1 Понятие элементов, узлов и устройств в схемотехнике

- •4.1.2 Характеристики логических элементов

- •Контрольные вопросы

- •4.2 Логические элементы – диодные, транзисторные

- •4.2.1 Диодные логические элементы

- •4.2.2 Элементы дтл

- •4.2.3 Транзисторная логика (тл)

- •4.2.4 Интегральная инжекционная логика

- •4.2.5 Транзисторно-транзисторные логические элементы

- •4.3 Асинхронные и синхронные rs-триггеры

- •4.4 Триггеры типов jk, t, d и dv

- •4.4.2 Двухступенчатые т-триггеры

4.3 Асинхронные и синхронные rs-триггеры

4.3.1 Определение и назначение триггеров

4.3.2 Классификация триггеров

4.3.3 Динамические параметры и таблицы переходов

4.3.4 Асинхронные RS-триггеры

4.3.5 Синхронные RS-триггеры

Используемая литература: Н.П.Бабич, И.А.Жуков Компьютерная Схемотехника. Методы построения и проектирования: Учебное пособие. - «МК-Пресс» Киев, 2004. 576 с.

4.3.1 Определение и назначение триггеров

Триггер — это запоминающий элемент с двумя устойчивыми состояниями, изменение которых происходит под действием входных сигналов.

Как элемент компьютера, триггер предназначен для хранения одного бита информации, то есть лог. 0 или лог. 1.

Схема триггера обеспечивает запись, считывание, стирание и индикацию хранимой двоичной информации.

На основе триггеров строят типовые функциональные узлы компьютеров — регистры, счетчики, накапливающие сумматоры, а также микропрограммные автоматы.

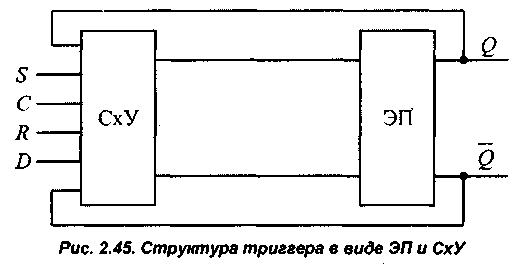

Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и схему управления (СхУ), которая образует входную логику (рис. 4.25).

С

остояние

триггера

определяется

сигналами

на

прямом

Q

и

инверсном

выходах.

выходах.

При положительном кодировании информации высокий уровень напряжения на прямом выходе отображает значение лог. 1 (состояние Q = 1), а низкий уровень — значение лог. О (состояние Q = 0).

Рисунок 4.25 – Структура триггеров виде ЭП и СхУ

Изменение состояния триггера (его переключение) обеспечивается внешними сигналами и сигналами обратной связи на выходе триггера, поступающие на входы СхУ.

Обычно внешние сигналы, как и входы триггера, обозначают латинскими буквами R, S, Т, С, V и др..

В простейших схемах триггеров отдельная СхУ может отсутствовать.

Поскольку функциональные свойства триггеров определяются их СхУ, то названия основных входов переносятся на всю схему триггера.

4.3.2 Классификация триггеров

Триггеры классифицируют по следующим признакам:

логике функционирования (RS, JK, D, Т и др.);

способу записи информации (асинхронные и синхронные);

моменту реакции на тактовый сигнал (статические, динамические);

количеству тактов синхронизации (одно-, двух- и трехтактные);

количеству ступеней (одно- или двухступенчатые триггеры);

составу логических элементов (триггеры на элементах НЕ-И, НЕ-ИЛИ, НЕ-И-ИЛИ и др.).

В соответствии с логикой функционирования различают следующие триггеры:

с раздельной установкой состояний "О" и "1" (RS-триггеры);

с одним информационным входом (D-триггеры);

со счетным входом (Т-триггеры);

универсальные с раздельной установкой состояний "О" и "1" (JK-триггеры);

комбинированные (RST-, RSJK-триггеры);

со сложной входной логикой.

Входы триггеров разделяются на информационные (R, S, Т и др.) и управляющие (С, V).

Информационные (логические) входы предназначены для приема сигналов запоминаемой информации. Названия входных сигналов отождествляют с названиями входов триггера.

Управляющие входы служат для управления записью информации. В триггерах может быть два вида управляющих сигналов: синхронизирующий (тактовый) сигнал С, поступающий на С-вход (тактовый вход) и разрешающий сигнал V, поступающий на V-вход.

По способу записи (приема) информации различают асинхронные и синхронные (тактируемые) триггеры.

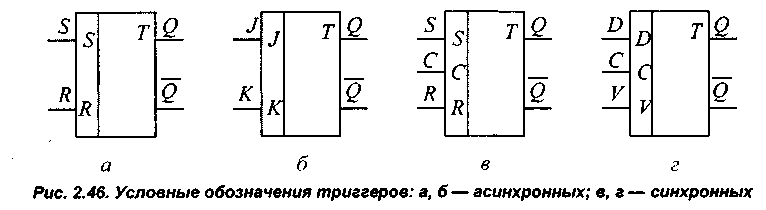

Триггеры, не имеющие С-входа, называются асинхронными (рис. 4.26, а и б).

В асинхронных триггерах запись информации производится в любой момент времени при поступлении сигналов на информационные входы.

Триггеры, имеющие С-вход, называются синхронными (рис. 4.26, в и г)..

В синхронном триггере запись информации возможна при совпадении сигналов на информационном и синхронном входах. Этим объясняется более высокая помехоустойчивость синхронных триггеров в сравнении с асинхронными.

Рисунок 4.26-Условные обозначения триггеров: а,б –асинхронные; в, г -синхронные

На V-входы триггера поступают сигналы, которые разрешают (V = 1) или запрещают (V = 0) запись информации. В синхронных триггерах с V-входом запись информации возможна при совпадении сигналов на информационном, С- и V- входах.

В зависимости от количества тактовых сигналов, необходимых для формирования нового состояния, различают однотактные, двухтактные и многотактные триггеры.

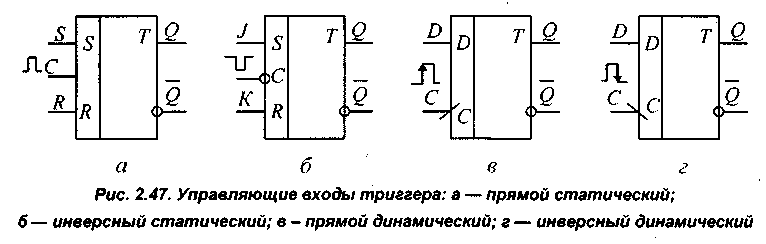

По способу управления записью (моменту реакции на тактовый сигнал) выделяют синхронные триггеры со статическим (по уровню), динамическим (по фронтам) и двухступенчатым управлением.

В асинхронных триггерах запись нуля и единицы возможна в любой момент времени, при этом входной информационный сигнал одновременно является и управляющим.

В синхронных триггерах с управлением по уровню запись информации возможна только в течение длительности тактового сигнала. При этом тактовые сигналы могут быть прямыми (изменяться от нуля к единице) или инверсными (изменяться от единицы к нулю) (рис. 4.27, а и б).

Рисунок 4.26-Управляющие входы триггеров: а -прямой статический;

б –инверсный статический; в –прямой динамический; г –инверсный динамический

При управлении фронтами разрешение на запись информации дается только в момент перепада тактового сигнала от нуля к единице (прямой динамический вход) или от единицы к нулю (инверсный динамический вход).

В другие моменты времени триггер не реагирует на входные информационные сигналы независимо от уровня тактового импульса (рис. 4.26, в и г).

4.3.3 Динамические параметры и таблицы переходов

Динамические параметры

Для триггеров установлены следующие динамические параметры, измеряемые на уровне половины амплитуды сигналов (рис. 4.27):

м

инимальная

длительность

импульса

tc

на

тактовом

входе;

инимальная

длительность

импульса

tc

на

тактовом

входе;минимальное время предварительной установки сигнала на информационном входе tycт;

время восстановления (фиксации) tвос — минимальное время между нарастанием синхросигнала С и спадом информационного сигнала D; для асинхронных триггеров tвос — просто длительность входного сигнала;

время переключения триггера tп.т — временной интервал между

Рисунок 4.27- Временные фронтом входного переключающего сигнала и фронтом сигнала

интервалы на выходе Q или .

Минимальная длительность синхросигнала на входе триггера определяется максимальным временем переключения триггера tc ≥ tп.т max.

В двухступенчатом триггере с однотактной синхронизацией время переключения второй ступени определяется по отношению к спаду синхроимпульса.

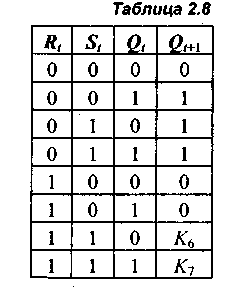

Таблица переходов и логические уравнения RS-триггера

RS-триггером называют запоминающий элемент с раздельными информационными входами для установки его в состояние "0" (R-вход) и в состояние "1" (S-вход).

Название "RS-триггер" образовано от первых букв слов RESET (сброс) и SET (установка).

В таблице переходов RS-триггера (табл. 4.6) приняты обозначения:

Rt, St, Qt, -значения логических переменных в момент времени t на входах R, S и выходе Q;

Qt+1 — состояние триггера после переключения;

К6, К7 — запрещенная комбинация сигналов (неопределенные коэффициенты на тех набо-

рах, где входные сигналы R, и S, одновременно принимают значение единицы).

Табл.

4.6

Табл.

4.6

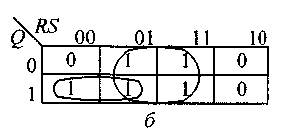

Рисунок 4.28-Карты Карно для RS-триггера

Т аблице переходов соответствует карта Карно (рис. 4.28, а), где значения функции Qt+1 для минтермов Rt, St, Qt и Rt, St, Qt, заменены неопределенными коэффициентами К6 и К7.

Предположив, что комбинации входных сигналов Rt, St = 1 не существует, получим карты Карно для К6 = К7 = 1 (рис. 4.28, б) и К6 = К7 = 0 (рис. 4.28, в).

Из карт Карно получаем логические уравнения асинхронного RS-триггера:

К6

=

К7

= 1 , Qt+1

= St

Qt

(4.1)

Qt

(4.1)

К6

= К7

= 0, Qt+1

=

(St

Qt

).

(4.2)

(St

Qt

).

(4.2)

Логические выражения (4.1) и (4.2) определяют новое состояние триггера Qt+1 в зависимости от старого состояния Qt и входных сигналов Rt и St.

В дальнейшем для простоты индекс t в правой части логического выражения опускается.

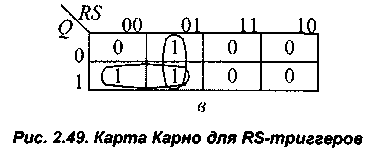

4.3.4 Асинхронные RS-триггеры

Асинхронный RS-триггер на элементах НЕ-И

П реобразуем логическое выражение (4.1) к виду, удобному для реализации на элементах НЕ-И:

Qt+1 = S R ∙ Q = S ∙ R ∙ Q (4.3)

Схема асинхронного RS-триггера на двух элементах НЕ-И с логическими связями на основе выражения (4.3) показана на рис. 4.29, а.

Особенностью этого триггера является инверсное управление по информационным входам, что отражается в условном графическом обозначении.

Из анализа диаграмм работы RS-триггера следует, что элементы НЕ И в схеме переключаются последовательно.

И меется интервал времени, когда на обоих выходах устанавливаются одинаковые сигналы Q = 1 и = 1 (рис. 4.29, в, заштрихованные области) — явление "риск".

Длительность переключения триггера определяется суммой задержек: tП.Т = 2tр.

Длительность входного сигнала определяется из условия ti ≥ tП.Т.

На практике для надежности переключения триггера длительность входного импульса увеличивают на одну задержку, то есть tt = 3tp.

Максимальная (fmax) и рабочая (fp) частоты переключения триггера соответственно равны

fmax = 1/(2tр) и fp = l/(3tp).

Рисунок 4.29-Асинхронный RS-триггер на элементах НЕ-И

а - схема; б – условное обозначение; в – временные диаграммы

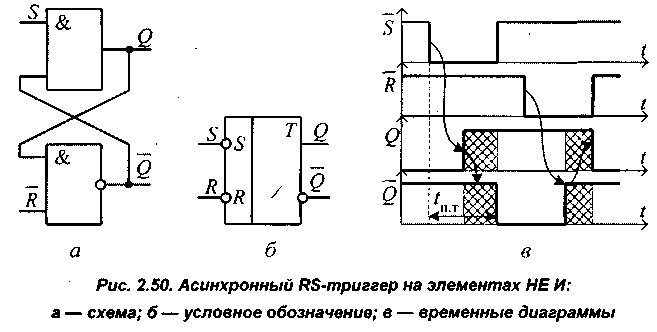

Асинхронный RS-триггер на элементах НЕ-ИЛИ

П реобразуем логическое выражение (4.2) к виду, удобному для реализации на элементах НЕ-ИЛИ:

Qt+1 = R (S Q) = R (S Q) (4.4)

Схема асинхронного RS-триггера на двух элементах НЕ-ИЛИ с логическими связями на основе выражения (4.4) показана на рис. 4.30, а.

Из анализа диаграмм работы RS-триггера следует, что элементы НЕ-ИЛИ в схеме переключаются последовательно.

И меется интервал времени, когда на обоих выходах устанавливаются одинаковые сигналы Q = 0 и Q = 0, — явление "риск" (рис. 4.30, в).

Временные параметры данного триггера аналогичны параметрам триггера, изображенного на схеме рис. 4.30, а.

Рисунок 4.30-Асинхронный RS-триггер на элементах НЕ-ИЛИ

а - схема; б – условное обозначение; в – временные диаграммы

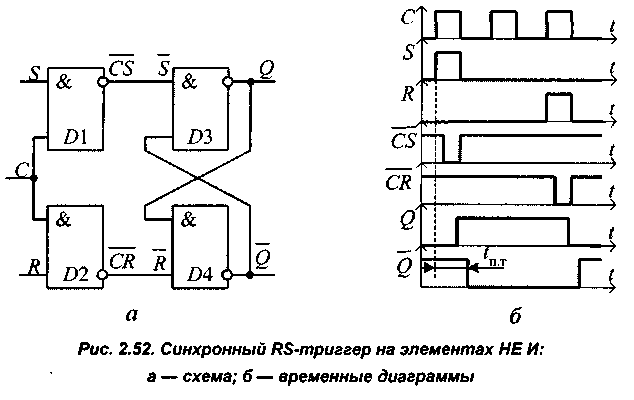

4.3.5 Синхронные RS-триггеры

Синхронный RS-триггер на элементах НЕ-И

Д ля построения синхронного RS-триггера на элементах НЕ-И следует заменить в логическом выражении (4.3) переменные S и R на сочетания CS и CR, где С - синхросигнал:

Qt+1= C S C R Q. (4.5)

Схема синхронного RS-триггера на четырех элементах НЕ-И с логическими связями на основе выражения (4.5) показана на рис. 4.31, а.

Элементы D1 и D2 образуют схему управления с прямыми входами, а элементы D3 и D4 образуют фиксатор (асинхронный RS-триггер).

При значении сигналов CS = 1 на выходе элемента D1 устанавливается лог. 0 и триггер переключается в состояние "1".

При значении сигналов CR = 1 на выход элемента D2 устанавливается лог. 0. и триггер переключается в состояние "0".

Комбинация входных сигналов CSR = 1 запрещена, поскольку приводит к неопределенному состоянию триггера.

Из временной диаграммы (рис. 4.31, б) следует, что время переключения триггера

tп.т = 3tp,

а длительность синхросигнала (с учетом запаса на одну задержку) определяется из условия: tc = 4tp.

Максимальная и рабочая частоты переключения триггера соответственно равны:

fmax = 1/(3tр) и fp = l/(4tp).

Рисунок 4.31-Синхронный RS-триггер на элементах НЕ-И

а - схема; б –временные диаграммы

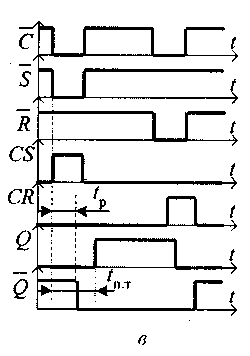

Синхронный RS-триггер на элементах НЕ-ИЛИ

Д ля построения синхронного RS-триггера на элементах НЕ-ИЛИ следует заменить в логическом выражении (4.4) переменные S и R на сочетания CS и CR :

Qt+1 = CR (CS Q) = C R (C S Q) (4.6)

Схема синхронного RS-триггера на четырех элементах НЕ-ИЛИ с логическими связями на основе выражения (4.6) показана на рис. 4.32.

Э лементы

D1

и

D2

составляют

схему

управления

с

инверсными

входами,

а

элементы

D3

и

D4

образуют

фиксатор

(асинхронный

RS-триггер).

лементы

D1

и

D2

составляют

схему

управления

с

инверсными

входами,

а

элементы

D3

и

D4

образуют

фиксатор

(асинхронный

RS-триггер).

Рисунок 4.32-Синхронный RS-триггер на элементах НЕ-ИЛИ

а - схема; б – условное обозначение; в – временные диаграммы

П ри значении сигналов C=0 и S=0 на выходе элемента D2 устанавливается лог.1 (т.e. CS = 1), и триггер переключается в состояние "1".

При значении сигналов C=0 и R = 0 на выходе элемента D1 устанавливается лог. 1 (то есть CR = 1), и триггер переключается в состояние "О".

К омбинация сигналов C=S=R = 0 запрещена, так как приводит к неопределенному состоянию триггера.

Временные параметры такого триггера аналогичны параметрам триггера, изображенного на схеме рис. 4.31.

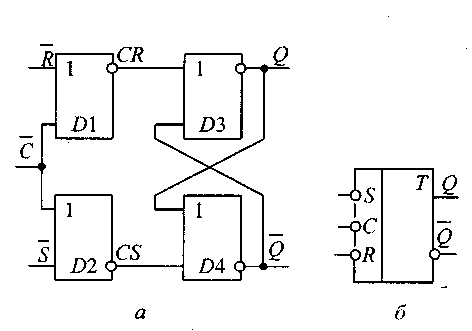

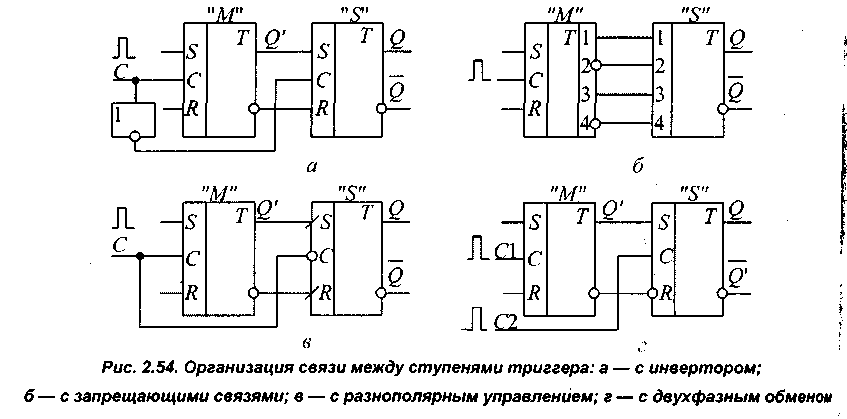

Двухступенчатые RS-триггеры

Двухступенчатые триггеры строятся по способу "M-S" и обеспечивают совмещение двух процессов — одновременной записи новой информации и считывания старой.

Во время действия синхроимпульса С первая ступень "М" (Master— основная) принимает новую входную информацию, а вторая ступень "S" (Slave — вспомогательная) в это же время передает во внешние схемы старую информацию.

После окончания синхроимпульса С информация из первой ступени переписывается во вторую ступень.

При однофазном (однотактном) обмене информацией связь между ступенями реализуется с помощью инвертора (рис. 4.33, а), запрещающих связей (рис. 4.33, б) или разнополярного управления (рис. 4.33, в).

При двухтактном обмене связь между ступенями обеспечивается двумя сериями синхросигналов — С1 и С2 (рис. 4.33, г).

Рисунок 4.33-Организация связи между ступенями триггера:

а -с инвертором; б –с запрещающими связями; в –с разнополярным управлением; г –с двухфазным обменом

КОНТРОЛЬНЫЕ ВОПРОСЫ

Дайте определение триггеру и его назначению.

Чем определяется состояние триггера и чем обеспечивается его изменение.

По каким признакам можно классифицировать триггеры.

Как разделяются входы триггеров.

По способу записи как различают триггеры.

По способу управления записью как различают триггеры.

Расскажите о таблице переходов RS-триггера.

Расскажите об асинхронном RS-триггере на элементах НЕ-И.

Расскажите об асинхронном RS-триггере на элементах НЕ-ИЛИ.

Расскажите об синхронном RS-триггере на элементах НЕ-И.

Расскажите об синхронном RS-триггере на элементах НЕ-ИЛИ.

Расскажите о двухступенчатых триггерах.