- •Компьютерная арифметика и алгоритмическое моделирование арифметических операций

- •Введение

- •Глава 4, подготовленная доцентом о.П. Шафеевой, посвящена вопросам разработки алгоритмических моделей выполнения арифметических операций и моделирования на пэвм спроектированных алгоритмов.

- •Основы двоичной компьютерной арифметики

- •1.1. Позиционные системы счисления

- •Десятичная позиционная система счисления

- •Двоичная позиционная система счисления

- •1.1.3. Восьмеричная позиционная система счисления

- •1.1.4. Шестнадцатеричная позиционная система счисления

- •Перевод чисел из одной позиционной системы счисления в другую

- •1.2.1. Перевод целых чисел

- •1.2.2. Перевод правильных дробей

- •1.2.3. Перевод неправильных дробей из одной системы счисления в другую

- •1.2.4. Частный случай перевода чисел из одной системы счисления в другую

- •1.2.5. Перевод чисел из одной системы счисления в другую с использованием промежуточной двоично-десятичной системы

- •1.3. Представление чисел с фиксированной запятой (точкой)

- •1.4. Представление чисел с плавающей запятой (точкой)

- •1.5. Коды двоичных чисел

- •1.5.1. Прямой код

- •1.5.2. Обратный код

- •1.5.3. Модифицированный обратный код

- •1.5.4. Дополнительный код

- •1.5.5. Модифицированный дополнительный код

- •2. Выполнение арифметических операций с двоичными числами

- •2.1. Сложение (вычитание) двоичных чисел с фиксированной запятой

- •2.1.1. Алгебраическое сложение чисел в дополнительном коде

- •2.1.2. Алгебраическое сложение чисел в обратном коде

- •2.1.3. Переполнение разрядной сетки при сложении чисел

- •2.2. Сложение (вычитание) двоичных чисел с плавающей запятой

- •2.2.1. Метод ускоренного сложения двоичных чисел с запоминанием переносов

- •2.3. Умножение двоичных чисел с фиксированной запятой

- •2.4. Машинные технологии выполнения операции умножения двоичных чисел с фиксированной запятой

- •2.5. Умножение двоичных чисел с плавающей запятой

- •2.6. Методы ускоренного выполнения операции умножения двоичных чисел

- •2.6.1. Метод пропуска такта суммирования

- •2.6.2. Метод анализа сомножителей

- •2.6.3. Метод расшифровки и одновременного умножения на два разряда множителя

- •2.6.4. Метод ускоренного умножения Мак-Сорли

- •2.6.5. Метод ускоренного умножения Лемана

- •2.6.6. Метод умножения с расшифровкой пар разрядов множителя и запоминанием переносов

- •2.7. Деление двоичных чисел с фиксированной запятой

- •2.8. Деление двоичных чисел с плавающей запятой

- •3. Основы десятичной компьютерной арифметики

- •3.1. Машинное кодирование десятичных чисел

- •3.2. Выполнение арифметических операций с десятичными числами

- •3.2.1. Сложение десятичных чисел в эвм

- •3.2.2. Умножение десятичных чисел в эвм

- •3.2.3. Ускорение умножения в -кодах

- •Деление десятичных чисел в эвм

- •4. Алгоритмические модели выполнения арифметических операций

- •4.1. Проектирование универсального алгоритма перевода чисел в разные системы счисления

- •4.2. Моделирование алгоритма сложения двоичных чисел

- •Различные случаи ненормализованных мантисс

- •4.3. Проектирование алгоритма умножения чисел

- •4.5. Проектирование алгоритма деления чисел

- •4.7. Разработка алгоритма вычисления квадратного корня

- •Компьютерная арифметика и алгоритмическое моделирование арифметических операций

4.5. Проектирование алгоритма деления чисел

Для получения частного для чисел с плавающей запятой необходимо разделить мантиссу делимого на мантиссу делителя и вычесть порядок делителя из порядка делимого.

Если исходные числа представлены в форме с фиксированной запятой, то перед началом деления нужно выполнить проверку условия: А < B, т.е. делимое должно быть меньше делителя, иначе произойдет переполнение разрядной сетки (результат больше единицы). На операцию деления чисел с плавающей запятой это ограничение не распространяется. Если мантисса числа А больше мантиссы числа В, нужно перед делением денормализовать МА вправо, а порядок его РА увеличить на единицу, либо в конце деления проверить результат на денормализацию влево. При делении нормализованных чисел может иметь место денормализация результата не более чем на один разряд влево (если делимое больше делителя).

При нахождении порядка результата, а также во время нормализации мантиссы частного может возникнуть переполнение сумматора порядков, которое трактуется так же, как и переполнение сумматора порядков, возникающее при сложении или умножении операндов.

Деление мантисс чисел можно производить при помощи одного из двух алгоритмов: с восстановлением остатка и без восстановления остатка.

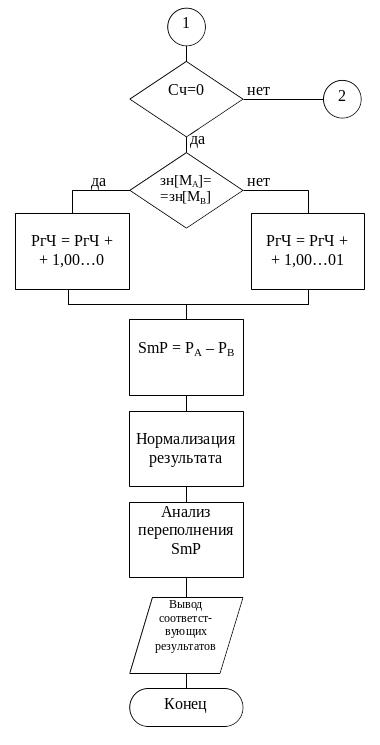

Рассмотрим алгоритм деления без восстановления остатка дополнительных кодов чисел. Структурная схема алгоритма деления чисел с плавающей запятой, представленных дополнительными кодами, показана на рис. 4.5.

Рис. 4.5. Схема алгоритма деления чисел без восстановления остатка

в дополнительных кодах

Рис. 4.5. Схема алгоритма деления чисел без восстановления остатка

в дополнительных кодах (окончание)

В сумматор SmM записывается делимое MA, делитель MB и частное располагаются в соответствующих регистрах РгД и РгЧ. Перед началом деления в младший разряд регистра частного записывается единица, если знак делимого равен знаку делителя, и нуль – в противном случае. Затем выполняется (n-2) цикла, каждый из которых содержит два такта:

1) содержимое сумматора и регистра частного сдвигается на один разряд влево;

2) из сумматора вычитается делитель, если (n-1)-я цифра частного равна единице, в противном случае производится сложение сумматора и содержимого регистра делителя.

Очередная цифра частного равна единице, если знак сумматора равен знаку делителя, и нулю – при различных знаках на сумматоре и регистре делителя.

После выполнения деления нужно выполнить коррекцию, заключающуюся в сложении содержимого регистра частного с поправкой, которая равна 1,00…0 при равенстве знаков делимого и делителя и 1,00…01 – в противном случае.

4.6. Разработка алгоритма ускоренного выполнения операции деления

с анализом за один такт двух разрядов делителя

В ряде случаев при реализации операции деления можно не выполнять арифметических операций в циклах, когда модуль делимого после сдвига оказывается меньше модуля делителя.

Рассмотрим алгоритм, позволяющий сравнивать две цифры после запятой в сумматоре с соответствующими цифрами в регистре делителя. При этом если модуль сумматора меньше модуля делителя, то очередная цифра частного определяется по знаку сумматора. Если сумматор меньше нуля (знак SmM равен единице), то в младший разряд регистра частного записывается единица, в противном случае – нуль.

Различные случаи сочетания цифр сумматора и регистра делителя при двух анализируемых разрядах приведены в табл. 4.3.

Таблица 4.3

Различные случаи сочетания цифр сумматора и регистра делителя

Пара старших цифровых разрядов сумматора |

Пара старших цифровых разрядов регистра делителя |

|

0,10 |

0,11 |

|

0,00 |

См < PгД, арифметической операции нет |

См < PгД, арифметической операции нет |

0,01 |

См < PгД, арифметической операции нет |

См < PгД, арифметической операции нет |

0,10 |

Требуется выполнение арифметической операции |

См < PгД, арифметической операции нет |

0,11 |

Требуется выполнение арифметической операции |

Требуется выполнение арифметической операции |

Из таблицы следует, что при равновероятном появлении единиц и нулей в анализируемых разрядах регистра делителя и сумматора арифметические операции для определения цифр частного должны выполняться в трех случаях из восьми.

Необходимо отметить, что при переполнении сумматора вследствие удвоения очередного частичного остатка в первом такте очередного цикла выполнения операции деления во втором такте этого цикла обязательно выполнение арифметической операции, поскольку модуль сумматора становится меньше единицы.

Тип выполняемой арифметической операции определяется знаком сумматора: производится сложение значения SmM с регистром делителя, если сумматор отрицательный, и вычитание – в противном случае.

Структурная схема алгоритма деления представлена на рис. 4.6.

Деление реализуется в прямых кодах, поэтому знак частного определяется сложением по модулю два знаковых разрядов операндов.

Действия по нормализации результата и анализу переполнения сумматора порядков аналогичны соответствующим действиям, описанным выше.

Следует отметить, что выполнение как ускоренного, так и неускоренного деления невозможно в случае, если при представлении чисел с фиксированной запятой значение делимого по модулю больше значения делителя, поскольку приводит к неустранимому переполнению разрядной сетки.