- •1. Архитектура эвм. Архитектура Фон-Неймана.

- •2. Архитектура эвм. Гарвардская архитектура.

- •3. Обобщенная структурная схема эвм.

- •4.Функциональные узлы эвм. Центральный процессор.

- •5. Функциональные узлы эвм. Устройства основной памяти.

- •6. Функциональные узлы эвм. Шины. Циклы работы шин.

- •14. Классификация сетей.

- •15. Эталонная модель взаимодействия открытых систем.

- •16. Каналы передачи данных.

- •17. Проводные линии связи.

- •18. Беспроводные линии связи. Спутниковые каналы передачи данных.

- •20. Архитектура сети gsm. Транкинговая связь.

- •21. Методы доступа в локальные сети.

- •22. Сети Ethernet и Token Ring.

- •23. Стек протоколов tcp/ip. Транспортный протокол tcp.

- •24. Стек протоколов tcp/ip. Сетевой протокол ip.

- •25. Функции и характеристики сетевых операционных сетей. Информационная безопасность.

- •26. Распределенные вычисления. Основные модели организации.

- •27. Структура территориальных сетей.

- •35. Типовая структура иувс.

- •36. Структуры микропроцессорных иувс.

- •37. Система камак.

- •38. Система модульных приборов National Instruments.

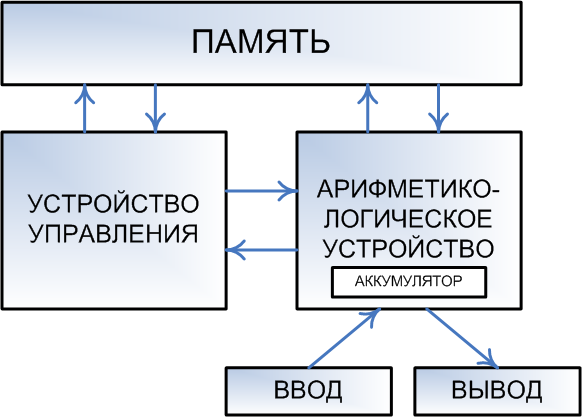

1. Архитектура эвм. Архитектура Фон-Неймана.

Архитектура фон Неймана — широко известный принцип совместного хранения программ и данных в памяти компьютера. Вычислительные системы такого рода часто обозначают термином «машина фон Неймана», однако соответствие этих понятий не всегда однозначно. В общем случае, когда говорят об архитектуре фон Неймана, подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных.

Принципы фон Неймана

Принцип двоичного кодирования

Согласно этому принципу, вся информация, поступающая в ЭВМ, кодируется с помощью двоичных сигналов (двоичных цифр, битов) и разделяется на единицы, называемые словами.

Принцип однородности памяти

Программы и данные хранятся в одной и той же памяти. Поэтому ЭВМ не различает, что хранится в данной ячейке памяти — число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

Принцип адресуемости памяти

Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Отсюда следует возможность давать имена областям памяти, так, чтобы к хранящимся в них значениям можно было бы впоследствии обращаться или менять их в процессе выполнения программы с использованием присвоенных имен.

Принцип последовательного программного управления

Предполагает, что программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определенной последовательности.

Принцип жесткости архитектуры

Неизменяемость в процессе работы топологии, архитектуры, списка команд.

Компьютеры, построенные на принципах фон Неймана

Манчестерский Марк I (прототип — Манчестерская малая экспериментальная машина). Манчестерский университет, Великобритания, 21 июня 1948 года;

EDSAC. Кембриджский университет, Великобритания, 6 мая 1949 года;

BINAC. США, апрель или август 1949 года;

CSIR Mk 1. Австралия, ноябрь 1949 года;

SEAC. США, 9 мая 1950 года

2. Архитектура эвм. Гарвардская архитектура.

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются: 1. Хранилище инструкций и хранилище данных представляют собой разные физические устройства. 2. Канал инструкций и канал данных также физически разделены.

Архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете.

Классическая гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

выборку двух операндов,

выбор инструкции и её выполнение,

и, наконец, сохранение результата.

Идея, реализованная Эйкеном, заключалась в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие компьютера.

В Гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не требуется иметь общими. В частности, ширина слова, тайминги, технология реализации и структура адресов памяти могут различаться. В некоторых системах инструкции могут хранится в памяти только для чтения, в то время как, для сохранения данных обычно требуется память с возможностью чтения и записи. В некоторых системах требуется значительно больше памяти для инструкций, чем памяти для данных (поскольку данные обычно могут подгружатся с внешней или более медленной памяти). Такая потребность увеличивает битность (ширину) шины адреса памяти инструкций по сравнению с шиной адреса памяти данных.

Модифицированная гарвардская архитектура

Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи команд и данных на кристалле процессора последний должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Способом решения этой проблемы стала идея использовать общие шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной Гарвардской архитектурой.

Такой подход применяется в современных сигнальных процессорах. Ещё дальше по пути уменьшения стоимости пошли при создании однокристалльных ЭВМ — микроконтроллеров. В них одна шина команд и данных применяется и внутри кристалла.

Разделение шин в модифицированной Гарвардской структуре осуществляется при помощи раздельных управляющих сигналов: чтения, записи или выбора области памяти.

Расширенная гарвардская архитектура

Часто требуется выбрать три составляющие : два операнда и инструкцию (в алгоритмах цифровой обработки сигналов это наиболее распространенная задача в БПФ и КИХ, БИХ фильтрах). Для этого существует кэш-память. В ней может храниться инструкция — следовательно, обе шины остаются свободными и появляется возможность передать два операнда одновременно. Использование кэш-памяти вместе с разделёнными шинами получило название «Super Harvard Architecture» («SHARC») — расширенная Гарвардская архитектура.

Примером могут служить процессоры «Analog Devices»: ADSP-21xx — модифицированная Гарвардская Архитектура, ADSP-21xxx(SHARC) — расширенная Гарвардская Архитектура.