- •Теоретические вопросы: Вопрос № 1 Состав электронно-вычислительных машин. Структурная схема. Назначение узлов и блоков эвм. Характеристики эвм.

- •Вопрос № 2 Интерфейсы пэвм ibm классификация интерфейсов. Дать определение шин. Охарактеризовать шины в зависимости от их назначения, разрядности и направленности.

- •Вопрос № 4 Структурная схема материнской платы пэвм «Агат». Назначение узлов и блоков. Характеристика интерфейса.

- •Встроенный интерфейс ввода-вывода

- •Назначение узлов и блоков

- •Принцип работы

- •Технические характеристики

- •Вопрос № 5 Управление вычислительным процессам в эвм. Взаимодействие устройств эвм. Характеристика машинных команд.

- •Вопрос № 6 Составить схему асинхронного триггера r-s типа. Пояснить принцип ее действия в зависимости от состояния входных сигналов. Привести условное обозначение триггера r-s типа.

- •Р исунок 3. Электрическая схема, временные диаграммы и условное графическое обозначение однотактного асинхронного триггера построенного на логических элементах и-не.

- •Вопрос № 7 Структура машинных команд эвм. Назначение составляющих машинных команд. Характеристика одноадресных и двухадресных команд. Алгоритм работы процессора при их обработке.

- •Вопрос № 8 Рассказать о системах счисления. Дать определение основания систем счисления. Правила перевода из одной системы счисления в другую. Перечислить достоинства и недостатки.

- •Вопрос № 9 Адресация информации и обработка адресов в эвм. Непосредственная, прямая регистровая, косвенная, индексная, относительная, адресация.

- •Вопрос №15. Устройство управления эвм. Структурная схема. Назначение узлов.

- •Вопрос №19. Арифметико-логическое устройство эвм. Обобщенная структурная схема алу. Классификация алу.

- •Вопрос №21. Операционный блок для сложения и вычитания двоичных чисел с фиксированной точкой. Назначение узлов и блоков. Алгоритм выполнения операций сложения и вычитания.

- •Вопрос №22. Оперативные запоминающие устройства на основе интегральных схем. Условное обозначение и структурная схема зу, организация поиска информации.

- •Вопрос №23. Операционный блок для умножения двоичных чисел с фиксированной точкой. Назначение узлов и блоков. Алгоритм выполнения операции умножения.

- •Вопрос №24. Структурная схема материнской платы ibm pc. Назначение узлов и блоков, принцип действия.

- •Вопрос №25. Операционный блок для деления двоичных чисел с фиксированной точкой без восстановления остатка. Назначение узлов и блоков. Алгоритм выполнения операции деления.

- •Вопрос №26. Схема управления режимами работы в пэвм «Агат». Назначение узлов и блоков, схемы, принцип действия.

- •Вопрос №27. Операционный блок для деления двоичных чисел с фиксированной точкой с восстановлением остатка. Назначение узлов и блоков. Алгоритм выполнения операции деления.

- •Вопрос №28. Статическая и динамическая память. Основное назначение сверхоперативного запоминающего устройства и кэш памяти. Характеристика кэш памяти.

- •Вопрос №29. Операционный блок десятичного сумматора. Структурная схема. Назначение узлов и блоков. Последовательность микроопераций при выполнении схемой алгоритма сложения и вычитания чисел.

- •Вопрос №30. Система прерываний микропроцессора. Алгоритм работы микропроцессора при обработки сигналов маскируемого и немаскируемого прерываний.

- •Вопрос №31. Структура операционных блоков для операций над двоичными числами с плавающей точкой. Структурная схема операционного блока выравнивания порядков двоичных чисел с плавающей точкой.

- •Вопрос №32. Микропроцессоры. Адресация и структура команд. Назначение регистров общего назначения и специальных регистров.

- •Вопрос№33. Дополнительный код положительных и отрицательных чисел. С какой целью он используется в эвм. Представление чисел в эвм с фиксированной точкой и плавающей точкой.

- •Вопрос№34. Архитектура современных пэвм. Логическая структура. Назначение узлов и блоков. Характеристика внутреннего и внешнего интерфейса.

- •Вопрос№35. Взаимодействие процессора и запоминающего устройства в процессе выполнения программы. Рассмотреть различные варианты машинных команд

- •Вопрос№37 Персональная эвм. Логическая структура. Назначение узлов и блоков. Характеристика внутреннего и внешнего интерфейса.

- •Вопрос №38. Правила перевода целых и дробных чисел из 10-й системы счисления в 2-ю, 8-ю, 16-ю и из 2-й, 8-й, 16-й в 10-ю систему счисления.

- •Вопрос №39. Поколения эвм. Идентичность и различие эвм всех поколений. Основные характеристики и особенности каждого поколения.

- •Вопрос№40. Распределение адресного пространства пэвм «агат» по функциональному назначению. Алгоритм работы процессора после включения питания.

- •Вопрос№42. Схемное и микропрограммное управление по эвм. Характеристики, достоинства и недостатки схемного и микропрограммного управления.

- •Вопрос№48. Архитектура процессоров, разработанных с использованием суперскалярной технологии. Алгоритм выполнения процессором двух команд одновреммено.

Вопрос №15. Устройство управления эвм. Структурная схема. Назначение узлов.

Принцип работы.

Выполнение команды центральным устройством управления (ЦУУ) процессора проводится обычно в такой последовательности:

-выборка команды из ОП;

-формирование исполнительных адресов операндов по информации, содержащейся в коде команды;

-выборка операндов из ОП;

-выполнение действий в арифметическо-логических блоках;

-отсылка результата выполнения операции в ОП.

Все действия, связанные с преобразованием кодов команд в наборы управляющих сигналов (УС) и исполнительные адреса, выполняются непосредственно в ЦУУ. В ЦУУ входят:

Блок выборки команд и данных(БВКиД). Он предназначен для приёма команды, хранения ёё до окончания операции, расшифровки кода операции, модификации адресов, формирования адреса следующей команды, выдачи адресов операндов и следующий команды в ОЗУ, для хранения кодов операндов, принимаемых из ОЗУ и выдача в ОЗУ адреса, по которому производится запись результата выполнения операции.

Блок центрального управления(БЦУ). Вырабатывает необходимую последовательность УС при выполнении каждой команды программы для АЛУ и других устройств ЭВМ.

Пульт управления(ПУ). Обеспечивает управление работой ЭВМ со стороны оператора, визуальный контроль состояния отдельных устройств и проведение профилактических мероприятий.

Блок прерываний(БП). Служит ля реализации запросов на прерывание в соответствии с их приоритетами.

Блок управления ОП(БУОП). Обеспечивает обмен информации с ОП не только процессором, но и всеми каналами ввода-вывода(КВВ).

Блок защиты памяти(БЗП). Предназначен для предотвращения искажения любой информации, хранящейся в ОП, по записи и её возможного искажения вследствие возможных ошибочных обращений к ОП при считывании.

Блок внешних связей(БВС). Обеспечивает обмен управляющей информацией с другим процессором при построении и работе мультипроцессорной системы.

Блок таймеров(БТ). Служит для подсчёта временных интервалов и управления работой процессора в системе по принимаемым временным соотношениям.

Б

лок

синхронизации(БС). Обеспечивает жёсткую

синхронизацию работы всех блоков и

устройств процессора.

лок

синхронизации(БС). Обеспечивает жёсткую

синхронизацию работы всех блоков и

устройств процессора.

Вопрос №16. Дать определение регистра. Нарисовать схему запоминающего регистра и пояснить принцип её действия. Привести условное графическое обозначение запоминающего регистра на электрических схемах.

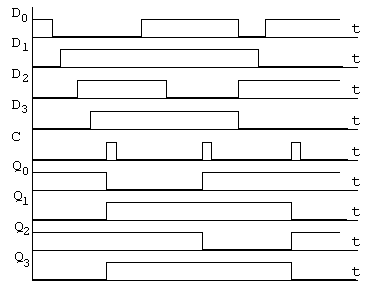

Регистром называется функциональный узел, предназначенный для записи, хранения и выдачи многоразрядного кода двоичного числа. Регистр хранения информации принимает и выводит код только в параллельном формате и не преобразует код. В большинстве случаев регистры хранения строятся на D-триггерах.

На вход регистра подаётся код числа в двоичном формате. Приём кода происходит при поступлении синхроимпульса С на вход регистра. При поступлении сигнала С триггеры в регистре переключатся в нулевое или единичное состояние, в зависимости от сигналов D0, D1, D2, D3, и будут находится в этом состоянии до прихода очередного синхроимпульса и изменения информационных сигналов.

Условное графическое обозначение регистра на электрических схемах.

Вопрос №17. Дать определение микропроцессора в зависимости от его назначения. Нарисовать структурную схему микропроцессора и пояснить принцип её действия.

Микропроцессор—программно-управляемое устройство обработки цифровой информации. По назначению микропроцессоры делят на универсальные и специализированные. Универсальные позволяют совместно с другими БИС создавать ЭВМ широкого диапазона применений. Специализированные не требуют развитого программного обеспечивания.

Устройство управления—совокупность блоков и узлов процессора, обеспечивающая координирование работы всех устройств ЭВМ и управление ими для всех режимов работы.

Регистр команд—часть устройства управления, хранит команду, пока её выполняет процессор.

Дешифратор команд—вторая часть устройства управления, расшифровывает операционные и адресные части команд.

Схема приращения (СхП) используется для хранения части адреса.

Регистр признаков (РПР) хранит признак результата.

Аккумулятор(А)—используется в процессоре, использующим одноадресные команд. Хранит второе число для выполнения действия.

Буферные регистры(БР1, БР2)—нужны для временного хранения данных.

Указатель стека (УС)—специальный регистр, который хранит начальный адрес стековой памяти. Стековая память—часть ОП, работает по специальному признаку. Всё записывается по одному и тому же адресу, а предыдущая информация перезаписывается в адрес на 1 больше.

Вопрос №18. Дать определение дешифратора в зависимости от его назначения. Составить схему дешифратора на логических элементах. Пояснить принцип действия дешифратора и привести его графическое изображение на электрических схемах.

Дешифратор – функциональный узел, преобразующий код двоичного числа в управляющий сигнал логического уровня, который возникает на одном из его выходов. Номер выхода соответствует значению кода поданному на входы. Если количество выходов N=2m , где m – количество информационных входов, то дешифратор называется полным. Входы и выходы дешифраторы могут быть как прямыми так и инверсными. Активным уровнем сигнала для прямого входа является высокий, а для инверсного – низкий. Если выход прямой, то при его активизации на нем действует высокий уровень напряжения, на остальных выходах – низкий. На активизированном инверсном выходе действует низкий уровень напряжения, а на остальных – высокий. Дешифраторы строятся на элементах И, имеющих такое количество входов сколько и информационных входов дешифратора. Часто дешифраторы делаются синхронными. Это значит, что выходные сигналы появляются только при наличии дополнительного управляющего сигнала. Такой сигнал называется синхронизирующим, он может быть как высокого, так и низкого уровня.