- •Аппаратные и программные средства эвм

- •Двоичная арифметика

- •Коды для представления чисел

- •Представление числовой информации (??? Заголовок похож на предыдущий заголовок).

- •Кодирование чисел и алфавитно-цифровой информации.

- •Лекция №3. Представление информации физическими сигналами

- •Элементы и типовые узлы эвм

- •1. Триггеры

- •Синхронный rs-триггер

- •2. Регистры

- •Параллельный регистр

- •Последовательный регистр

- •3. Счетчики

- •Лекция №4. Комбинационные схемы (кс)

- •1. Дешифратор.

- •2. Шифратор.

- •3. Компаратор

- •4. Сумматор

- •5. Мультиплексор

- •6. Демультиплексор

- •Лекция№5. Теория автоматов

- •Классификация автоматов.

- •Способы построения схем автоматов

- •1. Построение схем автоматов с жесткой логикой.

- •Достоинства и недостатки автоматов с жесткой логикой.

- •2. Построение схем автоматов с микропрограммной логикой

- •Достоинства и недостатки автоматов с микропрограммной логикой.

- •3. Построение схем автоматов с программной логикой.

- •Достоинства и недостатки автоматов с программной логикой.

- •Лекция №6. Основные характеристики эвм

- •Запоминающие устройства (зу) Иерархия запоминающих устройств

- •Классификация методов доступа к зу

- •Характеристики зу

- •Классификация зу:

- •Оперативные запоминающие устройства (озу)

- •Постоянные запоминающие устройства (пзу)

- •Пзу и система bios

- •Центральный процессор эвм

- •Основные характеристики цп

- •Лекция №7. Функциональная и структурная организация типового цп

- •Важнейшие этапы этого машинного цикла

- •Виды адресаций

- •Шины эвм

- •Лекция №8. Микропроцессоры и микроконтроллеры

- •Режимы и организация ввода-вывода в эвм

- •Лекция №9. Стандартные внешние интерфейсы эвм

- •Параллельный интерфейс Centronix

- •Последовательный интерфейс rs-232

- •Последовательный интерфейс usb

- •Лекция №10. Особенности организации рабочих станций и серверов

- •Многопроцессорные и многомашинные системы

- •Телекоммуникационные и компьютерные сети. Локальные и глобальные сети. Топологии и стандарты локальных сетей.

- •Стандарты локальных сетей:

- •Модель сетевого взаимодействия osi

- •Семейства протоколов для локальных и глобальных сетей. Способы адресации и маршрутизации в компьютерных сетях.

- •Методы маршрутизации

1. Дешифратор.

Дешифраторы (ДШ) — это комбинационные схемы с n входами и у=2n выходами.

Рис.6.

Дешифратор

Рис.6.

Дешифратор

Запишем таблицу истинности для дешифратора с тремя входами (n=3). Если число входов n=3, то число выходов у=2n=23=8.

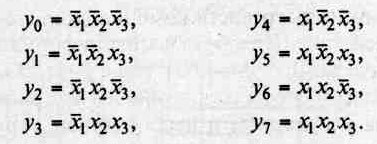

Логические зависимости дешифратора:

Структурная схема дешифратора (а) с тремя входами и обозначение дешифратора на принципиальных электрических схемах (б):

2. Шифратор.

Шифратор (ШР) решает задачу, обратную схемам ДШ, т. е. по номеру входного сигнала формирует однозначную комбинацию выходных сигналов.

Назначение шифратора – выдавать на выходе информацию о том, на какой из входов подан сигнал, используя при этом кодовое слово, содержащее минимум двоичных разрядов.

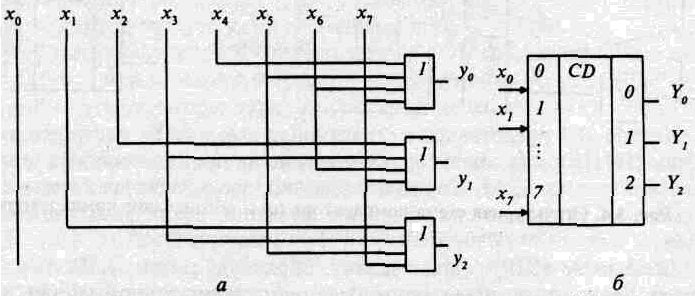

Рассмотрим структурная схема шифратора (а) с восемью входами и обозначение шифратора на принципиальных электрических схемах (б):

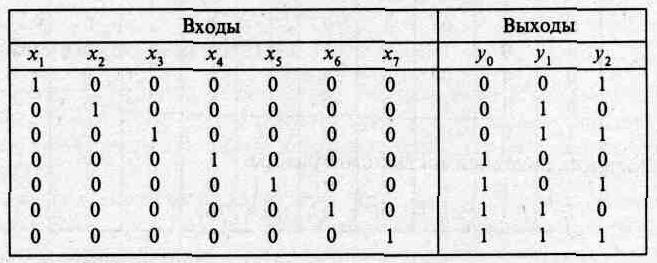

Таблица истинности шифратора

Логические зависимости шифратора:

Обратим внимание, что таблицы истинности у шифратора и дешифратора во многом похожи. Только входы и выходы в них поменялись местами. Состояния входов у шифратора содержат только по одному единичному элементу. Другие произвольные комбинации входов недопустимы.

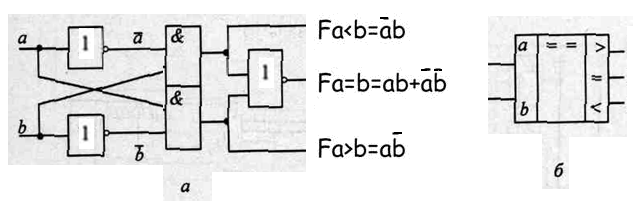

3. Компаратор

Компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А>В или А<В.

Структурная схема компаратора (а) и обозначение компаратора на принципиальных электрических схемах (б):

Компараторы имеют три выхода: Fa > b, Fa = b, Fa < b.

Таблица истинности компаратора

4. Сумматор

Сумматор — это узел ЭВМ, в котором суммируются коды чисел. Как правило, любой сумматор представляет собой комбинацию одноразрядных сумматоров.

Сумматоры классифицируются по разным признакам:

1. В зависимости от системы исчисления:

Двоичные

Двоично-десятичные

Десятичные

Прочие (пример: амплитудные)

2. По количеству одновременно обрабатываемых разрядов складываемых чисел:

Одноразрядные

Многоразрядные

3. По числу входов и выходов одноразрядных двоичных сумматоров:

Четвертьсумматоры, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

Полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом ≈ перенос в следующий (более старший разряд);

Полные одноразрядные двоичные сумматоры, характеризующиеся наличием трех входов, на которые подаются одноименные разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом ≈ перенос в следующий (более старший разряд).

4. По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

Последовательные, в которых обработка чисел ведется поочередно, разряд за разрядом, на одном и том же оборудовании;

Параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется свое оборудование.

Сумматоры разделяют по принципам построения на накапливающего и комбинационного типа. Сумматоры накапливающего типа строят на сложных JKRS-триггерах, дополняя их выходы достаточно сложными схемами формирования и распространения переносов.

Для построения сумматоров чаще применяют сумматоры комбинационного типа. Принципы построения и работы такого сумматора вытекают из правил сложения двоичных цифр.

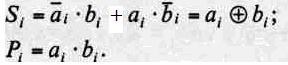

Структурная схема (а) и обозначение полусумматора(б)

Таблица истинности полусумматора:

Логические зависимости полусумматора:

Логические зависимости полусумматора Si и компаратора очень похожи, так как они инверсны по отношению друг к другу.

Уравнения, положенные в основу полусумматора, используются и при построении многоразрядных сумматоров.

Структурная схема одного разряда комбинационного сумматора (а); условное изображение (б):

Видно, что структурная схема i-го разряда сумматора требует включения в свой состав трех схем сравнения для формирования разрядной суммы и шести схем совпадения.

Таблица истинности сумматора:

Таблица истинности сумматора, учитывающего сигналы переноса, отличается от таблицы истинности полусумматора дополнительным входом р — переносом из предыдущих разрядов.

Логические зависимости:

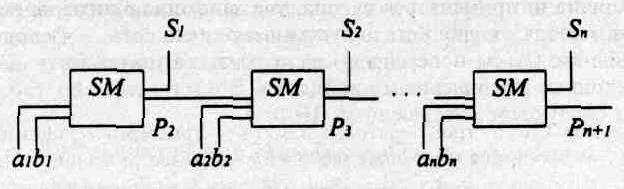

Структурная схема многоразрядного комбинационного сумматора: