- •Введение

- •1. Разработка структуры микропроцессорной системы

- •1.1 Состав микропроцессорной системы

- •1.2 Обоснование выбора способа организации связей между элементами мпс

- •2. Разработка функциональной схемы

- •2.1 Описание заданного типа микропроцессора

- •2.2 Проектирование модуля озу

- •2.3 Проектирование модуля пзу

- •РРис.3.

- •2.4 Обмен информации внутри ядра мпс

- •3. Описание и разработка схемы ввода - вывода

- •4. Разработка схемного и программного вывода слова на элементах индикации

- •5. Разработка электрической принципиальной схемы

- •6. Описание системы команд и формата команд заданного микропроцессора

- •6.1 Команды заданного микропроцессора:

- •Заключение

- •Литература

1.2 Обоснование выбора способа организации связей между элементами мпс

Для организации связей между элементами МПС выбрана общая системная шина. Данный способ имеет более простую организацию связей между элементами МПС, а также позволяет экономить на материале, так как используется только одна шина.

2. Разработка функциональной схемы

2.1 Описание заданного типа микропроцессора

Микропроцессор i8086/i8088 принадлежит к 16-разрядным процессорам первого поколения. Большая интегральная схема i8086 с геометрическими размерами 5,5x5,5 мм имеет 40 контактов, содержит около 29 000 транзисторов и потребляет 1,7 Вт от источника питания +5 В, тактовая частота составляет 5; 8 или 10 МГц.

Микропроцессор выполняет операции над 8 - и 16-разрядными данными, представленными в двоичном или двоично-десятичном виде, может обрабатывать отдельные биты, а также строки или массивы данных. Он имеет встроенные аппаратные средства умножения и деления.

Микропроцессор имеет внутреннее сверхоперативное запоминающее устройство (СОЗУ) емкостью 14x16 байт. Шина адреса является 20-разрядной, что позволяет непосредственно адресовать 220 = 1 048 576 ячеек памяти (1 Мбайт).

Пространство адресов ввода/вывода составляет 64 Кбайт. В БИС i8086 реализована многоуровневая векторная система прерываний с количеством векторов до 256. Предусмотрена также организация прямого доступа к памяти, по которому микропроцессор прекращает работу и переводит шины адреса, данных и управления в высокоимпедансное состояние.

Среднее время выполнения команды занимает 12 тактов. Особенностью i8086 является возможность частичной реконфигурации аппаратной части для обеспечения работы в двух режимах - минимальном и максимальном. Режимы работы задаются аппаратно. В минимальном режиме, используемом для построения однопроцессорных систем, микропроцессор самостоятельно формирует все сигналы управления внутренним системным интерфейсом. В максимальном режиме, используемом для построения мультипроцессорных систем процессор формирует на линиях состояния двоичный код, который зависит от типа цикла шины. В соответствии с этим кодом системный контроллер К1810ВГ88 формирует сигналы управления шиной. Контакты, которые освободились в результате кодирования информации, используются для управления мультипроцессорным режимом. При использовании арифметического сопроцессора необходимо выбирать максимальный режим.

Токи потребления и параметры выходных сигналов характеризуются значения:

ICC max = 340/350/360 mA

VOL max = 0,45 B при IOL = 2,5 mA

VOL max = 0,40 B при IOL = 2,5 mA

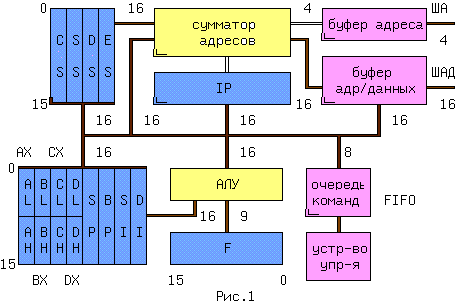

Устройство управления декодирует байты программы и управляет работой операционного устройства и шинного интерфейса. Операционное устройство МП состоит из 4-х шестнадцатиразрядных регистров общего назначения: РОН (AX,BX,CX,DX), из 4-х регистров указателей (адресных регистров SP,BP,SI, DI) и арифметико-логического устройства (АЛУ) с регистром признаков операций (флагов F).

РОН (Регистры Общего Назначения) служат для хранения промежуточных результатов операций, т.е. операндов. Помимо общих, каждый из этих регистров имеет и некоторые специальные функции, о которых будет сказано далее. Каждый РОН может раcсматриваться, как состоящий из двух независимых 8-ми разрядных регистров AH, AL, BH, BL, CH, CL и DH, DL.

Адресные регистры хранят 16-ти битовые указатели (адреса) на области памяти. В SP (StackPointer) находится текущий адрес "вершины стека" - специально организованной области памяти, которая будет описана далее. Регистр BP(Base Pointer) хранит любойбазовый адрес в области стека. Два регистра SI и DI (Source и Destination Index) адресуют области памяти, называемые источником и приемником данных.

Шинный интерфейс его узлы отмечены двойной чертой, выполняет операции обмена между МП и памятью или внешними устройствами. В сегментных регистрах CS,SS,DS,ES хранятся указатели на 64-х килобайтные области памяти называемые сегментами. Значения этих указателей могут перекрываться. Адрес байта в ячейке памяти получается суммированием содержимого одного из сегментных регистров и одного из регистров (SP,SI,DI,IP). Например адрес текущего байта программы, извлекаемого из памяти определяется суммой адресов, хранящихся в регистре кодового сегмента (CS) и указателе команд (IP). В регистре IP хранится 16-битовый адрес байта в кодовом сегменте к которому микропроцессор должен обратиться. Подробнее об этом будет сказано далее. Связь с внешними устройствами осуществляется через специальные тристабельные схемы с повышенной нагрузочной способностью и называемые буферами.

Текущий байт программы направляется в очередь команд: шесть однобайтовых регистров расположенных конвейером (по принципу "первым вошел - первым вышел" или FIFO ). Конвейер позволяет одновременно выполнять команду из очереди и загружать следующую, повышая производительность МП.

Буферные тристабильные элементы увеличивают мощность сигналов до стандартных значений ТТЛ.

ZF - флаг/признак нулевого результата (Zero), устанавливается в 1, если получен нулевой результат, иначе (ZF)=0.

CF - флаг переноса (Carry) устанавливается, если в результате выполнения операции из старшего бита переносится или занимается 1 при сложении или вычитании, иначе (CF)=0. На CF влияют также команды сдвига и умножения.

SF - флаг знака результата (Sign) равен единице, если результат отрицательный, т.е. он дублирует старший знаковый бит результата.

PF - флаг четности (Parity). (PF)=1, если сумма по модулю два всех битов результата равна нулю (число единичных битов - четное).

AF - флаг дополнительного переноса (Auxiliary) устанавливается, если есть перенос из старшего бита младшей тетрады (бит D3) в младший бит старшей тетрады (бит D4). Используется в операциях над упакованными BCD числами.

OF - флаг переполнения (Overflow) устанавливается, когда результат операции превысит одно- или двухбайтовый диапазон чисел со ЗНАКОМ, а также в некоторых других случаях. Другое определение: (OF)=1, если перенос/заем в старший бит результата не равен переносу/заему из старшего бита.

Микропроцессорный модуль является по сути основным узлом микропроцессорной системы. В его состав входит сам микропроцессор, тактовый генератор, буферные регистры, шинный формирователь, дешифратор адреса контроллера прерываний и контроллер прерываний.

Электрическая функциональная схема микропроцессорной системы представлена на втором листе графической части.