- •1.Процессоры

- •2.Многофункциональное алу

- •3.Управляющие автоматы с жесткой логикой

- •4.Управл автоматы с мпу

- •5.Организация модулей пзу

- •6.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •7.Организация динамических модулей дозу

- •8.Вс классификация по Флинну

- •9.Машины упр потоками данных(df-машины)

- •10. Общие полож.Risc-проц. Берклинская арх.

- •11. Общие полож.Risc-проц. Старнфордсая структура

- •12. Кэш память.

- •13. Виртуальная память.

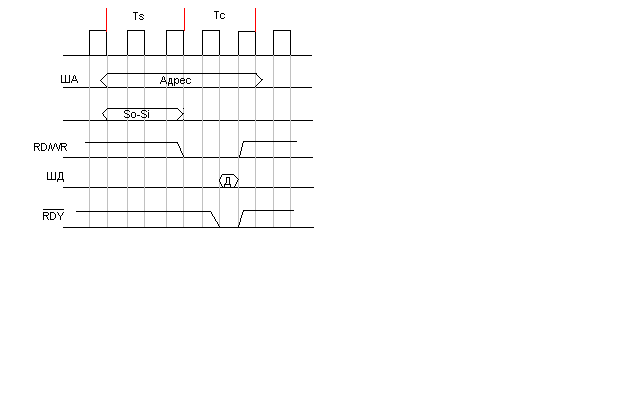

- •14.Синхр способ продкл ву к см

- •15. Асинхр способ продкл ву к см

- •16. Требования к кодам команди способы кодирования.

- •17. Организация эвм типа ibm pc/at

- •18. Процессор Pentium

- •19. Процессор Pentium II (Pentium Pro)

- •20. Процессор Pentium VI

- •21. Структура вс с общей шиной, каждый с каждым, дублированная шина, кольцо

- •22. Структура вс древовидная, почтового ящика, многопортового озу

- •23. Архитектура Сммр,Сvмр.

- •24. Архитектуры вс типа Сm, BlueChip, Минимакс, Сумма.

- •25. Прогр контр прерываний.

- •26. Контролер пдп.

- •27. Ппи

- •27.М/о ч/з ппи.

- •28. Однокристальн эвм

- •29. Покдл модулей дозу к см(прозр рег).Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

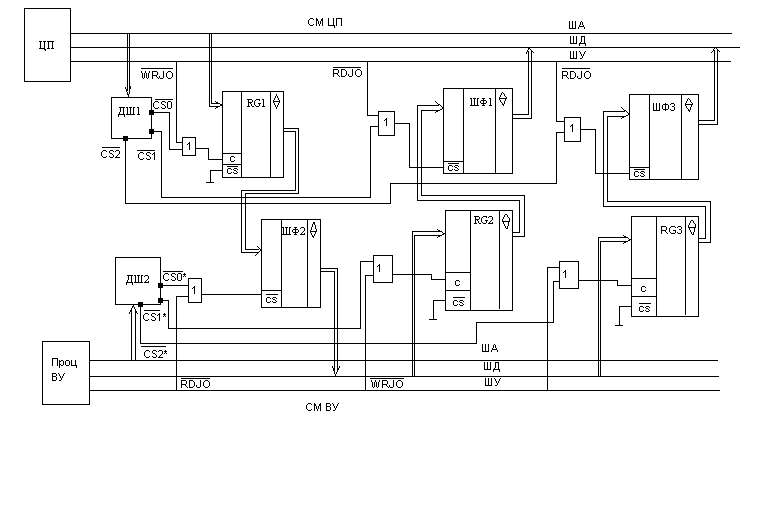

15. Асинхр способ продкл ву к см

В Рг3 храниться слово состояния ВУ (ССВУ).

При асинхр способе обмена ЦП в программно доступном RG1 записывает команду для ВУ. После этого он периодически обращается к CS2 и и ч/з ШФ3 считывает ССВУ. ВУ получив команду от ЦП приступает к ее выполнению и сооьщает об этом записью определенного кода в регистр 3 для ЦП (записывается ССВУ). После этого команда выполняется ВУ, результат записывается в Рг 2, затем записывается другое ССВУ в Рг3, в котором ВУ говорит ЦП, что результат получен и ЦП может забрать данные из Рг2.

АСОИ исключает повторное считывание той же самой инфы, ускоряет процесс обмена. Биты Рг состояния иногда называют битами квитирования, т.е. битами сопровождения инфы.

-----------------------------------------------------------------------------------------------------

16. Требования к кодам команди способы кодирования.

Код команды должен соотв требованиям:

1)Указывать на вид операции

2)Указывать на месторасположение одного (или неск) операндов участв в выполнении команды.

3)Указывать на адрес расположения результат выполнения

4)Указывать на адрес выполнения след команды

Способы кодирования:

1)Горизонтальное кодирование. Каждому разряду Рг микрокоманд соответствует фиксированное управляющее воздействие yi. Одновременно можно формировать все управляющие воздействия, допустимые в данный момент времени (не взаимно исключающие). Это позволяет обеспечить макс распоралеливание и макс быстродействие при выполнении команд

|

y1 |

y2 |

… |

. |

yn |

Недостаток – высокие аппаратные затраты и большая разрядная сетка регистра команд.

2)Вертикальное кодирование.

В Рг команд запис двоичн код управляющего воздействия yi, в каждый момент времени может формироваться только одно воздействие (мин разрядная сетка, нет рапаралеливания, команда выполняется за максимальное количество тактов).

3)Вертикально-горизонтальное микропрограммирование.

Все множество управляющих воздействий yi разбивается на К подмножеств по принципу наиболее часто встречающихся одновременно yi. Управляющие воздействия в подмножестве кодируются горизонтально, а номер подмножества вертикально.

4)Горизонтально-верикальное микропрогр

Все множество упр возд yi разбивается на К подмножеств по принципу наиболее редко встречающихся одновременно или взаимно исключающих yi. Управляющие воздействия в подмножестве кодируются вертикально, а номер подмножества горизонтально.

Если команда выполняется за один такт, то она однофазная, если за много тактов – многофазная. Реально в коде команды содержится несколько дополнительных полей, в зависимости от кода которых меняется функциональное значение остальных полей разрядов.

-----------------------------------------------------------------------------------------------------

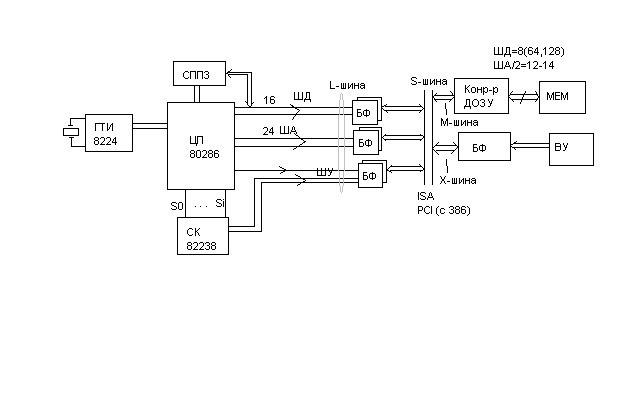

17. Организация эвм типа ibm pc/at

L-шина обладает пониженным напряж питания(напр пит ЦП)

S-шина нормальная магистраль 5В. Первое поколение- ISA шины следующее PCI. Как вариант PCI была шина VESA.

М-шина (шина подкл памяти)

Х-шина обращения к ВУ.

ША/2-потому что динамич память (адр строки, адр столбца)

Базовый магистральный кристалл VL82C100- контроллер ВУ (84 конт, 2 контр ПДП 82237, 2 контр прерываний, таймер)

VL82C101-сист контр(генератор тактовык импульсов 8224, сист контр 88238,СППЗ 80287) с пониженным питанмем.

VL82C102-контроллер ДОЗУ

Протокол обмена по системной шине ISA (такой же как у про-цессора 1810ВМ86) каждый обмен выполн за 4 такта. 1 такт состояния 2 такт-командный.

Любая ЭВМ содержит: ЦП, ГТИ, модули ПЗУ, модули ОЗУ, таймер, контролер прерыв(м/б и ПДП), устр упр вв/выв (ППИ), устр последов вв/выв.

Если все эти устр-ва установить на одном кристалле то получится однокристальная ЭВМ (транспьютер).

-----------------------------------------------------------------------------------------------------