- •1.Процессоры

- •2.Многофункциональное алу

- •3.Управляющие автоматы с жесткой логикой

- •4.Управл автоматы с мпу

- •5.Организация модулей пзу

- •6.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •7.Организация динамических модулей дозу

- •8.Вс классификация по Флинну

- •9.Машины упр потоками данных(df-машины)

- •10. Общие полож.Risc-проц. Берклинская арх.

- •11. Общие полож.Risc-проц. Старнфордсая структура

- •12. Кэш память.

- •13. Виртуальная память.

- •14.Синхр способ продкл ву к см

- •15. Асинхр способ продкл ву к см

- •16. Требования к кодам команди способы кодирования.

- •17. Организация эвм типа ibm pc/at

- •18. Процессор Pentium

- •19. Процессор Pentium II (Pentium Pro)

- •20. Процессор Pentium VI

- •21. Структура вс с общей шиной, каждый с каждым, дублированная шина, кольцо

- •22. Структура вс древовидная, почтового ящика, многопортового озу

- •23. Архитектура Сммр,Сvмр.

- •24. Архитектуры вс типа Сm, BlueChip, Минимакс, Сумма.

- •25. Прогр контр прерываний.

- •26. Контролер пдп.

- •27. Ппи

- •27.М/о ч/з ппи.

- •28. Однокристальн эвм

- •29. Покдл модулей дозу к см(прозр рег).Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

1.Процессоры

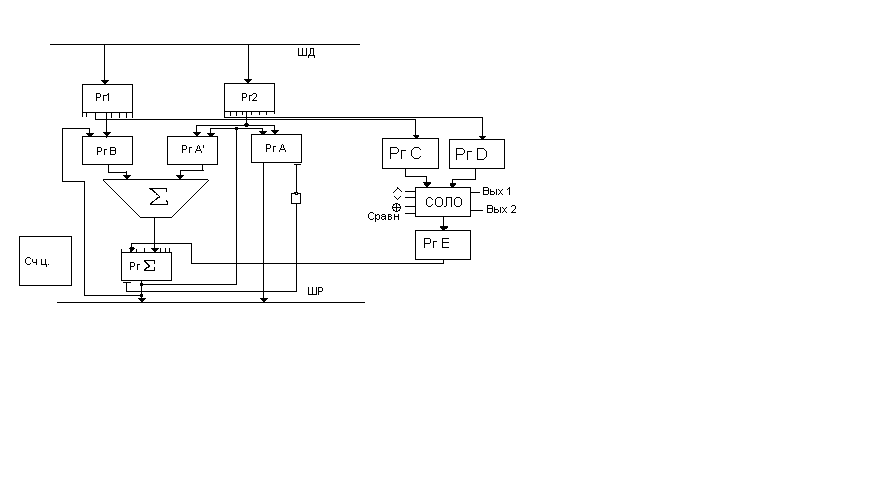

Процессор-это центр устр, обеспечивающее автоматическую обработку цифровой информации в соотв с заданным алгоритмом.

При разработки CPU анализируется область его приминения и выдиляется группа наиболее часто встречающихся команд. Выделяемая группа команд обычно реализуется аппаратно и выполняется с максимальным быстродействием. Те команды, которые не могут быть выполнены аппаратно выполняются на подпрограммном уровне. Процессор должен иметь алгоритмически полную систему команд.

![]()

x1 – состояние ОУ (знаки операндов, переполнение, переноса);

x2 – код команды ассемблера.

ОУ – включает в себя совокупность сумматоров, регистров, счетчиков, дешифраторы, мультиплексоры, триггеры и КЛС. Работа узлов ОУ осуществляется под управлением управляющих сигналов yi (временная последовательность импульсов). На одно управляющие воздействие yi в ОУ выполняется какая-либо микрокоманда (запись в регистр числа, обнуление или сброс регистра, пересылка или перезапись содержимого одного регистра в другой, сдвиг влево или вправо, инкриминирование или декрементирование содержимого счетчика, суммирование на сумматоре двух чисел, обмен инфы по информационной магистрали, выполнение к-л логической операции КЛС). За одно и то же управляющее воздействие yi может быть выполнено несколько таких микрокоманд. Совокупность микрокоманд, предназначенных для выполнения одной команды ассемблера, называется микропрограммой.

АЛУ – центральная часть ОУ. В зависимости от вида представления информации и особенностей арифметики АЛУ делятся:

арифметика чисел с фикс (,)

арифметика чисел с плавающей (,);

в D-кодах (десятичный код);

спец арифметика (операции нормирования, работа с алфавитно-цифровыми полями);

арифметика в спец кодах (кодах Фибоначчи (помехозащищенные отказоустойчивые коды))

-----------------------------------------------------------------------------------------------------

2.Многофункциональное алу

Аппаратн затраты многофукц АЛУ позволяют:

1) Выолн опер + - * / чисел с фикс(,)

2) Операции лог обр-ки ( и,или,слож по модулю два) операндов

3) Использ Рг С и D для обработки порядков позвол выполнять операции арифм с плавающ(,).

Это все достигается только за счет различных последовательностей упр возд-й (yi) разные микропрограммы управления.

-----------------------------------------------------------------------------------------------------

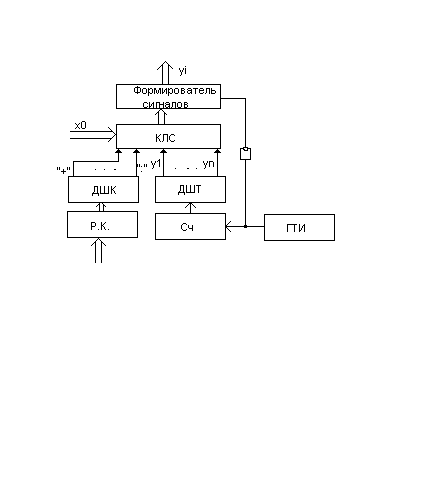

3.Управляющие автоматы с жесткой логикой

КЛС-комб.лог.схема

ГТИ-генер.такт.имп

ДШК-дш.команд

ДШТ-дш.тактов

Р.К.-регистр команд.

Счетчик имеет коэфф пересчета = числу упр воздействий yn, необходимые для выполнения самой длинной команды, напр деление; для более коротких команд, напр + упр возд-я получаются из общего числа yn путем блокировки КЛС yi не участвующих в в выполн данной ком-ды.

В РК загружается код команды, ДШК опред тип выполн ком-ды. ДШТ дешифрует состояние счетчика и формирует одно из управляющих воздействий. Выход с ДШК в совокупности с сигналами состояния АЛУ xi разрешает прохождение на выход через буфер соответствующих сигналов yi (только тех yi которые участвуют в выполнении данной команды, остальные КЛС блокирует). Инвертор разрешает прохождение yi после прохождения "гонок" (все сигналы долгии). Все ком-ды выполн за одинаковое кол-во тактов соотв самой длинной ком-де. Если изм-ся микропрогр упр-е для выполн какой–либо одной ком-ды необходимо пересчитывать или пересинтезировать всю КЛС – недостаток.

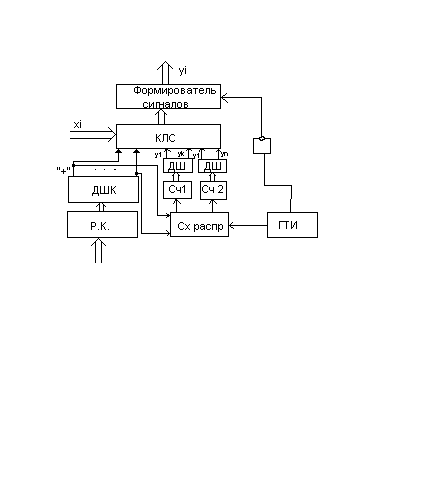

Для повышения быстродействия команды условно разбиваются на группы по длительности выполнения:

короткие – (+,-)

длинные – (*, / арифметика с пл.запятой).

-----------------------------------------------------------------------------------------------------