- •1.Процессоры

- •2.Многофункциональное алу

- •3.Управляющие автоматы с жесткой логикой

- •4.Управл автоматы с мпу

- •5.Организация модулей пзу

- •6.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •7.Организация динамических модулей дозу

- •8.Вс классификация по Флинну

- •9.Машины упр потоками данных(df-машины)

- •10. Общие полож.Risc-проц. Берклинская арх.

- •11. Общие полож.Risc-проц. Старнфордсая структура

- •12. Кэш память.

- •13. Виртуальная память.

- •14.Синхр способ продкл ву к см

- •15. Асинхр способ продкл ву к см

- •16. Требования к кодам команди способы кодирования.

- •17. Организация эвм типа ibm pc/at

- •18. Процессор Pentium

- •19. Процессор Pentium II (Pentium Pro)

- •20. Процессор Pentium VI

- •21. Структура вс с общей шиной, каждый с каждым, дублированная шина, кольцо

- •22. Структура вс древовидная, почтового ящика, многопортового озу

- •23. Архитектура Сммр,Сvмр.

- •24. Архитектуры вс типа Сm, BlueChip, Минимакс, Сумма.

- •25. Прогр контр прерываний.

- •26. Контролер пдп.

- •27. Ппи

- •27.М/о ч/з ппи.

- •28. Однокристальн эвм

- •29. Покдл модулей дозу к см(прозр рег).Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

- •30. Арбитраж по последовательному опросу.

- •30. Арбитраж по || опросу.

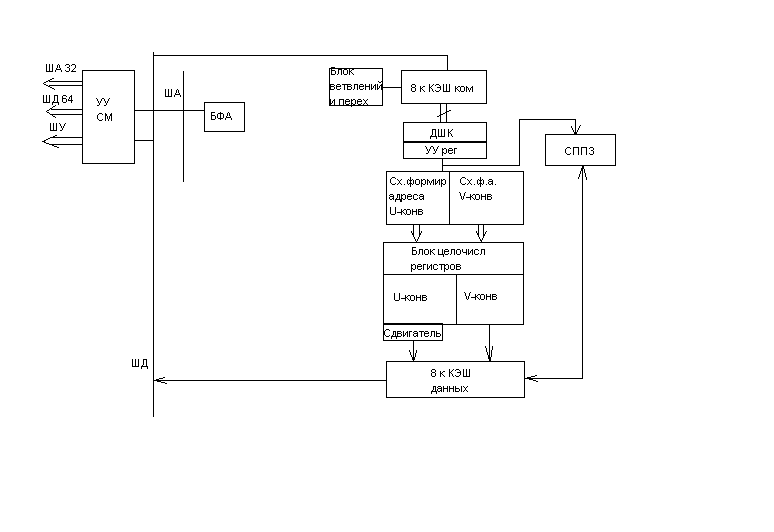

18. Процессор Pentium

С начала 486 проц а затем и проц ряда Pentuimстали использовать эл-тыRISCарх-ры (глубокий конвейер, все команды выполняются за опр промеж времени). С переходом наPentiumдля обеспеченияminвыполнения команд арифметики с палвающ (,) потребовалось сильно переделать СПЗ(сопроцессор) первые партииPentuimбыли с ошибкой в СПЗ.

ША-32 ШД-64(внешн) ШД-32(внутр)

БФА –блок формирования адреса

СППЗ – сопроцессор с плавающей запятой

Процессор имеет суперскалярную архитектуру (закладывается параллелизм) и при тактовой частоте 66MHzпроцессор обепечивал производ-ть до 100млн опер/с. Внутр структура проц Гарвардская (раздельная память команд и память данных). Внешняя структура фон-Неймановская. Обращение в внешней памяти идет блоками по 4 64-разр слова для заполнения 256 разр КЭШ. Процессор имеет 2 || работающих 5-ти ступенчатых конвейераUиV. КонвUполноразмерный и на нем может выполн любая ариф и лог команда.Uимеет 64-разр сдвигатель. КонвVупрощенный, предназ начен для выполнения простых команд типа сдвига,лог опер (легких). Команда из КЭШ дешефрируется (ДШК) и УУ рег-ми и микрокомандами выбирает аппаратные ресурсы необход-е для выполн данной команды, при этом команды анализирются на возможность их одновременного выполнения вUиVконв. Схема формир адр следит за тем чтобы последовательность выполнения команд не нарушалась.

В проц-ре впервые исполз схема предсказания переходов (блок ветвл переходов).В БВ хранится до 256 адресов последних переходов. Вероятность предсказания ≈10%. Принцип: если переход состоялся то в след цикле наиболее вероятно , что этот переход повторится. Это позволяет не ломать “логику” конвейера.

БФА обеспечивает формир адреса при работе с внешними модулями памяти и ВУ. Адр простр памяти и ВУ раздельное.

Проц имеет возмодность работать с КЭШ 2-го уровня который нах-ся на матер плате (в процессоре встр контроллер КЭШ памяти и встроенный контроллер Вирт памяти.)

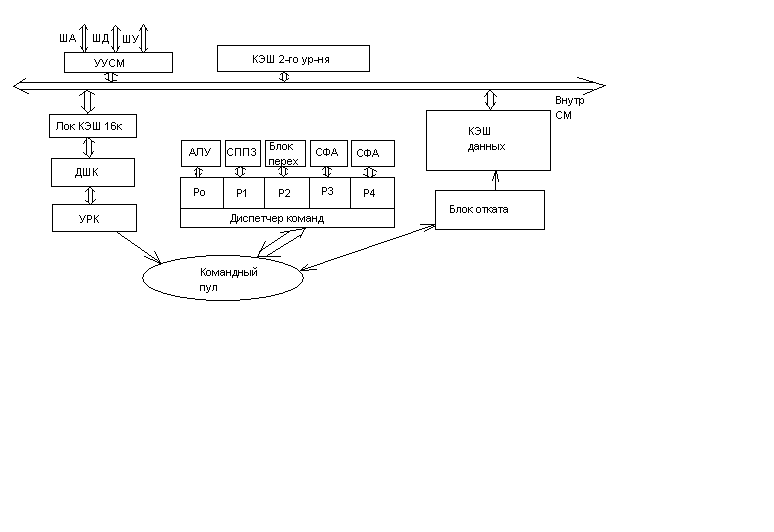

19. Процессор Pentium II (Pentium Pro)

УРК- устр распред команд.

Процессор имеет суперскалярную архитектуру и на кристалле располагается двухуровневая КЭШ. 16кб КЭШ команд и 16кб КЭШ данных. КЭШ 2-го ур-ня (общая)(128k-2mb). Одновременно работают до5-ти аппаратных ресурса (5 команд может выполн одновременно). Проц имеет 11-ти ступ конвейер т.е. все команды выполняются за 11 тактов. Команда из КЭШ памяти поступает в ДШК, УРК формирует блоки из кодов команд и операндов ктр загружаются в пул команд, ДШ команд из цикла выбирает те команды которые для которых определены операнды и есть свободные аппаратные ресурсы, команды выполн аппаратными ресурсами и возвращаются обратно в пул команд. Блок отката выбирает из пула команд выполненные ком-ды и восстанавливает последовательность выполнения команд в соотв с программой. Результат отправляется в КЭШ данных 1-го уровня.

Процессор относится к разряду машин управляемых потоком данных. Проц имеет несколько напряж питания : вычислительное ядро запитывается напряж-ем 2,3В, микросхема обвязки (внешний уровень) повышенным, мощность потребл достигает 40Вт. Прой имеет встроенный датчик температуры и встроенный АЦП, а также требует внешней системы охлаждения. Потребляемый ток 15-20 А.