- •1.Процессоры

- •2.Многофункциональное алу

- •3.Управляющие автоматы с жесткой логикой

- •4.Управл автоматы с мпу

- •5.Организация модулей пзу

- •6.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •7.Организация динамических модулей дозу

- •8.Вс классификация по Флинну

- •9.Машины упр потоками данных(df-машины)

- •10. Общие полож.Risc-проц. Берклинская арх.

- •11. Общие полож.Risc-проц. Старнфордсая структура

- •12. Кэш память.

- •13. Виртуальная память.

- •14.Синхр способ продкл ву к см

- •15. Асинхр способ продкл ву к см

- •16. Требования к кодам команди способы кодирования.

- •17. Организация эвм типа ibm pc/at

- •18. Процессор Pentium

- •19. Процессор Pentium II (Pentium Pro)

- •20. Процессор Pentium VI

- •21. Структура вс с общей шиной, каждый с каждым, дублированная шина, кольцо

- •22. Структура вс древовидная, почтового ящика, многопортового озу

- •23. Архитектура Сммр,Сvмр.

- •24. Архитектуры вс типа Сm, BlueChip, Минимакс, Сумма.

- •25. Прогр контр прерываний.

- •26. Контролер пдп.

- •27. Ппи

- •27.М/о ч/з ппи.

- •28. Однокристальн эвм

- •29. Покдл модулей дозу к см(прозр рег).Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

- •30. Арбитраж по последовательному опросу.

- •30. Арбитраж по || опросу.

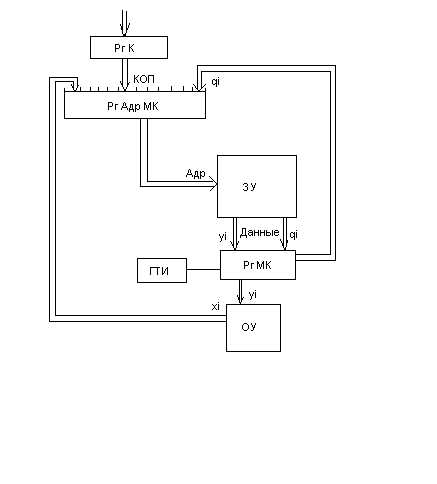

4.Управл автоматы с мпу

КОП-код операции; qi - состояние управляющего автомата (указывает на адр след МК).

В Рг.К записыв-ся код команды, который в Рг.Адр.МК задает начальный адрес памяти, где располагается первое управляющее воздействие yiдля выполнения данной команды. Одновременно по этому адресу записывается биты состоянияqi, которые указывают на адрес следующей микрокоманды, для выполнения данной команды. Адрес МК зависит от признаковxiоперационного устройства.

Требуются большие затраты памяти, т.к. возникает многократное повторение управл воздействий yiв зависимости от разл состоянийxi.

В ЗУ прописыв-ся система команд МК. Если в качестве ЗУ используют ПЗУ, то процессор имеет жестко заданную сист команд. Вместо ПЗУ можно использовать ОЗУ и тогда перед началом работы в проц загружается новая система команд и можно делать совместные проги работающие на разных процах (напр сделать совместными проги под IntelиMotorola(Mac)).

Достоинства:1)Каждая ком имеет свою область памяти микропрограмм (измен одной ком не приводит к необх переделки остальн ком) 2)Для выполн каждой ком-ды выделяется столько времени сколько необх-мо (длительности выполн всех команд различны и минимальны)

5.Организация модулей пзу

Пусть требуется подключить модуль 24kbх8 начиная с 0 адр, состоящий из микросх 8кх8 (нужно 3 м.сх.)

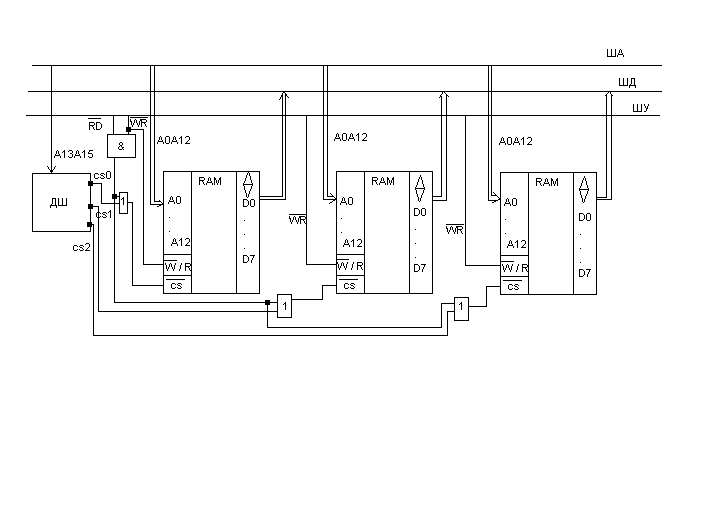

6.Организация модулей статического озу.

Рисуем карту адресного пространства и определяем место где располагается модуль памяти. Для каждой микросх строится ДШ на опр комб ША (на ДШ поступают старш разр с ША,а младш поступ на микросх ОЗУ)

8-ми разрядные модули памяти

микросхема памяти вкл в работу CS0 тогда когда адрес попадает в адресное пространство данной миросхемы и есть сигнал чтения или записи.

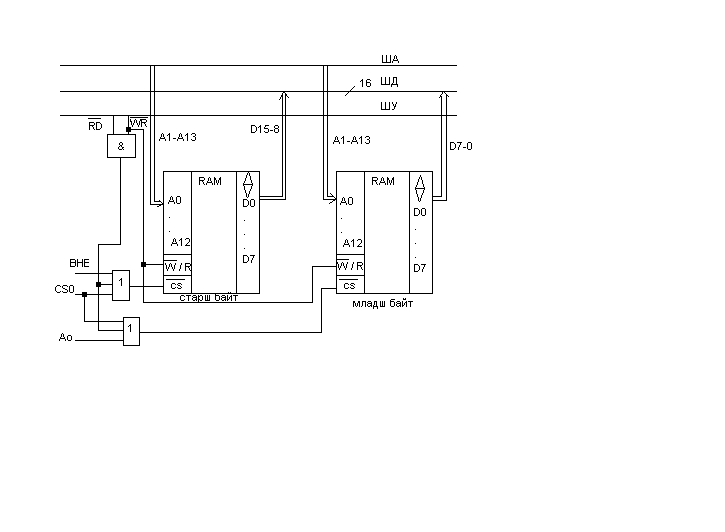

16-Ти разрядные модули памяти

ВНЕ- выборка старшего байта.

|

ВНЕ |

А0 |

|

0 |

0 |

|

0 |

1 |

|

1 |

0 |

|

1 |

1 |

16-разр слово

старший байт

младший байт

нет обращения

При обращении к 16 разр ШД в ШУ присутствует сигнал ВНЕ, ктр в комбинации с Ао обеспечивает обр-е к 16 разр слову отдельно млад или отдельно старш байту. Счетчик команд после обр по адресу автом увел на два (слова располагаются по четным адр т.е. Ао=0).

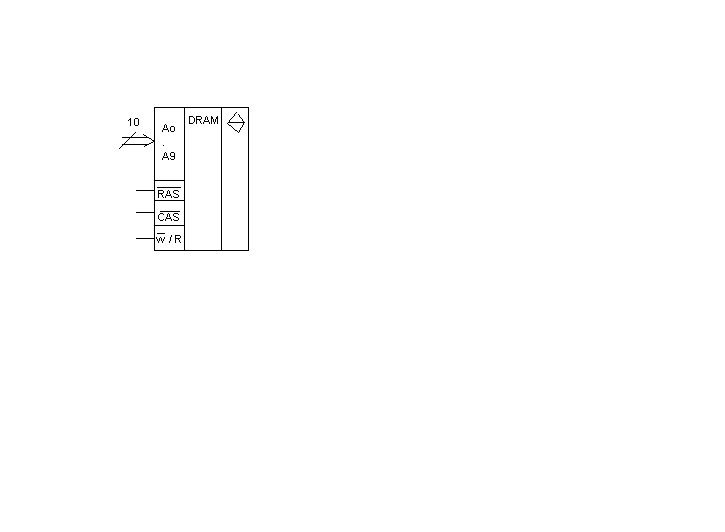

7.Организация динамических модулей дозу

В ДОЗУ одна ячейка памяти строится на одном транзисторе (в статических ОЗУ на одну ячейку памяти прих 2 тр) и использует "паразитную" емкость затвор-сток.

в ДОЗУ хранение инф обеспечив за счет наличия заряда на паразитной емкости затвора-истока. Инф в динам ячейке ч/з какое-то время пропадает за счет рассеивания заряда из-за сопротивл этой емкости. Чтобы этого не происходило инф в ДОЗУ периодически восстанавл (регенерируется). Динамическая память требует в 2 раза меньше затрат.

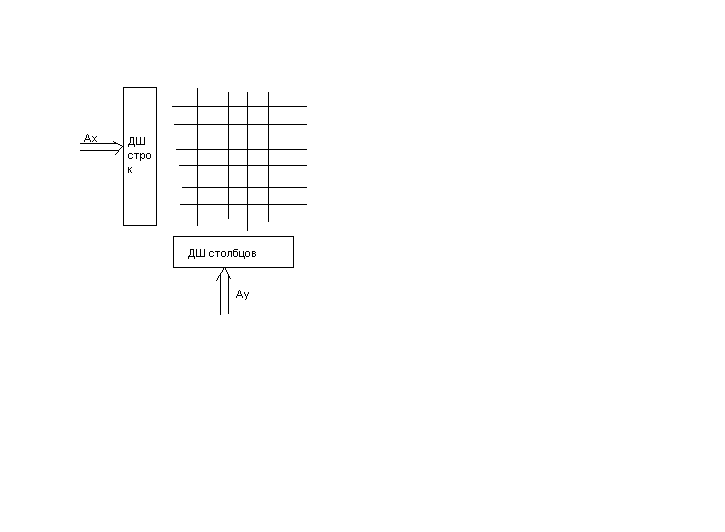

Микросхема динамической памяти представляет адрес в виде адреса строки (RAS) и столбца (CAS).

Обращение происходит, когда сформирован полноразмерный адрес. Для осуществления циклов регенерации достаточно сформировать только адрес строки, т.е. при этом напряжение питания подается на все строку и осуществляется регенерация всех ячеек памяти, расположенных на данной строке.

Частота регенерации задается техническими характеристиками микросхемы – от 8 до 16 мс.

Динамическая память требует применение контролеров ДОЗУ, которые разбивают адрес на адрес строки и столбца, сопровождая их сигналами RASиCAS, а так же осуществляется их регенерация.

На ША контроллером ДО ЗУ выставл адр стр Ах и защелкивается отриц фронтом сигн-ла RASв Рг ДОЗУ, затем контроллер ДОЗУ выставл на ША адр столбща Ау ктр защелк по отриц фронту сигн СAS,RAS=0 иCAS=0; вкл микр в работу и она анализир сигналыW/Rи в завис от него считывает инф с ШД в себя или выдает на ШД. ПоявлCASиRAS=1 переводит ее выход по ШД в 3 сост.

Для того чтобы вызвать регенерацию (в завис от типа микросх) сущ неск способов:

1)OnlyRAS– прозрачная регенерация.

2)Обычно использ в встр счетчиком адреса регенер и наз-ся CASbeforeRAS