- •1.Процессоры

- •2.Многофункциональное алу

- •3.Управляющие автоматы с жесткой логикой

- •4.Управл автоматы с мпу

- •5.Организация модулей пзу

- •6.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

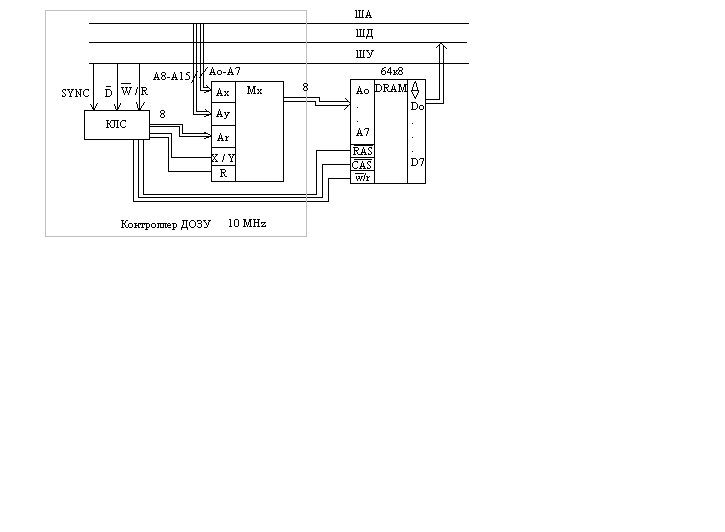

- •7.Организация динамических модулей дозу

- •8.Вс классификация по Флинну

- •9.Машины упр потоками данных(df-машины)

- •10. Общие полож.Risc-проц. Берклинская арх.

- •11. Общие полож.Risc-проц. Старнфордсая структура

- •12. Кэш память.

- •13. Виртуальная память.

- •14.Синхр способ продкл ву к см

- •15. Асинхр способ продкл ву к см

- •16. Требования к кодам команди способы кодирования.

- •17. Организация эвм типа ibm pc/at

- •18. Процессор Pentium

- •19. Процессор Pentium II (Pentium Pro)

- •20. Процессор Pentium VI

- •21. Структура вс с общей шиной, каждый с каждым, дублированная шина, кольцо

- •22. Структура вс древовидная, почтового ящика, многопортового озу

- •23. Архитектура Сммр,Сvмр.

- •24. Архитектуры вс типа Сm, BlueChip, Минимакс, Сумма.

- •25. Прогр контр прерываний.

- •26. Контролер пдп.

- •27. Ппи

- •27.М/о ч/з ппи.

- •28. Однокристальн эвм

- •29. Покдл модулей дозу к см(прозр рег).Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

- •30. Арбитраж по последовательному опросу.

- •30. Арбитраж по || опросу.

29. Покдл модулей дозу к см(прозр рег).Способы регенерации

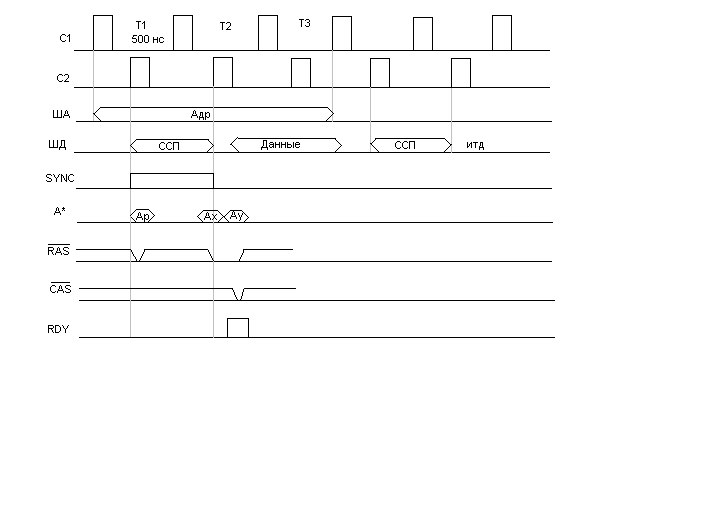

Прозр регенер- это такая регенерация о сущ которой на процессор не догадывается. (задержек нет).

2 MHzТ=500нс

Т.к. быстродействие памяти выше в данном случае быстр проц-ра (Тпрой=500нс)(Время доступа к ДОЗУ 150-200нс),то за один период тактовой частоты проц быстрод микросх ДОЗУ позволяет провести цикл регенер.Этот цикл удобно делать тогда когда на ШД нах-ся ССП (еще нет обращения к ДОЗУ). На быстрод процессора это не сказывается

Прозр регенер возможна когда ДОЗУ быстрее проц-ра.

Регенер ДОЗУ с блокировкой сигнала готовности RDY- прим тогда когда бвстрод ДОЗУ < быстр проц. В этом случае цикл реген осущ не каждый цикл обр к памяти (как в прозр регенер), а один раз за несколько циклов бор (зависит от проц и времени хранения инф в ДОЗУ) обычно 1 цикл реген приходится на 64-128 циклов обр-я. В цикле реген происх блокирование сигналаRDYна 1-2 такта чтобы успеть провести регенер.Это снижает производительность проц-ра на доли процента что приемлимо.

3 способ регенер ДОЗУ в режиме ПД. В эстом случае один раз за 8-16мс проц перев в режим ПДП и контроллер ДОЗУ осущ группу циклов регенер для всего модуля ДОЗУ.

30. Понятие интерфейса. Виды арбитража

Интерфейс – это совок-ть аппаратных, программных и конструктивных ср-в, предназначенных для обмена инф-цией м/д различными цифровыми устр-вами. Под физ-кой линией связи понимается электропроводник, оптоволокно. Совок-ть линей связей, объединенных по функц-ному назначению наз-ся шиной.

В интерфейсе выделяют: 1)инф-ную магистраль (ША, ШД, Шсостояния) Различная информация на шинах мултиплексированна во времени, след-но исп-ся доп-ные идентифиц. сигналы. 2) ШУ инф-ной магистралью(сигналы идентификации, WR,RD,HLD,HLDAи др, Ш прерывания, Ш приоритетов (арбитража), спец-ные сигналы (биты четности))

Функции арбитража

1)Временной арбитраж

Обычно интерфейс строится по принципу «ведомый-ведущий». Ведущая машина берет на себя фукции упр СМ.

ИБ каждого устр-ва имеет одинаковый счетчик, на вход к-рого подается один и тот же сигнал тактовой частоты. По RESET(системному сбросу) все счетчики сбрасываются в 0, что обозначает, что в каждый мом-т времени находится один код. Пусть счетчик 10 разрядный. 1-й машине предоставляется СМ, если код в счетчике от 0-100 и т.д. время предоставления СМ определяется важностью и объемом передаваемой информации. ДШ с выхода каждого счетчика подключает ИБ к СМ лишь в случае нахождения кода в данных пределах.

+)Простота и небольш апп затраты.

-)Нерациональн использ СМ.

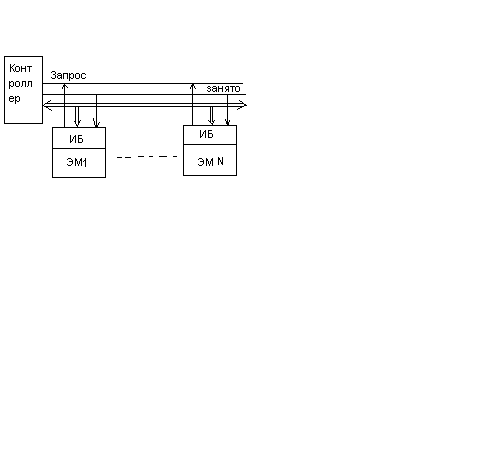

2) Способ адресного сканирования

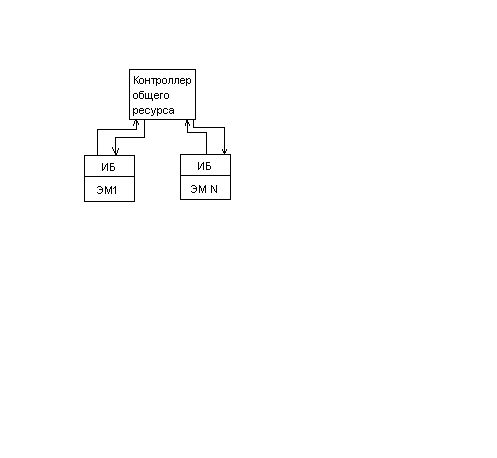

Машина Nвыставляет запросы контроллера СМ. Получив запрос, контроллер начинает опрашивать по фиксированным адресам в порядке убывания приоритетов интерфейсные блоки машин, подключенных к СМ. При нахождении машины, выставившей запрос, контроллер формирует сигналbusyи предоставляет СМ этой машине.

+) рациональная загруженность СМ

-) интеллект. Контроллер . К-р можно перепрограммировать.

СМ освобождается при снятии запроса.

3) Цепочный арбитраж

Машина, которой необходима СМ выставляет сигнал запроса, контроллер формирует строб, который последовательно проходит через интерфейсные блоки всех машин, начиная с машины с высшим приоритетом. Если машина запрос не выставляла, интерфейсный блок пропускает его дальше и т.д. Если машина запрос выставила, интерфейсный блок блокирует дальнейшее прохождение стоба и выставляет сигнал busy.

+): аппаратные затраты минимальны, контроллер простой.

-_: устройство с низким приоритетом редко получают доступ к СМ, поэтому реально не делают больше 20 устройств

4)Способ радиальной селекции (арбитража)

Контроллер интеллектуальный, приоритеты гибкие, время доступа определено.