- •1.Процессоры

- •2.Многофункциональное алу

- •3.Управляющие автоматы с жесткой логикой

- •4.Управл автоматы с мпу

- •5.Организация модулей пзу

- •6.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •7.Организация динамических модулей дозу

- •8.Вс классификация по Флинну

- •9.Машины упр потоками данных(df-машины)

- •10. Общие полож.Risc-проц. Берклинская арх.

- •11. Общие полож.Risc-проц. Старнфордсая структура

- •12. Кэш память.

- •13. Виртуальная память.

- •14.Синхр способ продкл ву к см

- •15. Асинхр способ продкл ву к см

- •16. Требования к кодам команди способы кодирования.

- •17. Организация эвм типа ibm pc/at

- •18. Процессор Pentium

- •19. Процессор Pentium II (Pentium Pro)

- •20. Процессор Pentium VI

- •21. Структура вс с общей шиной, каждый с каждым, дублированная шина, кольцо

- •22. Структура вс древовидная, почтового ящика, многопортового озу

- •23. Архитектура Сммр,Сvмр.

- •24. Архитектуры вс типа Сm, BlueChip, Минимакс, Сумма.

- •25. Прогр контр прерываний.

- •26. Контролер пдп.

- •27. Ппи

- •27.М/о ч/з ппи.

- •28. Однокристальн эвм

- •29. Покдл модулей дозу к см(прозр рег).Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

- •30. Арбитраж по последовательному опросу.

- •30. Арбитраж по || опросу.

30. Арбитраж по последовательному опросу.

Счетчик имеет коэф-т пересчета Nравный числу машин, нуждающихся в общем ресурсе. ДШ подключается к параллельному выходу счетчика, который в конкретный момент имеет только 1 возбужденный выход. Счетчик считает от 0 доN, переполняется, сбрасывается в 0, и 1-ца (маркер) на выходе ДШ бегает по кругу. Пусть ЭМ1 выставила запрос, когда маркер попадает на вход элементаi1на выходе 1-ца, которая проходит ч/з «или» и блокирует поступление тактовых импульсов на вход счетчика. Одновременно выход элемента «и» есть разрешение для ЭМ1. Получив Р1 ЭМ1 работает с СМ. В каждый мом-т времени маркер может находится только на одном элементе «и» и разрешение м.б. выдано только одной ЭМ. По окончании с СМ ЭМ убирает запрос и на выходе «и» - 0. Вход счетчика разблокируется и маркер побежал дальше.

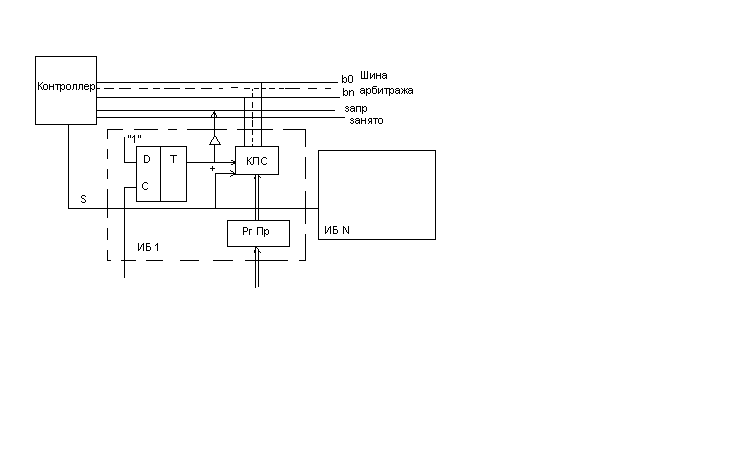

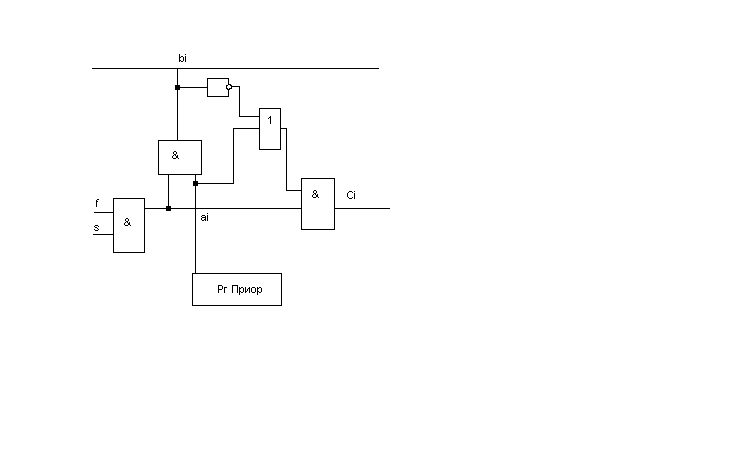

30. Арбитраж по || опросу.

Ш арбитража построена по принципу монтажного «или» любая 1 на выходе ставит bi в 1.

В регистр приоритета записывается код приоритета (maxприоритет все единички).

|

ai |

bi |

ci |

|

0 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

нет |

щий разряд.

3 строка – устр-во выбыло из кон-курса.

4 строка –невозм-я комбинация

КЛС работает в соответствии с таблицей. Если после анализа старшего разряда СN=1, это означает, что устр-во имеет высший приоритет из всех уч-щих в конкурсе и подключ-х к СМ. Если в процессе сравнения приоритетов Сi=0, устройство выбывает из конкурса. Анализ всех разрядовAiво всех интерфейсных блоках идет параллельно. Высокое быстродействие, высокие затраты, в кач-ве арбитров исп-ся обычные однокристалки.