- •1.Процессоры

- •2.Многофункциональное алу

- •3.Управляющие автоматы с жесткой логикой

- •4.Управл автоматы с мпу

- •5.Организация модулей пзу

- •6.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •7.Организация динамических модулей дозу

- •8.Вс классификация по Флинну

- •9.Машины упр потоками данных(df-машины)

- •10. Общие полож.Risc-проц. Берклинская арх.

- •11. Общие полож.Risc-проц. Старнфордсая структура

- •12. Кэш память.

- •13. Виртуальная память.

- •14.Синхр способ продкл ву к см

- •15. Асинхр способ продкл ву к см

- •16. Требования к кодам команди способы кодирования.

- •17. Организация эвм типа ibm pc/at

- •18. Процессор Pentium

- •19. Процессор Pentium II (Pentium Pro)

- •20. Процессор Pentium VI

- •21. Структура вс с общей шиной, каждый с каждым, дублированная шина, кольцо

- •22. Структура вс древовидная, почтового ящика, многопортового озу

- •23. Архитектура Сммр,Сvмр.

- •24. Архитектуры вс типа Сm, BlueChip, Минимакс, Сумма.

- •25. Прогр контр прерываний.

- •26. Контролер пдп.

- •27. Ппи

- •27.М/о ч/з ппи.

- •28. Однокристальн эвм

- •29. Покдл модулей дозу к см(прозр рег).Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

- •30. Арбитраж по последовательному опросу.

- •30. Арбитраж по || опросу.

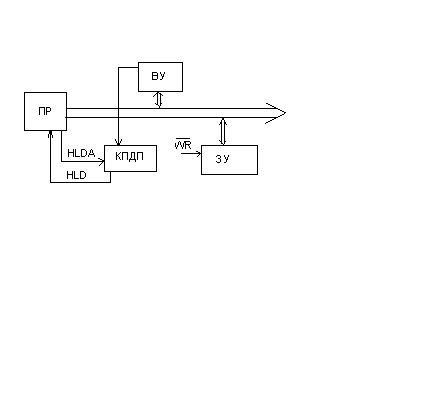

26. Контролер пдп.

Intel82237

Центральная задача:

1)КПДП берет на себя функции управления СМ и формирование ША при отключении ЦП от СМ.

2)Осуществляет арбитраж между разными устройствами, запрашивающими режим ПДП.

Классическое периферийное устройство ВУ

DMR-запрос на ПДП от ВУ,DACK-разрешение на ПДП от ВУ,HLD-запрос от пр-ра,HLDA-разрешение от пр-ра.

Контролер всегда имеет в паре: RDJ0,WR,RD,WRJ0.

Контролер имеет 4 идент. канала К0-К3. Каждый канал содержит 16 разр. регистр адреса и 14 разр. счетчик циклов. По включении питания ЦП в программе нач. пуска (BIOS) прогр-т все периферийные микросхемы, в том числе контролер ПДП. В контролере ПДП проц для каждого канала (ВУ) задает нач. адрес (перв.ячейку памяти запис-ся в РгА канала) и задается число циклов(зап-ся число циклов в канал).Адрес формируется путем инкрементирования РгА (соот-но после каждого цикла число циклов декрементируется). Режим ПДП заканчивается, когда счетчик циклов=0. В этот момент времени формируется сигналTCт.е. последний цикл. Максимальный размер этого блока=16 кбайт, т.к. счетчик циклов 14р, максимальный объем памяти перегоняемый в ПДП=214или 16 кбайт (ПДП не может слишком долго, так как СМ занята и невозможна регенерация динам памяти).

Как контролер ПДП подключается к СМ: STBA-строб адреса.

При программировании контролера использ-ся разряды ША А0÷А3 и CS=0. Помимо прогр-я каждого канала в отдельности запис-ся управл-ее слово(только после того как все каналы запрогр-ся).

Управл-ее слово задает приоритеты между каналами, устанавливается флаги конца цикла ПДП в слове состояния (СС).

ЦП период-ки считывает СС контр-ра ПДП , в котором определяет происходил ли обмен инфой по конкретным каналам (т.е свежая ли проц инф и забран ли от проца готовый предыдущий рез-т). Если цикл ПДП прошел, обмен инфой состоялся, пр-р перепрограммирует контр-р по данному каналу(это делает ОС).

STBAстробирует адрес на ША.

М128-каждый 128 цикл формируется строб, длительностью один цикл.чтобы показать что система не зависла, а идут циклы ПДП.

27. Ппи

Мксх поддержки по мат. плате – группа чипсет. ППИ предн. для подкл. периферийных устройств к СМ.

Все 4 канала независимы друг от друга и могут использ. как на ввод так и на вывод инфы. Порт- совокупность регистра и ШФ. РУС –регистр управляющего слова.

|

|

КАШД |

КВШД |

КСШД |

КА |

КВ |

КС |

РУС |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

A0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

A1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

WRJ0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

ППИ может раб-ть в одном из 3 режимов. Режим задается в регистре управляющего слова (РУС).

РУС

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

D0-к С1 0-ввод 1- вывод;

D1-к В

D2- задает реж “0” канало С1 и В

D3-к С2 и А

D4-к А (ввод/вывод)

D5D6-номер режима 00-“0” реж 01-первый реж 1х-второй реж

D7-1 признак РУС

Режим “0” предн. для синхронных обменов инфой, каждый из каналов независимо друг от друга может передавать или принимать сигналы в зависимости от РУС.

Режим “1” предн. для асинхронного обмена. В этом режиме данные передаются по каналам А и В, канал С исп-ся для формирования битов квитирования.

Если в режиме 0 или 1 требуется поменять направление передачи инфы ППИ необходимо перепрогр-ть(тратится время). Для скоростного обмена инф-й исп-ся режим 2. В режиме 2 данные могут передаваться только по каналу А. Напр. передачи опред-ся сигналамиRDJO,WRJO.

Порт С используется для формирования битов квитирования. В любом из режимов возм-на побитная установка канала С. В этом случае обращение происходит по адресу упр слова А0А1=1 ат только в РУС старший бит=0 (D7=0).

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

D0-то что нужно записатьD3D2D1-двоичный номер разр в кан С.