- •Обобщенная структура эвм. Принцип программного управления. Параметры эвм.

- •Классификация и принципы структурной организации алу.

- •Структурная организация бо алу. Состав узлов и их связи.

- •Универсальное алу на короткие операции.

- •Проектирование алб универсального алу.

- •5. Сдвигатели.

- •6. Выполнение длинных операций в универсальном алу на короткие операции.

- •7. 7. Ау для выполнения длинных операций с фиксированной запятой. Умножение кодов

- •8. Ау для выполнения длинных операций с фиксированной запятой. Умножение чисел.

- •9. Ау для выполнения длинных операций с фиксированной запятой. Деление кодов.

- •12. Двоично-десятичный сумматор. Ау, работающие в д-кодах, на его основе.

- •13. Динамические и статические озу эвм.

- •14. Расслоение памяти.

- •16. Ассоциативное зу.

- •Универсальный запоминающий элемент ассоциативного зу.

- •20. Микропрограммые уу. Проектирование фус.

- •21. Микропрограммые уу. Проектирование фамк с принудительной адресацией.

- •22. Микропрограммые уу. Проектирование фамк с естественной адресацией.

- •23. Центральный процессорный элемент секционированного мпк.

- •24. Бис схемы управления адресом микрокоманды секционированного мпк.

- •25. Построение блока обработки данных процессора на элементах секционированного мпк.

- •26. Построение блока микропрограммного управления процессора на элементах секционированного мпк.

- •27. Организация процессора. Форматы команд. Способы адресации.

- •Режимы прямой адресации

- •Структура процессора универсальной эвм. Алгоритм выполнения двухадресной арифметической команды.

- •Двухадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения одноадресной арифметической команды.

- •Одноадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения посылочных команд работы со стеком.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд ветвления.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд работы с подпрограммами.

- •Команды работы с подпрограммами

- •33. Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •34. Интерфейсы.

22. Микропрограммые уу. Проектирование фамк с естественной адресацией.

П ри

естественной

адресации

микрокоманды (МК) делят на операционные

и команды переходов (рис. 14.1). Тип МК

задаётся одним битом: "0" - операционная

МК; "1" - МК переходов.

ри

естественной

адресации

микрокоманды (МК) делят на операционные

и команды переходов (рис. 14.1). Тип МК

задаётся одним битом: "0" - операционная

МК; "1" - МК переходов.

0 |

ОП |

1 |

Х |

АП |

При операционной МК остальная часть МК - закодированная комбинация Y. По синхроимпульсу (рис.14.2) в регистр МК (РМК) загружается МК.

При "0" открывается схема формирования управляющих сигналов (ФУС) и блокируется МХХ. СМК - счётчик МК увеличивается на 1. При "1" схема ФУС блокируется, а МХХ разблокируется. Начинается анализ условия. В этом режиме ЗН (занесение) = (либо то, либо другое). При ЗН= 1 мультиплексор переключится на занесение адреса. Если Х=1, то вырабатывается сигнал +1, т.е. мы либо идём на адрес +1, либо на ?, а в ? мы берём из поля А МК.

Достоинство - сокращение аппаратных затрат за счёт уменьшения разрядности МК. Недостаток - уменьшение быстродействия.

23. Центральный процессорный элемент секционированного мпк.

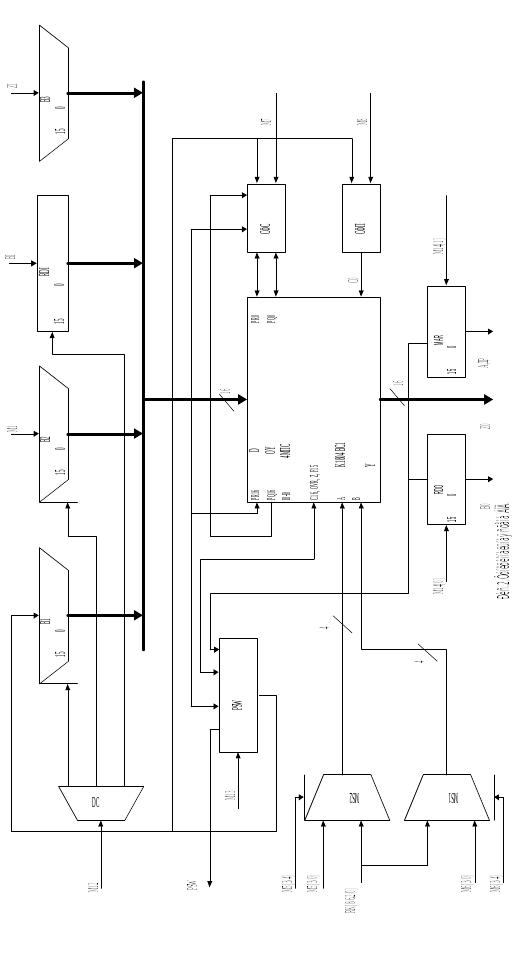

Для реализации процессора с заданной системой команд предлагается использовать в качестве базовой микроЭВМ с разрядномодульной организацией на БИС серии К1804, построенную по типовой схеме. В состав процессора базовой микроЭВМ входят следующие блоки (рис.1): блок микропрограммного управления (БМУ), блок обработки данных (БОД) и интерфейсный блок (ИБ).

Рис.1.Структура базовой микроЭВМ.

БМУ служит для генерации кодов микрокоманд, содержащих поля М1...М15 и управляющих работой БОД и ИБ. БОД осуществляет обработку информации под управлением полей Ml, M5...M14, вырабатываемых в БМУ кодов микрокоманд. По результатам выполнения операций в БОД формируется слово состояния процессора PSW, поступавшее, а БМУ. Информация в БМУ и БОД поступает из ИБ по шине данных В1, ас выхода ЗОД в ИБ поступают данные по шине В0 и адрес по шине DR. Поле М15, код которого поступает из БМУ в ИБ, служит для управления вводом-выводом при этом осуществляется анализ сигналовFLG, вырабатываемых в ИБ.

24. Бис схемы управления адресом микрокоманды секционированного мпк.

25. Построение блока обработки данных процессора на элементах секционированного мпк.

Функциональная схема БОД приведена на рис.2.

В состав БОД входят обрабатывающий узел (ОУ).вентили В1 и В2, входной регистр данных RDI, схема формирования переноса (СФП)- С0 в младший разряд, регистр состояния PSW, выходной регистр, данных RDO, регистр адреса МАR, мультиплексоры, адреса МSА и MSB, дешифратор DC.

Обрабатывающий узел выполнен на микросхемах K1804BCI и может выполнять все арифметические и логические операции, предусмотренные в данной микросхеме. Выполняемая операция задается девятиразрядным кодом 18-10, который образуется кодами М9, М10, М11. Адреса А и В регистров во внутреннем регистровом ЗУ операционного блока ОУ задаются соответственно кодами М5 и М6, при этом на входы А и В могут поступать как коды М5 и М6, так и разряды 8…6 или 2...0 регистра команд.

На вход D операционного узла может подаваться информация с вентилей В1.В2 и регистра RDI, подключение которых к шине D управляется кодом М12. С выхода Y информация может заноситься в RDO или в MAR в соответствии с заданным кодом М14относится команда, хранящаяся на РК, MS выбирает нужный сигнал условия из всех поступающих на его вход сигналов и под управлением кодов М2, МЗ формирует проверяемый сигнал TST, поступаюший в СУСА. CУАM совместно с СУСА определяют следующий адрес микрокоманды в соответствии с кодом М4, проверяемым условием TST, а также кодом, приходящим на вход D СУАМ.

На вход D СУАМ могут поступать коды M1, младшие или старшие разряды PK. Подключением того или иного кода на шину D управляют сигналы ME и РЕ. Если ME = 1. РЕ =0, то к шине адреса ветвления подключается поле Ml, если МЕ = 0,РЕ = 1 , то подключаются старшие разряды РК; если МЕ = 1,РЕ= 1, то подключаются младшие разряды РК. Сигналы CTL, СТЕ управляют работой счетчика, а также при CTE=CTL=0 задаются нулевой адрес на выходе Y схемы СУАМ (переход к микрокоманде с нулевым адресом).