- •Обобщенная структура эвм. Принцип программного управления. Параметры эвм.

- •Классификация и принципы структурной организации алу.

- •Структурная организация бо алу. Состав узлов и их связи.

- •Универсальное алу на короткие операции.

- •Проектирование алб универсального алу.

- •5. Сдвигатели.

- •6. Выполнение длинных операций в универсальном алу на короткие операции.

- •7. 7. Ау для выполнения длинных операций с фиксированной запятой. Умножение кодов

- •8. Ау для выполнения длинных операций с фиксированной запятой. Умножение чисел.

- •9. Ау для выполнения длинных операций с фиксированной запятой. Деление кодов.

- •12. Двоично-десятичный сумматор. Ау, работающие в д-кодах, на его основе.

- •13. Динамические и статические озу эвм.

- •14. Расслоение памяти.

- •16. Ассоциативное зу.

- •Универсальный запоминающий элемент ассоциативного зу.

- •20. Микропрограммые уу. Проектирование фус.

- •21. Микропрограммые уу. Проектирование фамк с принудительной адресацией.

- •22. Микропрограммые уу. Проектирование фамк с естественной адресацией.

- •23. Центральный процессорный элемент секционированного мпк.

- •24. Бис схемы управления адресом микрокоманды секционированного мпк.

- •25. Построение блока обработки данных процессора на элементах секционированного мпк.

- •26. Построение блока микропрограммного управления процессора на элементах секционированного мпк.

- •27. Организация процессора. Форматы команд. Способы адресации.

- •Режимы прямой адресации

- •Структура процессора универсальной эвм. Алгоритм выполнения двухадресной арифметической команды.

- •Двухадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения одноадресной арифметической команды.

- •Одноадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения посылочных команд работы со стеком.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд ветвления.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд работы с подпрограммами.

- •Команды работы с подпрограммами

- •33. Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •34. Интерфейсы.

Режимы прямой адресации

1. Прямая регистровая

2. Прямая автоинкрементная адресация

3. Прямая автодекрементная адресация

4. Индексная

Режимы косвенной адресации

1. Косвенная регистровая адресация

2. Косвенная автоинкрементная адресация

3. Косвенная автодекрементная адресация

4. Косвенная индексация

Режим адресации с пользованием счётчика команд

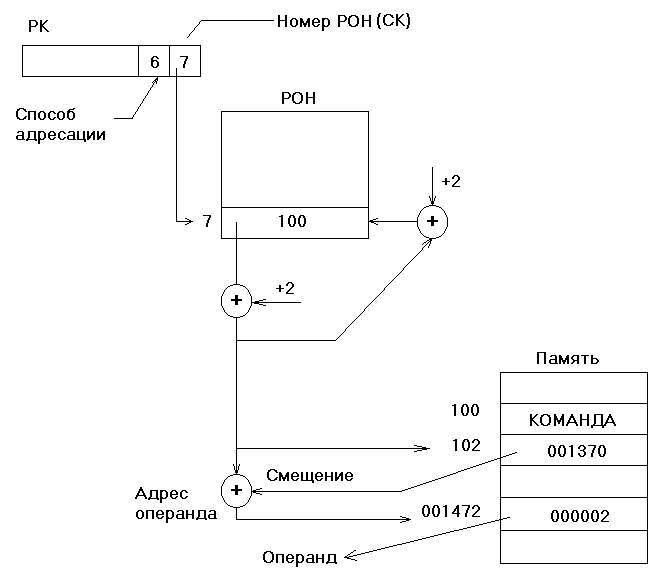

Использование для адресации операнда регистра РОН с номером 7 –счётчика команд(СК) позволяет расширить способы адресации к операнду.

1. Непосредственная

2. Абсолютная

3. Относительная. Адрес вычисляется как сумма смещения Е

4. Относительно-косвенная

Структура процессора универсальной эвм. Алгоритм выполнения двухадресной арифметической команды.

универсальная ЭВМ, - электронная вычислительная машина, предназнач. для решения широкого класса задач, имеет разветвлённую систему операций, иерархич. структуру памяти и развитую систему периферийных устройств; допускает работу практически во всех режимах взаимодействия с человеком.

Структура процессора

АЛУ – обеспечивает непосредственно исполнение арифметической или логической операции;

СОЗУ – сверхоперативная память. Высокая скорость обработки данных.

УУ – устройство управления. Извлечение, хранение команды, дешифрация и управление всеми остальными устройствами.

РК – регистр команд. Код команды в данный момент.

СК – счетчик команд. Адрес следующей команды.

ВК – выборка команды. УУ обращается к команде по адресу из СК. Обращение к памяти, считывание, запись в РК. Модификация СК, увеличение.

ДК – дешифрация команды. УУ разбирает код команды

АП – указывает адрес операндов.

Обрабатываются одновременно несколько команд, но в разных фазах!

ВО – выборка операнда (несколько). Процессор вычисляет адрес операнда, происходит обращение к памяти.

ИК – исполнение команды. АЛУ

ЗР – запись результата

Переход к следующей команде и ее 1-ой фазе.

Цикл продолжается до команды HALT или до сигнала прерывания (между ЗР и ВК). Сигнал прекращает выполнение программы, сохраняет состояние процессора. ВК и ДК присутствуют постоянно, остального может не быть! Возможна еще одна фаза DMA. В гарвордской машине память и данные разнесены (8051 - Intel).

Двухадресные команды

Двухадресные команды задают двухместные операции, т.е. операции, в которых участвуют два операнда, называемые источником и приёмником. Форматы двухадресных команд приведены на рис. 23. В зависимости от режима адресации каждого из операндов команды могут состоять из одного, двух или трёх слов, второе и третье слова задают смещения. Команды могут выполняться как над словами, так и над байтами, в последнем случае в разряде 15 кода команды записывается 1. Список и содержание двухадресных команд приведены в табл.2.

Таблица 2

Команда |

Наименование |

Содержание |

Признаки |

||||

мнемоника |

код |

N |

Z |

V |

C |

||

MOV(B) |

.ISSDD |

(dst)(src) |

Пересылка |

+ |

+ |

0 |

- |

CMP(B) |

.2SSDD |

(src)(dst) |

Сравнение |

+ |

+ |

+ |

+ |

BIT(B) |

.3SSDD |

(src)/\(dst) |

Проверка разрядов |

+ |

+ |

0 |

- |

BIС(B) |

.4SSDD |

|

Очистка разрядов |

+ |

+ |

0 |

- |

BIS(B) |

.5SSDD |

(dst)(src)\/(dst) |

Логическое "ИЛИ" Установка разрядов |

+ |

+ |

0 |

- |

ADD(B) |

06SSDD |

(dst)(dst)+(src) |

Сложение |

+ |

+ |

+ |

+ |

SUB(B) |

16SSDD |

(dst)(dst)-(src) |

Вычитание |

+ |

+ |

+ |

+ |

Рис.23

Рис.23