- •Обобщенная структура эвм. Принцип программного управления. Параметры эвм.

- •Классификация и принципы структурной организации алу.

- •Структурная организация бо алу. Состав узлов и их связи.

- •Универсальное алу на короткие операции.

- •Проектирование алб универсального алу.

- •5. Сдвигатели.

- •6. Выполнение длинных операций в универсальном алу на короткие операции.

- •7. 7. Ау для выполнения длинных операций с фиксированной запятой. Умножение кодов

- •8. Ау для выполнения длинных операций с фиксированной запятой. Умножение чисел.

- •9. Ау для выполнения длинных операций с фиксированной запятой. Деление кодов.

- •12. Двоично-десятичный сумматор. Ау, работающие в д-кодах, на его основе.

- •13. Динамические и статические озу эвм.

- •14. Расслоение памяти.

- •16. Ассоциативное зу.

- •Универсальный запоминающий элемент ассоциативного зу.

- •20. Микропрограммые уу. Проектирование фус.

- •21. Микропрограммые уу. Проектирование фамк с принудительной адресацией.

- •22. Микропрограммые уу. Проектирование фамк с естественной адресацией.

- •23. Центральный процессорный элемент секционированного мпк.

- •24. Бис схемы управления адресом микрокоманды секционированного мпк.

- •25. Построение блока обработки данных процессора на элементах секционированного мпк.

- •26. Построение блока микропрограммного управления процессора на элементах секционированного мпк.

- •27. Организация процессора. Форматы команд. Способы адресации.

- •Режимы прямой адресации

- •Структура процессора универсальной эвм. Алгоритм выполнения двухадресной арифметической команды.

- •Двухадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения одноадресной арифметической команды.

- •Одноадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения посылочных команд работы со стеком.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд ветвления.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд работы с подпрограммами.

- •Команды работы с подпрограммами

- •33. Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •34. Интерфейсы.

12. Двоично-десятичный сумматор. Ау, работающие в д-кодах, на его основе.

Универсальное арифметическое устройство на базе двоично-десятичного сумматора.

Устройство представленное на схеме (рис. 7.5) является параллельно-последовательным, т.е. обеспечивает обработку, прием и выдачу информации по тетрадам. Устройство включает:

три регистра - Р1,Р2 и Р3;

двоично-десятичный сумматор - SM;

триггер переноса - ТП;

счётчик разряда - СР;

счётчик значащей цифры - СЗЦ.

Все

регистры сдвигающие и сдвиг осуществляется

тетрадно. Разрядность регистров n, где

n - количество тетрад.

Операция сложения.

Включает вначале запоминание регистров слагаемых Р1 и Р2 (2 n тактов). Далее начинается сложение (n тактов). В каждом такте в сумматор поступают одноименные слагаемые и перенос, сумматор формирует очередную цифру и перенос в следующий такт. Очередная цифра суммы поступает в регистр Р2. Т. о. через n тактов в Р2 зафиксируется сумма, а в Р1 восстановится первое слагаемое. Признак переполнения - перенос после последнего такта.

Умножение.

Предполагает подготовительную часть - перепись множителя в Р3 (за n тактов). Затем начинается операция умножения, которая заключается в том, что в счётчик разрядов записывается n. Регистр Р2 обнуляется, m раз выполняется следующая процедура: очередная цифра множителя записывается в СЗЦ. Далее выполняется столько раз сложение Р1 и Р2, сколько загрузилось в счётчик. После этого счётчик разрядов уменьшается на единицу и алгоритм повторяется.

13. Динамические и статические озу эвм.

Статические.

В настоящее время ОЗУ строятся на полупроводниковой технике - биполярных и МОП больших интегральных схемах.

Запоминающий элемент в статическом ЗУ - триггер. Запоминающая среда - матрица триггеров. Эта ячейка подключается к четырём проводам: 2 - шины выборки, 2 другие - чтения и записи (разрядные провода), т. к. к этим линиям подключены все триггеры одноименных разрядов кристалла. Ячейка работает в трех режимах: хранение, чтение, запись. Ячейка находится в режиме хранения тогда, когда она не выбрана, т. е. на координатных проводах Uх, Uу (хотя бы на одном из них) нуль. Ячейка выбрана, если обе координатные шины имеют высокий потенциал (Uх=Uу=2,5В для ТТЛ). Запись - ячейка выбрана, но мы принудительно на одной из шин Uр1,Uр0 устанавливаем низкий потенциал ("0"). Организация ячейки ЗУ на рисунке.

БУ - буферный усилитель - обеспечивает высокое импедансное состояние в режиме хранения. В некоторых кристаллах БУ управляется сигналом DR/WR - и отключается сигналом записи.

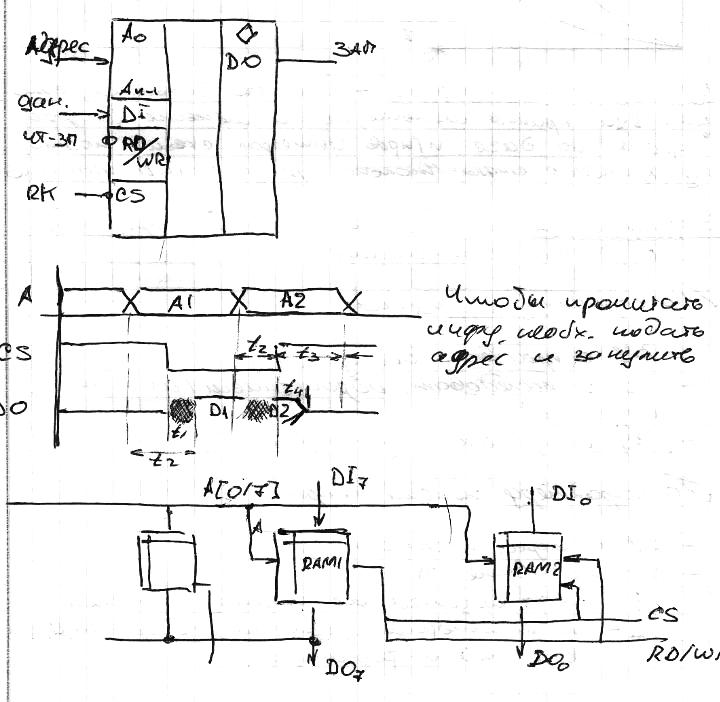

Микросхема статического ОЗУ на рисунке +временные диаграммы при чтении:

Во время действия CS допускается менять адрес. Заштриховано - время переходных процессов.

tсохр - после отключения сигнал сохраняется.

tр - переходные процессы.

Временные диаграммы при записи:

Правило

вложенности - сигнал чтение/запись

должен быть вложен внутрь сигналов

данных и адреса, т. к. необходимо надёжное

выполнение записи. Если во время записи

будет изменяться адрес, могут быть

испорчены данные в нескольких ячейках.

Правило

вложенности - сигнал чтение/запись

должен быть вложен внутрь сигналов

данных и адреса, т. к. необходимо надёжное

выполнение записи. Если во время записи

будет изменяться адрес, могут быть

испорчены данные в нескольких ячейках.

CS - может установиться раньше или позже сигнала записи

Длительность сигнала записи должна быть больше некоторого времени, это время должно быть согласовано с паспортными данными кристалла. Некоторые кристаллы многоразрядные - 4,8,16.

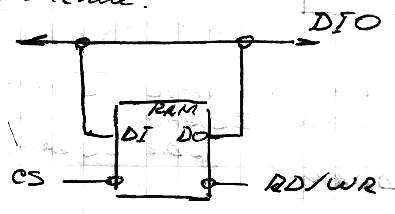

Некоторые типы кристаллов имеют совмещенный вход/выход.

В некоторых типах кристаллов два сигнала CS, один из которых управляет выбором кристалла, а другой только выходом.

Оперативная статич. память применяется как буферная (компонент КЭШ).

Динамические.

В них запоминающий элементом является паразитная ёмкость МОП транзистора. Матрица запоминающих элементов - в общем случае это матрица транзисторов. Такая организация обеспечивает считывание целиком строки. Статические ЗУ имеют емкость до 64 Кбит (максимум 256 Кбит). Динамические - 1,4,8 Мбит в одном кристалле.

В отличие от статических ЗУ, которые хранят информацию пока включено питание, в динамических ЗУ необходима постоянная регенерация информации, однако при этом для хранения одного бита в ДОЗУ нужны всего 1-2 транзистора и накопительный конденсатор (рис). Такие схемы более компактны.

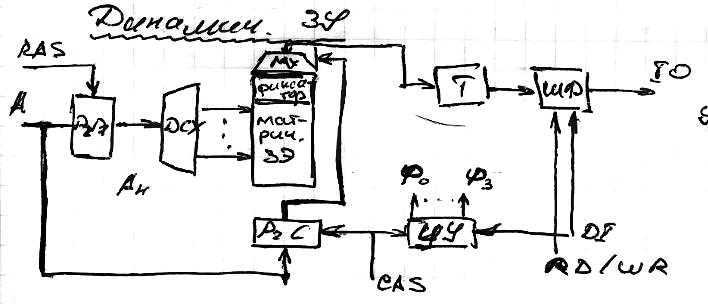

Структурная схема:

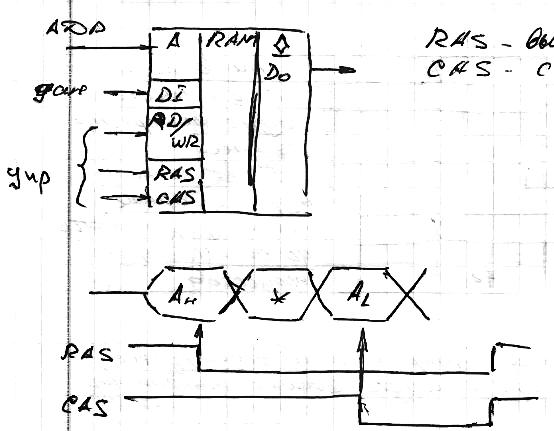

Микросхема динамического ОЗУ+Диаграммы:

Т. к. кристаллы получаются большие, то выходов для адреса делают в два раза меньше и управляется адрес двумя строками RAS и CAR. Т - выходной триггер;

PR - регистр строк;

РС - регистр столбцов;

УУ - устройство управления.

ЗУ работает в четырёх режимах: чтение, запись, хранение, регенерация. Чтение начинается с подачи половины адреса и подачи строба (загрузка PR). Затем вторая половина адреса и строб CAS (по нему на регистре РС фиксируется вторая половина адреса и одна из колонок) подключается к УВ.

Практически во всех типах динамических ОЗУ на время записи выходной каскад блокируется.

CAS переднем фронтом фиксирует А, DI. В некоторых типах кристаллов допускается операция записи при неизменном значении RAS, также допускается чтение/запись при неизменном RAS в ту же или другую ячейку. Регенерация - подача RAS и CAS при WR/RD=1.

Организация ЗУ с динамическим управлением.

Сложности связаны с регенерацией. Есть два подхода к её организации: внешняя и скрытая. При внешней регенерации ей управляет пользователь ОЗУ. Он обязан не позже чем через 2мс выполнить регенерацию. Допускается не делать этого при особых режимах (например, при непрерывном чтении информации). При скрытой регенерации информация об этом находится внутри ОЗУ. Пользователь ничего не видит