- •Обобщенная структура эвм. Принцип программного управления. Параметры эвм.

- •Классификация и принципы структурной организации алу.

- •Структурная организация бо алу. Состав узлов и их связи.

- •Универсальное алу на короткие операции.

- •Проектирование алб универсального алу.

- •5. Сдвигатели.

- •6. Выполнение длинных операций в универсальном алу на короткие операции.

- •7. 7. Ау для выполнения длинных операций с фиксированной запятой. Умножение кодов

- •8. Ау для выполнения длинных операций с фиксированной запятой. Умножение чисел.

- •9. Ау для выполнения длинных операций с фиксированной запятой. Деление кодов.

- •12. Двоично-десятичный сумматор. Ау, работающие в д-кодах, на его основе.

- •13. Динамические и статические озу эвм.

- •14. Расслоение памяти.

- •16. Ассоциативное зу.

- •Универсальный запоминающий элемент ассоциативного зу.

- •20. Микропрограммые уу. Проектирование фус.

- •21. Микропрограммые уу. Проектирование фамк с принудительной адресацией.

- •22. Микропрограммые уу. Проектирование фамк с естественной адресацией.

- •23. Центральный процессорный элемент секционированного мпк.

- •24. Бис схемы управления адресом микрокоманды секционированного мпк.

- •25. Построение блока обработки данных процессора на элементах секционированного мпк.

- •26. Построение блока микропрограммного управления процессора на элементах секционированного мпк.

- •27. Организация процессора. Форматы команд. Способы адресации.

- •Режимы прямой адресации

- •Структура процессора универсальной эвм. Алгоритм выполнения двухадресной арифметической команды.

- •Двухадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения одноадресной арифметической команды.

- •Одноадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения посылочных команд работы со стеком.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд ветвления.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд работы с подпрограммами.

- •Команды работы с подпрограммами

- •33. Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •34. Интерфейсы.

14. Расслоение памяти.

Допустим, имеем модуль памяти, который состоит из нескольких модулей.

М1, М2, М3 – три модуля памяти, которые могут работать параллельно и независимо. Каждый модуль обладает конечным быстродействием.

τ – время обращения цикла к памяти.

2 подхода к реализации метода расслоения:

построение памяти с буферизацией адресов.

построение памяти с буферизацией данных.

Буферизация адресов.

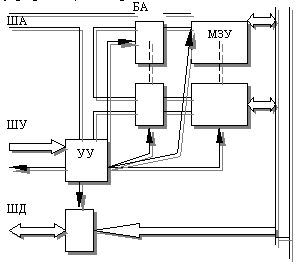

Перед модулями памяти ставится буфер адресов (БА). В простейшем случае это регистр в сложном очередь адресов (несколько регистров).

Как сделать так, чтобы обращение было к разным модулей? Это делается за счет разделения адресного пространства: адреса модуля делятся поочередно, (если два модуля, то чередование через 1, 4 модуля – 0,4, - в первом модуле, 1,5 – во втором и т.д.)

УУ анализирует занятость буфера. Если он пустой, то цикл обр-я фиксируется в нем, если нет, т.е. туда приходит адрес и выдается сигнал на выполнение.

Адреса ячеек нумеруют так, чтобы модули памяти были как единое целое, т.е. подряд идущие адреса разным модулям.

ШФ - шинный формирователь

Такая организация требует усложнения устройств управления.

Буферизация данных.

Модули памяти включены параллельно по ША, и работают параллельно (обращение ко всем модулям происходит одновременно). Если число модулей =2n, то часть разрядов общая, а часть разрядов задают номер модуля, т.е. память с широким выборным УУ анализирует адрес, который поступил.

На входе буферный регистр памяти (только за одно обращение из памяти забирается не одно (допустим слово), а два и затем нам не надо лезть в память за вторым словом, а берем его и буфера данных).

Модули памяти работают синхронно. Считывается длинное машинное слово, следующее можно извлекать из буфера, а не из памяти. Такая память будет давать выигрыш, если обращение будет по подряд идущим адресам, но зато дёшево.

По Коннову:

ОЗУ разбивается физически, а не логически на 4 блока, представляющих собой законченное ОЗУ со своими схемами управления и т.д.

Пусть время обращения 100 нс (рис). Эффективно только тогда, когда последовательные обращения идут к разным блокам памяти. Так как обычно информация располагается в соседних адресах, то используют подобную организацию распределения адресов, чтобы попадать в разные модули. Каждый модуль имеет внутри себя буферный регистр адреса и буферный регистр данных. Каждый блок формирует сигнал готовности ("0" - занят, "1" - готов).

На рисунке младшая часть адреса указывает блок, старшая часть - адрес внутри блока. Блок управления (БУ) анализирует сигналы готовности всех блоков. Если в момент обращения нужный блок занят, БУ убирает общий сигнал готовности, растягивая процесс обращения. Количество слоёв от двух до восьми.

15. Регистровая память.

Регистровые ЗУ обычно встраиваются в ЦП. Их отличие от ОЗУ в том, что они позволяют одновременно читать и записывать информацию. Более того, есть регистровые ЗУ позволяющие читать и записывать несколько ячеек.

Дешифратор используется для записи информации (по адресу АВ). Регистры выполняют одноступенчатыми, а на выходе ставят буферный регистр: