Регистры

ЦП

Данная глава описывает основные регистры

ЦП TMS320C55x (C55x) DSP и idle

регистры, которые используются для

определения и мониторинга энергосберегающих

idle конфигураций. В секции

2.2 представлена таблица, которая

показывает, где регистры ЦП размещены

в пространстве данных. Остальные секции

содержат более детальную информацию

о ЦП и о idle регистрах.

Тема

Страница

2.1

Алфавитный

список регистров

2-2

.

. . . . . . . . . . . . . . . . . . . . . . . .

2.2

Регистры,

отображенные в карте памяти

2-4

.

. . . . . . . . . . . . . . . . .

2.3

Аккумуляторы

(AC0-AC3)

2-9

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4

Регистры

перехода (TRN0, TRN1)

2-10

.

. . . . . . . . . . . . . . . . . . . . . .

2.5

Буферные

регистры (T0-T3)

2-11

.

. . . . . . . . . . . . . . . . . . . . . . . . . .

2.6

Регистры,

используемые для пространств I/O

и данных

2-12

.

. .

2.7

Регистры

хода программ (PC, RETA, CFCT)

2-21

.

. . . . . . . . . . . . . .

2.8

Регистры

для управления прерываниями

2-23

.

. . . . . . . . . . . . . . .

2.9

Регистры

для управления циклами повторения

2-34

.

. . . . . . . . .

2-36

.

. . . . . . . . . . . . . . . . .

2-1

2-12.10 Регистры состояния (st0_55-st3_55)

Глава 2

2-2

2.1

Алфавитный

список регистров

Таблица 2-1 перечисляет

регистры в алфавитном порядке. За более

подробной информацией о конкретном

регистре обращайтесь к последней

колонке данной таблицы.

Таблица

2-1. Алфавитный список регистров

Аббревиатура

Название

Размер

Смотрите

...

AC0-AC3

Аккумуляторы

с 0 по 3

40

бит каждый

Страница

2-9

AR0-AR7

Вспомогательные

регистры с 0 по 7

16

бит каждый

Страница

2-12

BK03,

BK47, BKC

Регистры

длины кольцевого буфера

16

бит каждый

Страница

2-16

BRC0,

BRC1

Счетчики

блочного повторения 0 и 1

16

бит каждый

Страница

2-34

BRS1

BRC1

регистры сохранения

16

бит

Страница

2-34

BSA01,

BSA23, BSA45, BSA67, BSAC

Регистры

стартового адреса кольцевого буфера

16

бит каждый

Страница

2-15

CDP

Коэффициент

указателя данных (нижняя часть XCDP)

16

бит

Страница

2-14

CDPH

Верхняя

часть XCDP

7

бит

Страница

2-14

CFCT

Контекстные

регистры управления потоком

8

бит

Страница

2-21

CSR

Регистр

одиночного повторения

16

бит

Страница

2-34

DBIER0,

DBIER1

Отладочные

рег. разрешения прерыв. 0 и 1

16

бит каждый

Страница

2-30

DP

Регистр

страницы данных (нижняя часть XDP)

16

бит

Страница

2-17

DPH

Верхняя

часть XDP

7

бит

Страница

2-17

IER0,

IER1

Регистры

разрешения прерываний 0 и 1

16

бит каждый

Страница

2-28

IFR0,

IFR1

Регистры

флагов прерываний 0 и 1

16

бит каждый

Страница

2-25

IVPD,

IVPH

Указатели

векторов прерываний

16

бит каждый

Страница

2-23

PC

Счетчик

команд

24

бита

Страница

2-21

PDP

Регистр

страницы периферийных данных

9

бит

Страница

2-18

REA0,

REA1

Рег.

конечного адреса блочного повтор. 0 и

1

24

бит каждый

Страница

2-34

RETA

Регистр

адреса возврата

24

бита

Страница

2-21

RPTC

Счетчик

одиночного повторения

16

бит

Страница

2-34

RSA0,

RSA1

Рег.

стартового адреса блочного повтор. 0 и

1

24

бита каждый

Страница

2-34

Алфавитный

список регистров

Алфавитный

список регистров

2-3

Регистры

ЦП

Таблица

2-1. Алфавитный список регистров

(продолжение)

Аббревиатура

Смотрите

...

Размер

Название

SP

Указатель

стека данных

16

бит

Страница

2-18

SPH

Верхняя

часть XSP и XSSP

7

бит

Страница

2-18

SSP

Указатель

стека системы

16

бит

Страница

2-18

ST0_55-ST3_55

Регистры

состояния с 0 по 3

16

бит каждый

Страница

2-36

T0-T3

Буферные

регистры

16

бит каждый

Страница

2-11

TRN0,

TRN1

Регистры

перехода 0 и 1

16

бит каждый

Страница

2-10

XAR0-XAR7

Расширенные

вспомогат. регистры с 0 по 7

23

бит каждый

Страница

2-12

XCDP

Расширенный

коэф. указателя данных

23

бита

Страница

2-14

XDP

Расширенный

регистр страницы данных

23

бита

Страница

2-17

XSP

Расширенный

указатель стека данных

23

бита

Страница

2-18

XSSP

Расширенный

указатель стека системы

23

бита

Страница

2-18 Алфавитный

список регистров

Алфавитный

список регистров

2-4

2.2

Регистры,

отображенные в карте памяти

Замечание:

1)

ST0_55, ST1_55 и ST3_55 доступны каждый по двум

адресам. По одному адресу все TMS320C55x

биты доступны. По другому адресу

(защищенному) определенные биты не

могут быть модифицированы. Защищенный

адрес обеспечивает TMS320C54x кодом, который

записывается в ST0, ST1 и PMST.

2)

T3, RSA0L, REA0L и SP доступны каждый по двум

адресам. Для доступа через DP режим

прямой адресации необходим доступ к

регистрам, отображенным в карте памяти,

ассемблер замещает старший из двух

адресов: T3 = 23h (не 0Eh), RSA0L = 3Dh (не 1Bh),

REA0L = 3Fh (не 1Ch), SP = 4Dh (не 18h).

3)

Любая C55x инструкция,

которая загружает BRC1, загружает то же

значение BRS1.

Таблица

2-2. Регистры, отображенные в карте

памяти

Адреса

Регистр

Описание

Битовый

диапазон

Смотрите

...

00

0000h

IER0

Регистр

разрешения прерываний 0

15-2

Страница

2-28

00

0001h

IFR0

Регистр

флага прерываний 0

15-2

Страница

2-25

00

0002h

(для

C55x кода)

ST0_55

Регистр

состояния 0

15-0

Страница

2-36

Замечание:

Адрес 00 0002h является “родным” TMS320C55x

кодом для доступа к ST0_55. TMS320C54x код,

написанный для доступа к ST0, должен

использовать адрес 00 0006h для доступа к

ST0_55.

00

0003h

(для

C55x кода)

ST1_55

Регистр

состояния 1

15-0

Страница

2-36

Замечание:

Адрес 00 0003h является “родным” TMS320C55x

кодом для доступа к ST1_55. TMS320C54x код,

написанный для доступа к ST1, должен

применять адрес 00 0007h для доступа к

ST1_55.

00

0004h

(для

C55x кода)

ST3_55

Регистр

состояния 3

15-0

Страница

2-36

Замечание:

Адрес 00 0004h является “родным” TMS320C55x

кодом для доступа к ST3_55. TMS320C54x код,

написанный для доступа к регистру PMST,

должен использовать адрес 00 001Dh

для доступа к ST3_55.

00

0005h

-

Зарезервировано

(не использовать данный адрес)

-

Регистры,

отображенные в карте памяти

Регистры,

отображенные в карте памяти

Регистры,

отображенные в карте памяти

2-5

Регистры

ЦП

Таблица

2-2. Регистры, отображенные в карте

памяти (продолжение)

Адреса

Смотрите

...

Битовый

диапазон

Описание

Регистр

00

0006h

(для

C54x кода)

ST0

(ST0_55)

Регистр

состояния 0

15-0

Страница

2-36

Замечание:

Адрес 00 0006h является защищенным адресом

ST0_55. Этот адрес предназначен для кода

TMS320C54x, написанного для доступа к ST0.

“Родной” TMS320C55x код должен применять

адрес 00 0002h для доступа к ST0_55.

00

0007h

(для

C54x кода)

ST1

(ST1_55)

Регистр

состояния 1

15-0

Страница

2-36

Замечание:

Адрес 00 0007h является защищенным адресом

ST1_55. Этот адрес предназначен для кода

TMS320C54x, написанного для доступа к ST1.

“Родной” TMS320C55x код должен использовать

адрес 00 0003h для доступа к ST1_55.

00

0008h

00

0009h

00

000Ah

AC0L

AC0H

AC0G

Аккумулятор

0

15-0

31-16

39-32

Страница

2-9

00

000Bh

00

000Ch

00

000Dh

AC1L

AC1H

AC1G

Аккумулятор

1

15-0

31-16

39-32

Страница

2-9

00

000Eh

T3

Буферный

регистр 3

15-0

Страница

2-11

00

000Fh

TRN0

Регистр

перехода 0

15-0

Страница

2-10

00

0010h

AR0

Вспомогательный

регистр 0

15-0

Страница

2-12

00

0011h

AR1

Вспомогательный

регистр 1

15-0

Страница

2-12

00

0012h

AR2

Вспомогательный

регистр 2

15-0

Страница

2-12

00

0013h

AR3

Вспомогательный

регистр 3

15-0

Страница

2-12

00

0014h

AR4

Вспомогательный

регистр 4

15-0

Страница

2-12

00

0015h

AR5

Вспомогательный

регистр 5

15-0

Страница

2-12

00

0016h

AR6

Вспомогательный

регистр 6

15-0

Страница

2-12

00

0017h

AR7

Вспомогательный

регистр 7

15-0

Страница

2-12

00

0018h

SP

Указатель

стека данных

15-0

Страница

2-18

00

0019h

BK03

Регистр

длины кольцевого буфера для AR0-AR3

15-0

Страница

2-16

Замечание:

В TMS320C54x-совместимом режиме (C54CM = 1) BK03

используется для всех вспомогательных

регистров. C54CM

является

битом в регистре состояния 1 (ST1_55).

Регистры состояния описаны в начале

страницы 2-36.

00

001Ah

BRC0

Счетчик

блочного повторения 0

15-0

Страница

2-34

Регистры,

отображенные в карте памяти

2-6

Таблица

2-2. Регистры, отображенные в карте памяти

(продолжение)

Адреса

Смотрите

...

Битовый

диапазон

Описание

Регистр

00

001Bh

RSA0L

Нижняя

часть регистра стартового адреса

блочного повторения 0

15-0

Страница

2-34

00

001Ch

REA0L

Нижняя

часть регистра конечного адреса блочного

повторения 0

15-0

Страница

2-34

00

001Dh

(для

C54x кода)

PMST

(ST3_55)

Регистр

состояния 3

15-0

Страница

2-36

Замечание:

Адрес 00 001Dh является защищенным адресом

ST3_55. Этот адрес предназначен для кода

TMS320C54x, написанного для доступа к регистру

состояния режима процессора (PMST).

“Родной” TMS320C55x код должен использовать

адрес 00 0004h для доступа к ST3_55.

00

001Eh

XPC

Данный

адрес установлен отдельно для

совместимости с TMS320C54x кодом, который

использует XPC.

7-0

-

00

001Fh

-

Зарезервирован

(не использовать этот адрес)

-

00

0020h

T0

Буферный

регистр 0

15-0

Страница

2-11

00

0021h

T1

Буферный

регистр 1

15-0

Страница

2-11

00

0022h

T2

Буферный

регистр 2

15-0

Страница

2-11

00

0023h

T3

Буферный

регистр 3

15-0

Страница

2-11

00

0024h

00

0025h

00

0026h

AC2L

AC2H

AC2G

Аккумулятор

2

15-0

31-16

39-32

Страница

2-9

00

0027h

CDP

Коэффициент

указателя данных

15-0

Страница

2-14

00

0028h

00

0029h

00

002Ah

AC3L

AC3H

AC3G

Аккумулятор

3

15-0

31-16

39-32

Страница

2-9

00

002Bh

DPH

Старшая

часть расширенного регистра страницы

данных

6-0

Страница

2-17

00

002Ch

00

002Dh

-

-

Зарезервирован

(не использовать этот адрес)

-

-

00

002Eh

DP

Регистр

страницы данных

15-0

Страница

2-17

00

002Fh

PDP

Регистр

страницы периферийных данных

8-0

Страница

2-18

Регистры,

отображенные в карте памяти

2-7

Регистры

ЦП

Таблица

2-2. Регистры, отображенные в карте

памяти (продолжение)

Адреса

Смотрите

...

Битовый

диапазон

Описание

Регистр

00

0030h

BK47

Регистр

длины кольцевого буфера для AR4-AR7

15-0

Страница

2-16

00

0031h

BKC

Регистр

длины кольцевого буфера для CDP

15-0

Страница

2-16

00

0032h

BSA01

Регистр

стартового адреса кольцевого буфера

для AR0 и AR1

15-0

Страница

2-15

00

0033h

BSA23

Регистр

стартового адреса кольцевого буфера

для AR2 и AR3

15-0

Страница

2-15

00

0034h

BSA45

Регистр

стартового адреса кольцевого буфера

для AR4 и AR5

15-0

Страница

2-15

00

0035h

BSA67

Регистр

стартового адреса кольцевого буфера

для AR6 и AR7

15-0

Страница

2-15

00

0036h

BSAC

Регистр

стартового адреса кольцевого буфера

для CDP

15-0

Страница

2-15

00

0037h

-

Зарезервировано

под BIOS, 16 - разр. регистр, который будет

применяться при старте, как ячейка

хранения указателя таблицы данных,

необходимой для работы BIOS.

-

00

0038h

TRN1

Регистр

перехода 1

15-0

Страница

2-10

00

0039h

BRC1

Счетчик

блочного повторения 1

15-0

Страница

2-34

00

003Ah

BRS1

BRC1

регистр сохранения

15-0

Страница

2-34

00

003Bh

CSR

Регистр

одиночного повторения

15-0

Страница

2-34

00

003Ch

00

003Dh

RSA0H

RSA0L

Регистр

стартового адреса блочного повторения

0

23-16

15-0

Страница

2-34

00

003Eh

00

003Fh

REA0H

REA0L

Регистр

конечного адреса блочного повторения

0

23-16

15-0

Страница

2-34

00

0040h

00

0041h

RSA1H

RSA1L

Регистр

стартового адреса блочного повторения

1

23-16

15-0

Страница

2-34

00

0042h

00

0043h

REA1H

REA1L

Регистр

конечного адреса блочного повторения

1

23-16

15-0

Страница

2-34

00

0044h

RPTC

Счетчик

одиночного повторения

15-0

Страница

2-34

Регистры,

отображенные в карте памяти

2-8

Таблица

2-2. Регистры, отображенные в карте

памяти (продолжение)

Адреса

Смотрите

...

Битовыйдиапазон

Описание

Регистр

00

0045h

IER1

Регистр

разрешения прерывания 1

10-0

Страница

2-28

00

0046h

IFR1

Регистр

флага прерывания 1

10-0

Страница

2-25

00

0047h

DBIER0

Отладочный

рег. разреш. прерыв. 0

15-2

Страница

2-30

00

0048h

DBIER1

Отладочный

рег. разреш. прерыв. 1

10-0

Страница

2-30

00

0049h

IVPD

Указатель

вектора прерывания для векторов DSP

15-0

Страница

2-23

00

004Ah

IVPH

Указатель

вектора прерывания для хост векторов

15-0

Страница

2-23

00

004Bh

ST2_55

Регистр

состояния 2

15-0

Страница

2-36

00

004Ch

SSP

Системный

указатель стека

15-0

Страница

2-18

00

004Dh

SP

Указатель

стека данных

15-0

Страница

2-18

00

004Eh

SPH

Старш.

часть расшир. указателей стека

6-0

Страница

2-18

00

004Fh

CDPH

Старшая

часть расширенного коэффициента

указателя данных

6-0

Страница

2-14

00

0050h по

00

005Fh

-

Зарезервирован

(не использовать этот адрес)

-

2-9

Регистры

ЦП

2.3

Аккумуляторы

(AC0-AC3)

ЦП

содержит четыре 40 - разрядных аккумулятора:

AC0, AC1, AC2 и AC3 (смотрите рисунок 2-1). Основной

функцией данных регистров является

содействие в операциях с данными в

следующих частях блока D:

арифметическом логическом устройстве

(ALU),

блоках умножителей-накопителей (MAC)

и сдвигателе. Все четыре аккумулятора

эквивалентны; любая инструкция, которую

применяет аккумулятор, может быть

запрограммирована для использования

каждым из четырех аккумуляторов. Каждый

аккумулятор разделен на младшее слово

(ACxL)

и старшее слово (ACxH),

и восемь сторожевых разрядов (ACxG).

Можно получить доступ к каждой из этих

частей индивидуально, используя режимы

адресации, которые обращаются к

регистрам, отображенным в карте памяти.

В

TMS320C54x-совместимом режиме (C54CM = 1)

аккумуляторы AC0 и AC1 соответствуют

аккумуляторам A

и B

TMS320C54x.

Рисунок

2-1. Аккумуляторы

39-32

31-16

15-0

AC0

AC0G

AC0H

AC0L

AC1

AC1G

AC1H

AC1L

AC2

AC2G

AC2H

AC2L

AC3

AC3G

AC3H

AC3L

Аккумуляторы

(AC0-AC3)

Аккумуляторы

(AC0-AC3)

2-10

2.4

Регистры

перехода (TRN0, TRN1)

Два регистра перехода

(смотрите рисунок 2-2) используются в

инструкциях сравнения и выбора

экстремума:

Синтаксис,

который производит выбор двух 16 -

разрядных экстремума, обновляет TRN0

и TRN1

на основе сравнения старших и младших

слов двух аккумуляторов. TRN0

обновляется на основе сравнения старших

слов аккумулятора; TRN1

– на основе сравнения младших слов.

Синтаксис,

который осуществляет выбор одного 40 -

разрядного экстремума, обновляет

выбранный регистр перехода (TRN0

или TRN1)

на основе сравнения 40-ка бит двух

аккумуляторов.

TRN0 и TRN1 способны удерживать решение

перехода для новой метрики в реализациях

алгоритма Виттерби.

Рисунок

2-2. Регистры перехода

15-0

TRN0

TRN1

Регистры

перехода (TRN0, TRN1)

Регистры

перехода (TRN0, TRN1)

2-11

Регистры

ЦП

2.5

Буферные

регистры (T0-T3)

ЦП включает в себя четыре 16 - разрядных

универсальных буферных регистра: T0-T3

(смотрите рисунок 2-3). Вот несколько

действий, которые вы можете совершать

при помощи буферных регистров:

Удерживание одного множителя памяти

для инструкций умножения,

умножения-накопления, и умножения-вычитания.

Удерживание

числа сдвигов используемого в инструкциях

сложения, вычитания и загрузки,

производимых в блоке D.

Отслеживание

значений указателя путем обмена

содержимого вспомогательных регистров

(AR0-AR7)

и буферных регистров (используя

инструкцию обмена).

Удерживание

метрики перехода “бабочки” Виттерби

для х 16 - разрядных операций, осуществляемых

в ALU

блока А.

Рисунок

2-3. Буферные регистры

15-0

T0

T1

T2

T3

Буферные

регистры (T0-T3)

Буферные

регистры (T0-T3)

2-12

2.6

Регистры,

используемые для пространств адресных

данных и I/O

Данная секция описывает

следующие регистры:

Регистры

Функция

Смотрите...

XAR0-XAR7

и

AR0-AR7

Указывает на

значение в пространстве данных для

доступа через режим косвенной адресации

Страница

2-12

XCDP

и CDP

Указывает на

значение в пространстве данных для

доступа через режим косвенной адресации

Страница

2-14

BSA01,

BSA23, BSA45, BSA67, BSAC

Определяет стартовый

адрес кольцевого буфера, который будет

добавлен к указателю

Страница

2-15

BK03,

BK47, BKC

Определяет

длину кольцевого буфера

Страница

2-16

XDP

и DP

Определяет

стартовый адрес для доступа через DP

режим прямой адресации

Страница

2-17

PDP

Опред.

страницу данных периферии для доступа

к пространству I/O

Страница

2-18

XSP

и SP

Указывает

на значение в стеке данных

Страница

2-18

XSSP

и SSP

Указывает

на значение в системном стеке

Страница

2-18

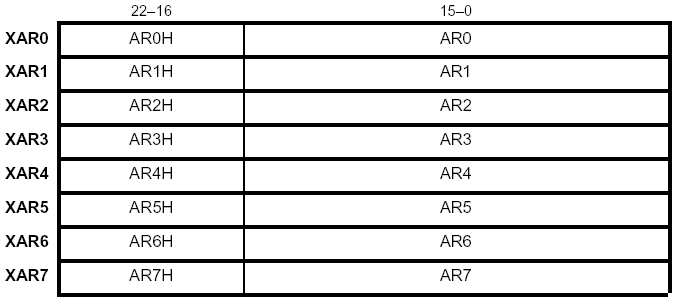

2.6.1

Вспомогательные

регистры (XAR0-XAR7 / AR0-AR7)

ЦП включает в себя восемь расширенных

вспомогательных регистров XAR0-XAR7

(смотрите рисунок 2-4 и Таблицу 2-3). Каждая

старшая часть (например, AR0H) используется

для определения 7- разрядной главной

страницы данных для доступа к пространству

данных. Каждая младшая часть (например,

AR0) может применяться как:

16

- разрядное смещение к 7- разрядной

главной странице данных (для формирования

23 - разрядного адреса).

Адрес бита (в инструкциях, доступ к

которым осуществляется индивидуальными

битами или парами бит)

Универсальный регистр или счетчик

Регистры,

используемые для пространства адресных

данных и пространства I/O

(ввода/вывода)

Регистры,

используемые для пространства адресных

данных и пространства I/O

(ввода/вывода)

2-13

Регистры

ЦП

Рисунок

2-4. Расширенные вспомогательные регистры

и их части

Таблица

2-3. Расширенные вспомогательные регистры

и их части

Регистр

Название

Доступность

XARn

Расширенный

вспомогательный регистр n

Доступен

только через выделенные инструкции.

XARn не является регистром, отображенным

в карте памяти.

ARn

Вспомогательный

регистр n

Доступен через

выделенные инструкции и как регистр,

отображенный в карте памяти.

ARnH

Старшая

часть расширенного вспомогательного

регистра n

Индивидуально не

доступен. Для доступа к ARnH

вы должны обратиться к XARn.

XAR0-XAR7

или AR0-AR7 применяются в AR режиме косвенной

адресации и двойном AR режиме косвенной

адресации. Базовые арифметические,

логические и сдвиговые операции могут

производиться в AR0-AR7 в ALU

блока А. Данные операции могут

осуществляться в параллель с модификацией

адресов, происходящих во вспомогательных

регистрах в блоке генерации адресных

данных (DAGEN).

Регистры,

используемые для пространства адресных

данных и пространства I/O

Регистры,

используемые для пространства адресных

данных и пространства I/O

2-14

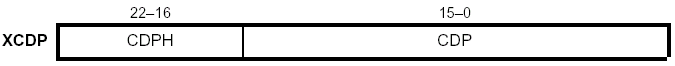

2.6.2

Коэффициент

указателя данных (coefficient

data

pointer)

(XCDP / CDP)

ЦП

включает в себя в карте памяти коэффициент

указателя данных (coefficient

data

pointer)

CDP

и связанный регистр расширения CDPH:

15-0

CDP

15-7

6-0

Зарезервирован

CDPH

ЦП может соединить

два для формирования расширенного CDP,

который обозначается XCDP (смотрите

рисунок 2-5 и Таблицу 2-4). Старшая часть

(CDPH) применяется для определения 7 -

разрядной главной страницы данных для

доступа к пространству данных. Младшая

часть (CDP) может использоваться как:

16

- разрядное смещение к 7 - разрядной

главной странице данных (для формирования

23- разрядного адреса).

Адрес бита (в инструкциях, доступ к

которым осуществляется индивидуальными

битами или парами бит)

Универсальный регистр или счетчик

Рисунок

2-5. Расширенный коэффициент указателя

данных и его части

Таблица

2-4. Расширенный коэффициент указателя

данных и его части

Регистр

Название

Доступность

XCDP

Расширенный

коэффициент указателя данных

Доступен

только через выделенные инструкции.

XCDP

не является регистром, отображенным в

карте памяти.

CDP

Коэффициент

указателя данных

Доступен через

выделенные инструкции и как регистр,

отображенный в карте памяти.

CDPH

Старшая

часть расширенного коэффициента

указателя данных

Доступен через

выделенные инструкции и как регистр,

отображенный в карте памяти.

Регистры,

используемые для пространства адресных

данных и пространства I/O

Регистры,

используемые для пространства адресных

данных и пространства I/O

2-15

Регистры

ЦП

XCDP

или CDP используются в CDP режиме косвенной

адресации. CDP может применяться в любой

инструкции, которая предоставляет

доступ к отдельным значениям пространства

данных; хотя CDP преимущественно

используется в инструкциях двойного

умножения-накопления (MAC), потому что

он обеспечивает третий, независимый

операнд к оператору двойного MAC

блока D.

2.6.3

Регистры

стартового адреса кольцевого буфера

(BSA01, BSA23, BSA45, BSA67, BSAC)

ЦП содержит пять 16 - разрядных регистров

стартового адреса кольцевого буфера

(смотрите рисунок 2-6) для возможности

определения кольцевого буфера со

стартового адреса, не связанного

ограничением выравнивания.

Рисунок

2-6. Регистры стартового адреса кольцевого

буфера

15-0

BSA01

BSA23

BSA45

BSA67

BSAC

Каждый

регистр стартового адреса буфера связан

с конкретным указателем или указателями

(смотрите Таблицу 2-5). Стартовый адрес

буфера добавляется к указателю только

тогда, когда указатель сконфигурирован

в регистре состояния ST2_55

для кольцевой адресации.

Таблица

2-5. Регистры стартового адреса кольцевого

буфера и указатели

Регистр

Указатель

Главная

страница данных ...

BSA01

AR0

или

AR1

AR0H

BSA23

AR2

или

AR3

AR2H

BSA45

AR4

или

AR5

AR4H

BSA67

AR6

или

AR7

AR6H

BSAC

CDP

CDPH

Регистры,

используемые для пространства адресных

данных и пространства I/O

Регистры,

используемые для пространства адресных

данных и пространства I/O

2-16

В качестве примера

использования стартового адреса буфера

рассмотрите следующую инструкцию:

MOV

*AR6, T2

;

Загрузка T2 со значением из слов кольцевого

буфера, ссылающихся на XAR6.

В

данном примере при AR6, сконфигурированном

для кольцевой адресации, адрес

генерируется по нижеследующему

выражению. Значение главной страницы

данных (AR6H)

соединяется с суммой AR6

и связанного стартового адреса буфера

(BSA67).

AR6H:(BSA67 + AR6) = XAR6 + BSA67

Когда запускается

TMS320C54x код в совместимом режиме (C54CM =

1), убедитесь, что регистры стартового

адреса буфера содержат 0.

2.6.4

Регистры

длины кольцевого буфера (BK03, BK47, BKC)

Три 16 - разрядных

регистра длины кольцевого буфера

(смотрите рисунок 2-7) определяют число

слов (до 65535) в кольцевом буфере. Каждый

регистр длины буфера связан с конкретным

указателем или указателями (Смотрите

Таблицу 2-6).

Рисунок

2-7. Регистры длины кольцевого буфера

15-0

BK03

BK47

BKC

Таблица

2-6. Регистры длины кольцевого буфера

и указатели

Регистр

Указатель

Главная

страница данных ...

BK03

AR0,

AR1, AR2, или

AR3

AR0H

для

AR0 или

AR1 AR2H для

AR2 или

AR3

BK47

AR4,

AR5, AR6, или

AR7

AR4H

для

AR4 или

AR5 AR6H для

AR6 или

AR7

BKC

CDP

CDPH

В TMS320C54x-совместимом

режиме (C54CM = 1) BK03 применяется для всех

вспомогательных регистров, а BK47 не

используется.

Регистры,

используемые для пространства адресных

данных и пространства I/O

(ввода/вывода)

Регистры,

используемые для пространства адресных

данных и пространства I/O

(ввода/вывода)

2-17

Регистры

ЦП

2.6.5

Регистр

страницы данных (XDP / DP)

ЦП

содержит в карте памяти регистр страницы

данных DP

и связанный регистр расширения DPH:

15-0

DP

15-7

6-0

Зарезервирован

DPH

ЦП способен соединить

два для формирования расширенного DP,

который обозначается XDP (смотрите

рисунок 2-8 и Таблицу 2-7). Старшая часть

(DPH) применяется для определения 7 -

разрядной главной страницы данных для

доступа к пространству данных. Младшая

часть определяет 16 - разрядное смещение

(локальная страница данных), который

объединяется с главной страницей данных

для получения адреса в 23 бита.

Рисунок

2-8. Расширенный регистр страницы данных

и его части

22-16

15-0

XDP

DPH

DP

Таблица

2-7. Расширенный регистр страницы данных

и его части

Регистр

Название

Доступность

XDP

Расширенный

регистр страницы данных

Доступен

только через выделенные инструкции .

XDP

не является регистром,

отображенным

в карте памяти.

DP

Регистр

страницы данных

Доступен через

выделенные инструкции и как регистр,

отображенный в карте памяти.

DPH

Старшая

часть расширенного регистра страницы

данных

Доступен через

выделенные инструкции и как регистр,

отображенный в карте памяти.

В DP режиме прямой адресации XDP определяет

адрес в 23 бита, а в k16 режиме абсолютной

адресации DPH объединяется с 16 - разрядным

непосредственным значением для

формирования адреса в 23 бита.

Регистры,

используемые для пространства адресных

данных и пространства I/O

Регистры,

используемые для пространства адресных

данных и пространства I/O

2-18

2.6.6

Регистр

страницы периферийных данных (PDP)

Для PDP режима прямой адресации 9 -

разрядный регистр страницы периферийных

данных (PDP) выбирает страницу в 128 слов

внутри 64K-словесного пространства I/O

(ввода/вывода).

Как показано на рисунке 2-9, PDP обладает

9 - битовым полем внутри ячейки 16 -

разрядного регистра. Биты 15-9 данной

ячейки игнорируются ЦП.

Рисунок

2-9. Регистр страницы периферийных

данных

15-9

8-0

Зарезервировано

PDP

2.6.7

Указатели

стека (XSP / SP, XSSP / SSP)

ЦП содержит в карте

памяти указатель стека данных (SP),

системный указатель стека (SSP) и связанный

регистр расширения (SPH):

15-0

SP

15-0

SSP

15-7

6-0

Зарезервировано

SPH

Смотрите рисунок 2-10 и Таблицу 2-8. При

доступе к стеку данных ЦП объединяет

SPH с SP для формирования расширенного

SP, который обозначается XSP. XSP обладает

адресом значения, продвинутого в стек

данных последним. SPH содержит 7 - разрядную

главную страницу данных памяти. SP

указывает на конкретное слово в данной

странице.

Аналогично, при доступе к системному

стеку ЦП соединяет SPH с SSP для формирования

XSSP. XSSP содержит адрес значения,

продвинутого в системный стек последним.

Регистры,

используемые для пространства адресных

данных и пространства I/O

(ввода/вывода)

Регистры,

используемые для пространства адресных

данных и пространства I/O

(ввода/вывода)

2-19

Регистры

ЦП

Рисунок

2-10. Расширенные указатели стека

22-16

15-0

XSP

SPH

SP

XSSP

SPH

SSP

Таблица

2-8. Регистры указателя стека

Регистр

Название

Доступность

XSP

Расширенный

указатель стека данных

Доступен

только через выделенные инструкции.

XSP

не является регистром, отображенным в

карте памяти.

SP

Указатель

стека данных

Доступен через

выделенные инструкции и как регистр,

отображенный в карте памяти.

XSSP

Расширенный

системный указатель стека

Доступен

только через выделенные инструкции.

XSSP

не является регистром, отображенным в

карте памяти.

SSP

Системный

указатель стека

Доступен

через выделенные инструкции и как

регистр, отображенный в карте памяти.

SPH

Старшая

часть XSP и XSSP

Доступен

через выделенные инструкции и как

регистр, отображенный в карте памяти.

Замечание:

SPH

зависит от записи в XSP и в XSSP. Регистры,

используемые для пространства адресных

данных и пространства I/O

Регистры,

используемые для пространства адресных

данных и пространства I/O

Регистры,

используемые для пространства адресных

данных и пространства I/O

(ввода/вывода)

2-20

XSP применяется в SP

режиме прямой адресации. Следующие

инструкции используют и/или модифицируют

SP и SSP:

Типы

инструкций

Описание

Программные

прерывания, захваты, сбросы, условные

и безусловные вызовы

Эти

инструкции проталкивают данные в стек

данных и системный стек. SP и SSP

декрементируют до проталкивания каждой

пары значений данных.

Проталкивание

в стек

Эта инструкция

проталкивает данные в стек данных. SP

декрементирует до проталкивания данных.

Условный и

безусловный возврат, возврат из

прерывания

Данные инструкции

выталкивают данные из стека данных и

системного стека. SP и SSP инкрементируют

после выталкивания каждой пары значений

данных.

Выталкивание

из стека

Эта инструкция

выталкивает данные только из стека

данных. SP инкрементирует после

выталкивания данных.

Регистры

хода программ (PC, RETA, CFCT)

2-21

Регистры

ЦП

2.7

Регистры

хода программ (PC, RETA, CFCT)

Таблица 2-9 описывает

три регистра, которые применяются ЦП

для поддержания правильного хода

программ.

Таблица

2-9. Регистры хода программ

Регистр

Описание

PC

Счетчик

команд. Данный 24 - разрядный регистр

содержит адрес от 1 до 6 байт кода

декодируемого в блоке I.

Когда ЦП производит прерывание или

запрос, текущее значение PC

(адрес возврата) запоминается, а затем

PC

загружается с новым адресом. Когда ЦП

возвращается из обработчика прерываний

или вызванной подпрограммы, адрес

возврата восстанавливается в PC.

RETA

Регистр

адреса возврата. Если выбранная

конфигурация стека (см. стр. 4-4) использует

процесс с быстрым возвратом, RETA

временно удерживает место под адрес

возврата, пока подпрограмма выполняется.

RETA

вместе с CFCT

позволяет эффективное исполнение

множества уровней подпрограмм. Есть

возможность считывания из RETA

и CFTC,

и записи в них.

CFCT

Регистр

контекста управляемого потока. ЦП ведет

запись циклов повторения (контекст

циклов). Если выбранная конфигурация

стека (см. стр. 4-4) применяет процесс с

быстрым возвратом, CFTC

временно удерживает место под 8 -

разрядный контекст циклов, пока

подпрограмма выполняется. CFTC

вместе с RETA

позволяют эффективное исполнение

множества уровней подпрограмм. Существует

возможность считывания из RETA

и CFTC,

и записи в них.

2.7.1

Биты

контекста, хранящиеся в CFCT

ЦП

обладает внутренними битами для хранения

контекста циклов – статуса (активного

или неактивного) циклов повторения в

подпрограмме. Когда ЦП следует за

прерыванием или за вызовом, контекст

циклов хранится в CFTC.

Когда ЦП возвращается из прерывания

или вызванной подпрограммы, контекст

циклов восстанавливается из CFTC.

Биты контекста циклов имеют следующую

форму в 8 - разрядной CFTC.

2-22

Биты

Описание

7

Этот

бит отражает активность цикла одиночного

повторения.

0

Неактивен 1 Активен

6

Отражает

активность цикла условного одиночного

повторения.

0

Неактивен 1 Активен

5-4

Зарезервированы

3-0

Данный код в 4 бита

отражает статус двух возможных уровней

циклов с блочным повторением, внешнего

(уровень 0) и внутреннего (уровень 1). В

зависимости от типа выбранной инструкции

блочного повторения, активный цикл

может быть локальным (весь его код

многократно исполняется из буфера

инструкции) или внешним (код многократно

выбирается и передается через буфер к

ЦП).

Код

блочного повторения

Цикл

уровня 0 ...

Цикл

уровня 1 ...

0

2

3

7

8

9

Другое:

Зарезервировано

Неактивен

Активен, внешний Активен, локальный

Активен, внешний Активен, внешний

Активен, локальный -

Неактивен

Неактивен Неактивен Активен,

внешний Активен, локальный Активен,

локальный -

Регистры

хода программ (PC, RETA, CFCT)

Регистры

хода программ (PC, RETA, CFCT)

Регистры

для управления прерываниями

2-23

Регистры

ЦП

2.8

Регистры

для управления прерываниями

Данная секция описывает

следующие регистры:

Регистры

Функция

Смотрите

...

IVPD

Указывает

на DSP вектора прерывания (IV0-IV15 и IV24-IV31)

Страница

2-23

IVPH

Указывает

на таблицу векторов прерываний

(IV16-IV23)

Страница

2-23

IFR0,

IFR1

Показывает,

какое маскируемое прерывание было

запрошено

Страница

2-25

IER0,

IER1

Разрешает

или запрещает маскируемые прерывания

Страница

2-28

DBIER0,

DBIER1

Конфигурирует

выбор маскируемых прерываний как

прерываний критичных по времени

Страница

2-30

2.8.1

Указатели

вектора прерываний (IVPD, IVPH)

Два

16 - разрядных указателя вектора прерывания

(смотрите рисунок 2-11) указывают на

вектора прерываний в пространстве

программ. DSP

указатель вектора прерывания (IVPD)

указывает на страницу программ в 256

байт, которая содержит DSP

вектора прерывания (IV0-IV15

и IV24-IV31).

Данные вектора могут быть распределены

в памяти, которая размещена только в

DSP.

Хост

указатель вектора прерывания (IVPH)

указывает на страницу программ в 256

байт, которая содержит хост вектора

прерываний (IV16-IV23).

Эти вектора могут быть распределены в

памяти, разделяемой DSP

и хост процессором таким образом, что

хост - процессор может определять

связанные обработчики прерываний.

Если IVPD и IVPH имеют одно и то же значение,

все вектора прерываний будут в одной

странице программ в 256 байт. Аппаратный

сброс DSP загружает оба IVPs с FFFFh. IVPs не

зависит от инструкции программного

сброса.

Рисунок

2-11. Указатели векторов прерываний

15-0

IVPD

IVPH

2-24

Перед

модификацией IVPs убедитесь, что:

Маскируемые

прерывания глобально отключены (INTM =

1). Это предотвратит возникновение

маскируемого прерывания перед тем, как

IVPs

модифицированы на указание к новым

векторам.

Каждое

аппаратное немаскируемое прерывание

имеет вектор и обработчик прерывания

для старого и нового значений IVPD.

Это предотвратит выборку недопустимого

кода инструкции, если аппаратное

немаскируемое прерывание произойдет

в течение процесса модификации IVPD.

Таблица 2-10 показывает, как адреса

векторов формируются для различных

векторов прерываний. ЦП объединяет 16

- разрядный указатель вектора прерывания

с номером вектора, закодированного в

пяти битах (например, 00001 для IV1 и 10000 для

IV16) и сдвинутого влево на 3 бита.

Таблица

2-10.

Векторы

и структура векторных адресов

Векторные

адреса

Векторы

Прерывания

Биты

23-8

Биты

7-3

Биты

2-0

IV0

Сброс

IVPD

00000

000

IV1

Немаскируемое

аппаратное прерывание, NMI_

IVPD

00001

000

IV2-IV15

Маскируемые

прерывания

IVPD

00010

по

01111

000

IV16-IV23

Маскируемые

прерывания

IVPH

10000

по

10111

000

IV24

Прерывание

ошибки шины (маск.), BERRINT

IVPD

11000

000

IV25

Прерывание

регистрации данных (маскир.), DLOGINT

IVPD

11001

000

IV26

Прерывание

работы системы в реальном времени

(маск.), RTOSINT

IVPD

11010

000

IV27-IV31

Прерывания

универсальных программ INT27-INT31

IVPD

11011

по

11111

000

Регистры

для управления прерываниями

Регистры

для управления прерываниями

2-25

Регистры

ЦП

2.8.2

Регистры

флага прерывания (IFR0, IFR1)

16

- разрядные регистры флага прерывания

IFR1

и IFR0

содержат биты флага для всех маскируемых

прерываний. Когда запрос маскируемого

прерывания достигает ЦП, соответствующий

флаг устанавливается в 1 в одном из IFR.

Это означает, что прерывание задерживается

или ожидает подтверждения от ЦП. Рисунок

2-12 отражает картину C55x

IFR.

Для того, чтобы посмотреть, какое

прерывание отображено в этих битах,

обратитесь к справочной документации

вашего C55x

DSP.

Существует возможность как чтения из

IFR для определения задерживаемых

прерываний, так и записи в IFR для очищения

данных прерываний. Для очищения запроса

прерывания (и установки бита IFR в 0),

запишите 1 в соответствующий IFR бит.

Например:

;

Очистка флагов IF14 и IF2:

MOV

#0100000000000100b, mmap(@IFR0)

Все задерживаемые прерывания могут

быть очищены записью текущего содержимого

IFR назад в IFR. Подтверждение аппаратного

запроса прерывания также очищает

соответствующий бит IFR. Сброс устройства

очищает все биты IFR.

Рисунок

2-12. Регистры флага прерывания

15-11

10

9

8

IFR1

Зарезервировано

RTOSINTF

DLOGINTF

BERRINTF

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

7

6

5

4

3

2

1

0

IF23

IF22

IF21

IF20

IF19

IF18

IF17

IF16

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

15

14

13

12

11

10

9

8

IFR0

IF15

IF14

IF13

IF12

IF11

IF10

IF9

IF8

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

7

6

5

4

3

2

1-0

IF7

IF6

IF5

IF4

IF3

IF2

Зарезервировано

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

R/W1C

- 0

Условные

обозначения:

R

Доступ чтения

W1C

Запись

1 в данный бит заставит ЦП установить

этот бит в 0.

-

X

X

– это значение после сброса DSP.

Зарезервировано

Запись

в данное битовое поле не имеет никакого

эффекта, и биты в этом поле всегда имеют

значение 0 в течение операции чтения.

Регистры

для управления прерываниями

Регистры

для управления прерываниями

Регистры

для управления прерываниями

2-26

2.8.2.1

Бит RTOSINTF в IFR1

Бит

Имя

Описание

Доступность

Значение

сброса

10

RTOSINTF

Бит

флага прерыв. для прерыв. операционной

системы рельного времени, RTOSINT

Запись/чтение

0

При чтении бита RTOSINTF

поступайте следующим образом:

RTOSINTF

Описание

0

RTOSINT

не задерживается.

1

RTOSINT

задерживается.

Для установки данного

бита флага в 0 (и очистки соответствующего

запроса прерывания) запишите 1 в бит.

2.8.2.2

Бит DLOGINTF в IFR1

Бит

Имя

Описание

Доступность

Значение

сброса

9

DLOGINTF

Бит

флага прерыв. для прерыв. регистрации

данных, DLOGINT

Чтение/запись

0

При

чтении бита DLOGINTF

поступайте следующим образом:

DLOGINTF

Описание

0

DLOGINT

не задерживается.

1

DLOGINT

задерживается.

Для установки данного

бита флага в 0 (и очистки соответствующего

запроса прерывания) запишите 1 в бит.

2.8.2.3

Бит

BERRINTF в

IFR1

Бит

Имя

Описание

Доступность

Значение

сброса

8

BERRINTF

Бит

флага прерыв. для прерыв. ошибки шины,

BERRINT

Чтение/запись

0

При

чтении бита DLOGINTF

поступайте следующим образом:

BERRINTF

Описание

0

BERRINT

не задерживается.

1

BERRINT

задерживается.

Для установки данного

бита флага в 0 (и очистки соответствующего

запроса прерывания) запишите 1 в бит.

Регистры

для управления прерываниями

2-27

Регистры

ЦП

2.8.2.4

Биты IF16-IF23 в IFR1

Бит

Имя

Описание

Доступность

Значение

сброса

0

IF16

Бит

16 флага прерывания

Чтение/Запись

0

1

IF17

Бит

17 флага прерывания

Чтение/Запись

0

2

IF18

Бит

18 флага прерывания

Чтение/Запись

0

3

IF19

Бит

19 флага прерывания

Чтение/Запись

0

4

IF20

Бит

20 флага прерывания

Чтение/Запись

0

5

IF21

Бит

21 флага прерывания

Чтение/Запись

0

6

IF22

Бит

22 флага прерывания

Чтение/Запись

0

7

IF23

Бит

23 флага прерывания

Чтение/Запись

0

При чтении данных бит

поступайте следующим образом (x – это

номер с 16 по 23):

IFx

Описание

0

Прерывание,

связанное с вектором x

прерывания, не задерживается.

1

Прерывание,

связанное с вектором x

прерывания, задерживается.

Для установки данного

бита флага в 0 (и очистки соответствующего

запроса прерывания) запишите 1 в бит.

2.8.2.5

Биты

IF2-IF15 в

IFR0

Бит

Имя

Описание

Доступность

Значение

сброса

2

IF2

Бит

2 флага прерывания

Чтение/Запись

0

3

IF3

Бит

3 флага прерывания

Чтение/Запись

0

4

IF4

Бит

4 флага прерывания

Чтение/Запись

0

5

IF5

Бит

5 флага прерывания

Чтение/Запись

0

6

IF6

Бит

6 флага прерывания

Чтение/Запись

0

7

IF7

Бит

7 флага прерывания

Чтение/Запись

0

8

IF8

Бит

8 флага прерывания

Чтение/Запись

0

9

IF9

Бит

9 флага прерывания

Чтение/Запись

0

10

IF10

Бит

10 флага прерывания

Чтение/Запись

0

11

IF11

Бит

11 флага прерывания

Чтение/Запись

0

12

IF12

Бит

12 флага прерывания

Чтение/Запись

0

13

IF13

Бит

13 флага прерывания

Чтение/Запись

0

14

IF14

Бит

14 флага прерывания

Чтение/Запись

0

15

IF15

Бит

15 флага прерывания

Чтение/Запись

0

При чтении данных бит

поступайте следующим образом (x – это

номер с 2 по 15):

IFx

Описание

0

Прерывание,

связанное с вектором x

прерывания, не задерживается.

1

Прерывание,

связанное с вектором x

прерывания, задерживается.

Для установки данного

бита флага в 0 (и очистки соответствующего

запроса прерывания) запишите 1 в бит.

2-28

2.8.3

Регистры

разрешения прерываний (IER0, IER1)

Для разрешения

маскируемого прерывания установите

соответствующий бит в IER0 или IER1 в 1. Для

запрета маскируемого прерывания

установите соответствующий бит в 0. При

сбросе все биты IER сбрасываются в 0,

запрещая все маскируемые прерывания.

Рисунок 2-13 отражает картину C55x IER. Чтобы

посмотреть какое прерывание связано

с данными битами, обратитесь к технической

документации C55x DSP.

Замечание:

IER1 и IER0 не зависят от инструкции

программного сброса или аппаратного

сброса DSP. Инициализируйте данные

регистры до глобального разрешения

маскируемых прерываний (INTM = 0).

Рисунок

2-13. Регистры разрешения прерываний

15-11

10

9

8

IER1

Зарезервировано

RTOSINTE

DLOGINTE

BERRINTE

R/W

- NA

R/W

- NA

R/W

- NA

7

6

5

4

3

2

1

0

IE23

IE22

IE21

IE20

IE19

IE18

IE17

IE16

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

15

14

13

12

11

10

9

8

IER0

IE15

IE14

IE13

IE12

IE11

IE10

IE9

IE8

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

7

6

5

4

3

2

1-0

IE7

IE6

IE5

IE4

IE3

IE2

Зарезервировано

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

Условные

обозначения:

R

Доступ чтения

W

Доступ

записи

-

NA

Данный

бит не зависит от сброса DSP.

Зарезервировано

Запись

в данное битовое поле не имеет эффекта,

и биты в этом поле всегда обладают

значением 0 в течение операции чтения.

Регистры

для управления прерываниями

Регистры

для управления прерываниями

Регистры

для управления прерываниями

2-29

Регистры

ЦП

2.8.3.1

Бит RTOSINTE в IER1

Бит

Имя

Описание

Доступность

Значение

сброса

10

RTOSINTE

Бит

разреш. для прерыв. операц. систем реал.

времени, RTOSINT

Чтение/запись

Не

зависит от сброса

Бит RTOSINTE разрешает

или запрещает RTOSINT:

RTOSINTE

Описание

0

RTOSINT

запрещен

1

RTOSINT

разрешен

2.8.3.2

Бит DLOGINTE в IER1

Бит

Имя

Описание

Доступность

Значение

сброса

9

DLOGINTE

Бит

разреш. для прерыв. регистр. данных,

DLOGINT

Чтение/запись

Не

зависит от сброса

Бит DLOGINTE разрешает

или запрещает DLOGINT:

DLOGINTE

Описание

0

DLOGINT

запрещен

1

DLOGINT

разрешен

2.8.3.3

Бит BERRINTE в IER1

Бит

Имя

Описание

Доступность

Значение

сброса

8

BERRINTE

Бит

разреш. для прерыв. ошибки шины, BERRINT

Чтение/запись

Не

зависит от сброса

Бит

BERRINTE разрешает или запрещает BERRINT:

BERRINTE

Описание

0

BERRINT

запрещен

1

BERRINT

разрешен

2.8.3.4

Биты IE16-IE23 в IER1

Бит

Имя

Описание

Доступность

Значение

сброса

0

IE16

Бит

16 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

1

IE17

Бит

17 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

2

IE18

Бит

18 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

3

IE19

Бит

19 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

4

IE20

Бит

20 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

5

IE21

Бит

21 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

6

IE22

Бит

22 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

7

IE23

Бит

23 разреш. прерыв.

Запись/чтение

Не

зависит от сброса

Функции данных битов

могут быть подытожены так, как следует

далее, где x - это число с 16 по 23:

IEx

Описание

0

Прерывание,

связанное с вектором x прерывания,

запрещено.

1

Прерывание,

связанное с вектором x прерывания,

разрешено.

Регистры

для управления прерываниями

2-30

2.8.3.5

Биты IE2-IE15 в IER0

Бит

Имя

Описание

Доступность

Значение

сброса

2

IE2

Бит

2 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

3

IE3

Бит

3 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

4

IE4

Бит

4 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

5

IE5

Бит

5 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

6

IE6

Бит

6 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

7

IE7

Бит

7 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

8

IE8

Бит

8 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

9

IE9

Бит

9 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

10

IE10

Бит

10 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

11

IE11

Бит

11 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

12

IE12

Бит

12 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

13

IE13

Бит

13 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

14

IE14

Бит

14 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

15

IE15

Бит

15 разреш. прерыв.

Чтение/запись

Не

зависит от сброса

Функции данных битов

могут быть подытожены так, как следует

далее, где x - это число с 2 по 15:

IEx

Описание

0

Прерывание,

связанное с вектором x прерывания,

запрещено.

1

Прерывание,

связанное с вектором x прерывания,

разрешено.

2.8.4

Отладочные

регистры разрешения прерывания (DBIER0,

DBIER1)

16 - разрядные регистры разрешения

прерывания DBIER1 и DBIER0 используются

только тогда, когда ЦП приостанавливается

в режиме эмуляции реального времени

отладчика. Если ЦП работает в режиме

реального времени, то применяется

стандартный процесс обработки прерываний,

а DBIERs игнорируется.

Маскируемое прерывание разрешено в

DBIER как прерывание критичное по времени.

Когда ЦП останавливается в режиме

реального времени, обрабатываются

только прерывания критичные по времени,

которые также разрешены в регистре

разрешения прерывания (IER1 или IER0).

Считывайте DBIERs для определения прерываний

критичных по времени. Запись в DBIERs

разрешает или запрещает прерывания

критичные по времени. Для разрешения

прерывания установите соответствующий

бит. Для запрещения прерывания очистите

соответствующий бит. Рисунок 2-14 отражает

картину C55x DBIERs. Для просмотра того,

какие прерывания относятся к данным

битам, обратитесь к технической

документации C55x DSP.

Замечание:

DBIER1

и DBIER0 не зависят от инструкции программного

сброса и аппаратного сброса DSP.

Инициализируйте данные регистры до

использования режима эмуляции реального

времени.

2-31

Регистры

ЦП

Рисунок

2-14. Отладочные регистры разрешения

прерывания

15-11

10

9

8

DBIER1

Зарезервировано

RTOSINTD

DLOGINTD

BERRINTD

R/W

- NA

R/W

- NA

R/W

- NA

7

6

5

4

3

2

1

0

DBIE23

DBIE22

DBIE21

DBIE20

DBIE19

DBIE18

DBIE17

DBIE16

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

15

14

13

12

11

10

9

8

DBIER0

DBIE15

DBIE14

DBIE13

DBIE12

DBIE11

DBIE10

DBIE9

DBIE8

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

7

6

5

4

3

2

1-0

DBIE7

DBIE6

DBIE5

DBIE4

DBIE3

DBIE2

Зарезервировано

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

R/W

- NA

Условные

обозначения:

R

Доступ чтения

W

Доступ

записи

-

NA

Этот

бит не зависит от сброса DSP

Зарезервировано

Запись

в данное битовое поле не имеет эффекта,

и биты в этом поле всегда обладают

значением 0 в течение операции чтения.

2.8.4.1

Бит

RTOSINTD в

DBIER1

Бит

Имя

Описание

Доступность

Значение

сброса

10

RTOSINTD

Бит

разреш. отладки для прерыв. операц.

систем реального времени, RTOSINT

Чтение/запись

Не

зависит от сброса

Бит RTOSINTD разрешает

или запрещает RTOSINT, как прерывание

критичное по времени:

RTOSINTD

Описание

0

RTOSINT

запрещено.

1

RTOSINT

разрешено. Конфигурируется, как

прерывание критичное по времени.

Регистры

для управления прерываниями

Регистры

для управления прерываниями

Регистры

для управления прерываниями

2-32

2.8.4.2

Бит

DLOGINTD в

DBIER1

Бит

Имя

Описание

Доступность

Значение

сброса

9

DLOGINTD

Бит

разреш. отладки для прерыв. регистр.

данных, DLOGINT

Чтение/запись

Не

зависит от сброса

Бит DLOGINTD разрешает

или запрещает DLOGINT как прерывание

критичное по времени:

DLOGINTD

Описание

0

DLOGINT

запрещено.

1

DLOGINT

разрешено. Конфигурируется как прерывание

критичное по времени. .

2.8.4.3

Бит

BERRINTD в

DBIER1

Бит

Имя

Описание

Доступность

Значение

сброса

8

BERRINTD

Бит

разреш. отладки для прерыв. ошибки шины,

BERRINT

Чтение/запись

Не

зависит от сброса

Бит BERRINTD разрешает

или запрещает BERRINT как прерывание

критичное по времени:

BERRINTD

Описание

0

BERRINT

запрещено.

1

BERRINT

разрешено. Конфигурируется как прерывание

критичное по времени.

2.8.4.4

Биты DBIE16-DBIE23 в

DBIER1

Бит

Имя

Описание

Доступность

Значение

сброса

0

DBIE16

Бит

16 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

1

DBIE17

Бит

17 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

2

DBIE18

Бит

18 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

3

DBIE19

Бит

19 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

4

DBIE20

Бит 20 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

5

DBIE21

Бит 21 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

6

DBIE22

Бит 22 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

7

DBIE23

Бит 23 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

Функции данных битов

могут быть подытожены так, как следует

далее, где x это число с 16 по 23:

DBIEx

Описание

0

Прерывание,

связанное с вектором x прерывания,,

запрещено.

1

Прерывание,

связанное с вектором x прерывания,

разрешено. Прерывание конфигурируется

как критичное по времени.

Регистры

для управления прерываниями

2-33

Регистры

ЦП

2.8.4.5

Биты DBIE2-DBIE15 в

DBIER0

Бит

Имя

Описание

Доступность

Значение

сброса

2

DBIE2

Бит 2 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

3

DBIE3

Бит 3 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

4

DBIE4

Бит 4 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

5

DBIE5

Бит 5 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

6

DBIE6

Бит 6 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

7

DBIE7

Бит 7 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

8

DBIE8

Бит 8 разрешения

прерывания отладки

Чтение/запись

Не

зависит от сброса

9

DBIE9

Бит

9 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

10

DBIE10

Бит

10 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

11

DBIE11

Бит

11 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

12

DBIE12

Бит

12 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

13

DBIE13

Бит

13 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

14

DBIE14

Бит

14 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

15

DBIE15

Бит

15 разрешения прерывания отладки

Чтение/запись

Не

зависит от сброса

Функции данных битов

могут быть подытожены так, как следует

далее, где x - это число с 2 по 15:

DBIEx

Описание

0

Прерывание,

связанное с вектором x прерывания,

запрещено.

1

Прерывание,

связанное с вектором x прерывания,

разрешено. Прерывание

конфигурируется как критичное по

времени.

Регистры

для управления циклами повторения

2-34

2.9

Регистры

для управления циклами повторения

Данная секция описывает регистры,

которые контролируют выполнение циклов

повторения. Регистры одиночного

повторения применяются для повторения

одной инструкции. Регистры блочного

повторения используются для повторения

одного или более блоков инструкций.

2.9.1

Регистры

одиночного повторения (RPTC, CSR)

Инструкции

одиночного повторения позволяют

повторять инструкцию, реализуемую за

один цикл (или две инструкции, реализуемых

за один цикл, которые исполняются

параллельно). Число повторений N

загружается в счетчик одиночного

повторения (RPTC)

до первого выполнения. После первого

исполнения инструкция выполняется еще

N

раз; следовательно, полное число

исполнений равно N+1

раз.

В

некоторых синтаксисах безусловных

инструкций одиночного повторения вы

можете использовать регистр одиночного

повторения (CSR)

для определения числа N.

Значение из CSR

копируется в RPTC

до первого выполнения инструкции или

пары инструкций.

Как показано на рисунке 2-15, RPTC и CSR имеют

по 16 бит, позволяющих до 65536 последовательных

исполнений инструкции (первое выполнение

плюс 65535 повторений).

Рисунок

2-15. Регистры одиночного повторения

15-0

RPTC

CSR

2.9.2

Регистры

блочного повторения (BRC0-1, BRS1, RSA0-1, REA0-1)

Инструкции

блочного повторения позволяют формировать

циклы, которые повторяют блоки инструкций.

Вы можете иметь один цикл блочного

повторения вложенным в другом, создав

внутренний (уровень 1) цикл и внешний

цикл (уровень 0). Таблица 2-11 описывает

регистры C55x,

связанные с циклами уровня 0 и 1. Как

представлено в следующих параграфах,

применение этих регистров зависит от

бита совместимого режима C54x

(C54CM),

который объясняется на странице 2-42.

Если C54CM = 0: C55x “родной”

режим ...

ЦП

ведет запись активных циклов повторения

(смотрите описание для CFTC

в секции 2.7 на странице 2-21). Когда ЦП

декодирует инструкции блочного

повторения, сначала он определяет, не

исполняется ли уже цикл. Если ЦП определит

активный цикл уровня 0, то он применит

регистры цикла уровня 1, иначе, он

использует регистры цикла уровня 0.

2-35

Регистры

ЦП

Если C54CM = 1:

C54x-совместимый режим ...

Инструкции

блочного повторения активируют только

регистры цикла уровня 0. Регистры цикла

уровня 0 не используются. Вложенные

операции блочного повторения могут

быть реализованы на C54x

DSP,

применив сохранение/восстановление

контекста и активный флаг блочного

повторения (BRAF).

Инструкции блочного повторения

устанавливают BRAF.

BRAF

очищается к концу операции блочного

повторения, когда BRC0

содержит 0. За более подробной информацией

о BRAF

обращайтесь к странице 2-41.

Таблица

2-11.

Описание

регистров блочного повторения

Регистры

цикла уровня 0

Регистры

цикла уровня 1 (нельзя при C54CM = 1)

Регистр

Описание

Регистр

Описание

BRC0

Счетчик 0 блочного

повторения. Этот 16 - разрядный регистр

содержит число повторений блока

инструкций после начального исполнения.

BRC1

Счетчик

1 блочного повторения. Этот 16 - разрядный

регистр содержит число повторений

блока инструкций после начального

исполнения.

RSA0

Регистр 0 стартовых

адресов блочного повторения. Данный

24 - разрядный регистр обладает адресом

первой инструкции в блоке инструкций.

RSA1

Регистр

1 стартовых адресов блочного повторения.

Данный 24 - разрядный регистр обладает

адресом первой инструкции в блоке

инструкций.

REA0

Регистр 0 конечных

адресов блочного повторения. Этот 24 -

разрядный регистр содержит адрес

последней инструкции в блоке инструкций.

REA1

Регистр

0 конечных адресов блочного повторения.

Этот 24 - разрядный регистр содержит

адрес последней инструкции в блоке

инструкций

BRS1

Регистр

сохранения BRC1.

Всякий раз когда BRC1

загружается, BRS1

загружается с тем же значением. Содержимое

BRS1

не изменяемо в течение выполнения цикла

уровня 1. Каждый раз при запуске цикла

уровня 1, BRC1

реинициализируется из BRS1.

Эта особенность дает возможность

инициализации BRC1

вне цикла уровня 0, уменьшая время,

необходимое для каждого повторения.

Замечание:

Значения

24 - разрядных регистров хранятся в двух

последовательных 16 - разрядных ячейках.

Биты 23-16 находятся в младшем адресе

(восемь старших бит в данной ячейке

игнорируются ЦП). Биты 15-0 располагаются

в старшем адресе. Например, RSA0(23-16)

доступен по адресу 00 003Ch

и RSA0(15-0)

доступен по адресу 00 003Dh.

Регистры

для управления циклами повторения

Регистры

для управления циклами повторения