TMS320C55x

DSP ЦП

Руководство

по применению

Предварительный

проект документа

Данный

документ содержит текущую предварительную

информацию о дате издания, не подлежащую

изменениям без соответствующего

уведомления.

Литературный

код: SPRU371D Май 2001

ВАЖНЫЕ

ЗАМЕЧАНИЯ

Компанией

Texas

Instruments

(TI)

и ее дочерними предприятиями

зарезервированы права на внесение

изменений в их изделия, прекращение

производства продукта или осуществления

услуги без предупреждения. TI

советует своим клиентам получить

последнюю релевантную информацию для

проверки перед отдачей распоряжений

и приказов. Все продукты являются

продаваемым товаром на основе свода

законов, включающих положение о гарантии,

о нарушении патента и ограничении

ответственности.

TI

гарантирует производительность

выпускаемых полупроводниковых продуктов

согласно приложенным спецификациям

на момент продажи в соответствии с

гарантийным стандартом TI.

Тестирование и другие техники контроля

качества применены TI

для обеспечения гарантии. Специфическоеное

тестирование всех параметров каждого

устройства производилось не всегда,

за исключением заказанных государством.

Клиенты

несут ответственность за применение

компонентов TI.

Для минимизации риска,

связанного с частным применением,

покупатель должен поставить адекватную

цель и обеспечить рабочие меры

предосторожности.

TI

не несет ответственности за содействие

в применении или за планы клиента

относительно изделий фирмы. TI

не гарантирует, что любая лицензия,

выданная на правах патента, авторских

прав или других прав интеллектуальной

собственности TI,

покрывает или связана с любым объединением,

машиной или процессом, в котором продукты

или услуги такого типа должны применяться

или уже используются. Публикация

информации, посвященной любой третьей

партии продукции или услуг, не означает

одобрения компанией TI.

Репродукция

информации, хранящейся в книгах данных

или в проспектах изделий, допустима

только, если она произведена без внесения

изменений и сопровождена всеми

необходимыми гарантиями, условиями,

ограничениями и замечаниями. Отображение

или репродукция данной информации с

изменениями отменяет все гарантии,

предоставляемые для продуктов или

услуг TI,

это нечестная и обманчивая практика

деловых отношений, за что TI

не несет ответственности.

Перепродажа

продуктов или услуг TI

на условиях (утверждениях), отличающихся

от параметров, установленных TI

для продуктов и услуг, отменяет все

гарантии, это нечестная и обманчивая

практика деловых отношений, за что TI

не несет ответственности.

Также

смотрите: Стандартные сроки и условия

продажи полупроводниковых продуктов.

www.ti.com/sc/docs/stdterms.htm

Почтовый

адрес:

Texas

Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright

2001, Texas Instruments Incorporated

Предисловие

Прочти

это первым

О

руководстве

Настоящее руководство описывает

семейство ЦП TMS320C55x сигнальных процессоров

с фиксированной точкой (DSP): архитектуру,

регистры и функционирование.

Принятые

обозначения

Данный документ

использует следующие обозначения.

Номер устройства TMS320C55x , как правило,

будет обозначаться как C55x.

Если

подчеркивание добавлено к имени сигнала

(например, RESET_),

то сигнал имеет низкий активный уровень.

Листинги,

примеры программ и интерактивное

изображение показываются в специальной

гарнитуре шрифта.

В

большинстве случаев шестнадцатиричные

числа указываются с суффиксом h.

Например, следующее число в шестнадцатиричной

системе счисления равно 40:

40h

Аналогично,

бинарные числа обычно показывают с

суффиксом b.

Например, число в десятичной системе

равное 4 в бинарной форме:

0100b

Биты

и сигналы иногда обозначаются следующим

образом:

Запись

Описание

Пример

Регистр(n-m)

n

бит регистра m

AC0(15-0)

отображает 16 младших битов регистра

AC0.

Шина[n:m]

n

сигналов шины m

A[21:1] отображает

21 сигнал через 1 внешнюю шину адреса.

iii

iii

iv

Следующие термины используются для

обозначения объемов данных:

Термин

Описание

Пример

LSB

Младший

бит

В

AC0(15-0), бит 0 - LSB.

MSB

Старший

бит

В

AC0(15-0), бит 15 - MSB.

LSByte

Младший

байт

В

AC0(15-0), биты 7-0 - LSByte.

MSByte

Старший

байт

В

AC0(15-0), биты 15-8 - MSByte.

LSW

Младшее

слово

В

AC0(31-0), биты 15-0 - LSW.

MSW

Старшее

слово

В

AC0(31-0), биты 31-16 - MSW.

Документация

от Texas Instruments

Следующие

книги описывают устройства TMS320C55x и

инструментальные средства поддержки.

Для приобретения копии данных документов

позвоните в Литературный Центр Texas

Instruments

(800) 477-8924. При заказе, пожалуйста, выберите

книгу по заголовку и укажите литературный

код.

TMS320C55x

Технический обзор (литературный

код SPRU393). Данный обзор является введением

для TMS320C55x процессоров цифровых сигналов

(DSP), последнего поколения DSP с фиксированной

точкой на TMS320C5000 DSP платформе. Как и

предыдущие поколения, данный процессор

оптимизирован для высокой производительности

и малого энергопотребления. Книга

описывает архитектуру ЦП, оптимизацию

энергопотребления и встроенные

возможности эмуляции.

TMS320C55x

DSP Справочное руководство по периферии

(литературный

код

SPRU317)

описывает периферию, интерфейсы и

аппаратуру, которая доступна на

TMS320C55x (C55x) DSPs. Здесь также описывается,

как можно использовать программное

обеспечение (энергосберегающие

конфигурации) для включения или

отключения индивидуальных частей DSP

для управления энергопотреблением.

TMS320C55x

DSP Набор алгебраических

инструкций

(литературный код SPRU375) описывает

индивидуально алгебраические инструкции

TMS320C55x DSP. Также содержит сводую таблицу

инструкций, список кодов операций и

перекрестные ссылки к набору мнемонических

инструкций.

TMS320C55x

DSP Набор мнемонических инструкций

(литературный код SPRU374) описывает

индивидуально мнемонические инструкции

TMS320C55x DSP. Также содержит сводую таблицу

инструкций, список кодов операций и

перекрестные ссылки к набору алгебраических

инструкций.

Документация

от Texas Instruments

Документация

от Texas Instruments

v

Прочти

это первым

TMS320C55x

Оптимизация компилятора С

(литературный код SPRU281) описывает

компилятор С TMS320C55x. Данный компилятор

C соответствует стандарту ANSI исходного

кода C и производит исходный код языка

ассемблера для устройств TMS320C55x.

TMS320C55x

Инструментальные средства языка

ассемблер

(литературный код

SPRU280)

описывает средства языка ассемблера,

директивы ассемблера, макросы, обычные

форматы объектных файлов и директивы

символьной отладки для устройств

TMS320C55x.

TMS320C55x

Руководство программиста

(литературный код SPRU376) описывает пути

оптимизации C и кода ассемблера для

TMS320C55x DSP и объясняет, как написать код,

использующий специальные возможности

и инструкции DSP.

Торговые

марки

TMS320C54x,

C54x, TMS320C55x и C55x являются торговыми марками

Texas

Instruments. Торговые

марки

Торговые

марки

vii

Оглавление

1

Архитектура ЦП

1-1

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

1.1

Обзор архитектуры ЦП

1-2

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1

Внутренние шины адреса

и данных

1-3

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

1.1.2

Блок интерфейса памяти

(M Блок)

1-4

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

1.1.3

Блок буфера инструкций

(I Блок)

1-4

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

1.1.4

Блок операций с адресами

команд (P Блок)

1-4

. . . . .

. . . . . . . . . . . . . . . . . . . . .

1.1.5

Блок операций с адресами

данных (A Блок)

1-4

. . . . . . . .

. . . . . . . . . . . . . . . . .

1.1.6

Вычислительный блок

(D Блок)

1-4

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

1.2

Блок буфера инструкций

(I Блок)

1-5

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.1

Буфер инструкций

1-5

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

1.2.2

Декодер инструкций

1-6

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3

Блок операций с адресами

команд (P Блок)

1-7

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.1

Генерация адресов

программ и логика управления программ

1-7

. . . . . . . . . .

1.3.2

Регистры P-Блока

1-8

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

1.4

Блок операций с адресами

данных (A Блок)

1-9

. . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

1.4.1

Блок генерации адресных

данных (DAGEN)

1-10

.

. . . . . . . . . . . . . . . . . . . . . . .

1.4.2

Арифметическое

логическое устройство A-Блока (A-Блок

ALU)

1-10

.

. . . . . . .

1.4.3

Регистры A-Блока

1-10

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

1.5

Вычислительный блок

(D Блок)

1-11

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

1.5.1

Сдвигатель

1-12

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

1.5.2

Арифметическое

логическое устройство D-Блока (D-Блок

ALU)

1-12

.

. . . . . .

1.5.3

Два блока умножителя

с накоплением (MAC)

1-12

.

. . . . . . . . . . . . . . . . . . . . .

1.5.4

Регистры D-Блока

1-13

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6

Шины адреса и шины

данных

1-14

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

1.7

Конвейер инструкций

1-17

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.7.1

Фазы

1-17

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . .

1.7.2

Охранные меры

1-20

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

Регистры ЦП

2-1

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . .

2.1

Алфавитный список

регистров

2-2

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

2.2

Регистры, отображенные

в карте памяти

2-4

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3

Аккумуляторы (AC0-AC3)

2-9

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4

Регистры перехода

(TRN0, TRN1)

2-10

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

2.5

Буферные регистры

(T0-T3)

2-11

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

Оглавление

viii

2.6

Регистры,

используемые для пространств адресных

данных и I/O

(вв./выв.)

2-12

.

. . .

2.6.1

Вспомогательные

регистры (XAR0-XAR7 / AR0-AR7)

2-12

. . . . . . . . . . .

. . . . . .

2.6.2

Коэффициент указателя

данных (XCDP / CDP)

2-14

. . . . . . . . . . .

. . . . . . . . . . .

2.6.3

Регистры стартового

адреса кольцевого буфера (BSA01, BSA23,

BSA45, BSA67, BSAC)

2-15

. . . . . . . . . . . . . . . . . . .

. . . . . . . .

2.6.4

Регистры длины

кольцевого буфера (BK03, BK47, BKC)

2-16

. . . . . . . . . . . .

. .

2.6.5

Регистр

страницы данных (XDP / DP)

2-17

. . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

2.6.6

Регистр страницы

данных периферии (PDP)

2-18

. . . . . . . . . . . .

. . . . . . . . . . .

2.6.7

Указатели стека (XSP /

SP, XSSP / SSP)

2-18

.

. . . . . . . . . . . . . . . . . . . . . . . . . .

2.7

Регистры хода программ

(PC, RETA, CFCT)

2-21

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

2.7.1

Контекстные биты,

хранящиеся в CFCT

2-21

.

. . . . . . . . . . . . . . . . . . . . . . . . . .

2.8

Регистры для управления

прерываниями

2-23

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

2.8.1

Указатели векторов

прерываний (IVPD, IVPH)

2-23

.

. . . . . . . . . . . . . . . . . . . . .

2.8.2

Регистры флагов

прерываний (IFR0, IFR1)

2-25

. . . . . . . . . . . .

. . . . . . . . . . . .

2.8.3

Регистры разрешения

прерываний (IER0, IER1)

2-28

. . . . . . . . . . .

. . . . . . . . .

2.8.4

Регистры разрешения

прерываний отладки (DBIER0, DBIER1)

2-30

. . . . . . . .

2.9

Регистры управления

циклов повторения

2-34

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

2.9.1

Регистры одиночного

повторения (RPTC, CSR)

2-34

.

. . . . . . . . . . . . . . . . . . . .

2.9.2

Регистры блочного

повторения (BRC0-1, BRS1, RSA0-1, REA0-1)

2-34

. . . . . .

2.10

Регистры состояния

(ST0_55-ST3_55)

2-36

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . .

2.10.1

ST0_55 Бит

2-38

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.10.2

ST1_55 Бит

2-40

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . .

2.10.3

ST2_55 Бит

2-48

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.10.4

ST3_55 Бит

2-52

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

3

Память

и пространство I/O

3-1

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1

Карта памяти

3-2

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

3.2

Пространство программ

3-3

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

3.2.1

Байтовые адреса (24

бита)

3-3

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . .

3.2.2

Организация инструкций

в пространстве программ

3-3

. . . . . . . . . . .

. . . . . . . .

3.2.3

Выравнивание выборок

из пространства программ

3-4

. . . . . . . . . . .

. . . . . . . .

3.3

Пространство данных

3-5

. . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . .

3.3.1

Словесные адреса (23

бита)

3-5

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

3.3.2

Типы данных

3-5

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3

Организация данных в

пространстве данных

3-7

. . . . . . . . .

. . . . . . . . . . . . . . . .

3.4

Пространство

ввода/вывода (I/O)

3-8

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . .

3.5

Загрузчик операционной

системы

3-9

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . .

4

Функционирование

стека

4-1

. . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . .

4.1

Стек данных и стек

системы

4-2

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . .

4.2

Конфигурации стека

4-4

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3

Быстрый возврат в

сравнении с медленным возвратом

4-5

.

. . . . . . . . . . . . . . . . . . . . .

4.4

Автоматическое

переключение контекста

4-8

. . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1

Переключение контекста

с быстрым возвратом для запросов

4-8

.

. . . . . . . . .

4.4.2

Переключение контекста

с быстрым возвратом для прерываний

4-9

.

. . . . . .

4.4.3

Переключение контекста

с медленным возвратом для запросов

4-9

.

. . . . . . .

4.4.4

Переключение контекста

с медленным возвратом для прерываний

4-10

.

. . . .

Оглавление

ix

Оглавление

5

Прерывания и операции

сброса

5-1

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

5.1

Введение к прерываниям

5-2

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2

Векторы прерываний и

приоритеты

5-4

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . .

5.3

Маскируемые прерывания

5-8

. . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1

Биты и регистры,

разрешающие маскируемые прерывания

5-8

. . . . . . . . . . . .

5.3.2

Стандартный ход

операций для маскируемых прерываний

5-9

. . . . . . . .

. . . .

5.3.3

Ход операций для

прерываний критичных по времени

5-11

.

. . . . . . . . . . . . . .

5.4

Немаскируемые прерывания

5-13

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.1

Стандартный ход

операций для немаскируемых прерываний

5-14

.

. . . . . . . .

5.5

DSP Аппаратный сброс

5-16

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6

Программный сброс

5-21

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . .

6

Режимы адресации

6-1

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

6.1

Введение к режимам

адресации

6-2

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . .

6.2

Режимы абсолютной

адресации

6-3

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.1

k16 Режим абсолютной

адресации

6-3

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

6.2.2

k23 Режим абсолютной

адресации

6-4

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

6.2.3

I/O Режим абсолютной

адресации

6-5

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

6.3

Режимы прямой адресации

6-6

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.1

DP Режим прямой адресации

6-7

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

6.3.2

SP Режим прямой адресации

6-9

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. .

6.3.3

Регистр-бит Режим

прямой адресации

6-10

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

6.3.4

PDP Режим прямой адресации

6-10

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4

Режимы косвенной

адресации

6-12

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

6.4.1

AR Режим косвенной

адресации

6-13

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4.2

Двойной AR Режим

косвенной адресации

6-22

. . . . . . . . . . . .

. . . . . . . . . . . . . .

6.4.3

CDP Режим косвенной

адресации

6-24

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

6.4.4

Коэффициентный режим

косвенной адресации

6-27

. . . . . . . . .

. . . . . . . . . . . .

6.5

Адресация памяти

данных (АПД)

6-30

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5.1

АПД с режимом абсолютной

адресации

6-30

. . . . . . . . . . . . . . . . . . .

. . . . . . . .

6.5.2

АПД с режимом прямой

адресации

6-31

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

6.5.3

АПД с режимом косвенной

адресации

6-32

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6

Адресация

регистров, отображенных в карте памяти

(MMR)

6-52

.

. . . . . . . . . . . . . . . . .

6.6.1

Адресация MMR с k16 и k23

режимами абсолютной адресации

6-52

. . . . . . .

6.6.2

Адресация MMR с DP режимом

прямой адресации

6-53

. . . . . . . . . . . . . . . . . .

6.6.3

Адресация MMR с режимами

косвенной адресации

6-55

. . . . . . . . . . . . . . . . .

6.7

Ограничения на доступ

к регистрам, отображенными в карте

памяти

6-72

. . . . . .

. . .

6.8

Адресация битов

регистров (АБР)

6-73

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

6.8.1

АБР с режимом прямой

адресации регистр-бит

6-73

.

. . . . . . . . . . . . . . . . . . .

6.8.2

АБР с режимами косвенной

адресации

6-73

. . . . . . . . . . . . . . . . . . .

. . . . . . . . .

6.9

Адресация

пространства I/O

6-86

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . .

6.9.1

Адресация

пространства I/O

с I/O

режимом абсолютной адресации

6-86

. . . .

6.9.2

Адресация

пространства I/O

с PDP режимом прямой адресации

6-87

. . . . . .

6.9.3

Адресация

пространства I/O

с режимами косвенной адресации

6-87

. . . . . . .

6.10

Ограничения на доступ

к пространству I/O

6-96

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

6.11

Кольцевая адресация

6-97

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

6.11.1

Конфигурирование

AR0-AR7 и CDP для кольцевой адресации

6-98

. . . . . . . .

6.11.2

Реализация кольцевого

буфера

6-98

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

6.11.3

TMS320C54x совместимость

6-99

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

x

Рисунки

1-1

Схема ЦП

1-2

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

1-2

Схема блока буфера

инструкций (I Блок)

1-5

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

1-3

Схема блока операций

с адресами команд (P Блок)

1-7

.

. . . . . . . . . . . . . . . . . . . . . . . . . .

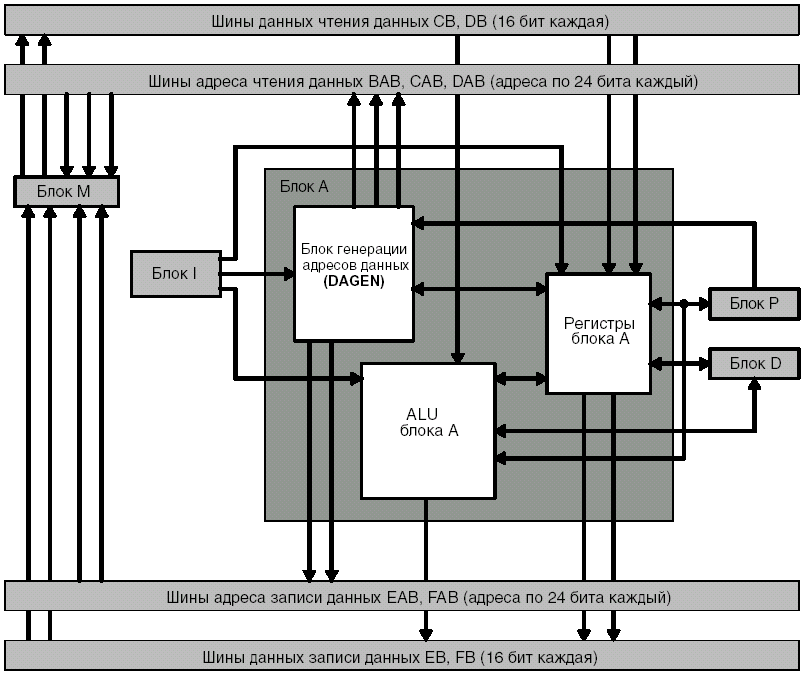

1-4

Схема блока операций

с адресами данных (A Блок)

1-9

. . . . . . . . .

. . . . . . . . . . . . . . . . . .

1-5

Схема вычислительного

блока (D Блок)

1-11

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

1-6

Первый сегмент конвейера

(Выборка)

1-17

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

1-7

Второй сегмент конвейера

(Выполнение)

1-18

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1

Аккумуляторы

2-9

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . .

2-2

Регистры перехода

2-10

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

2-3

Буферные регистры

2-11

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-4

Расширенные

вспомогательные регистры и их части

2-13

.

. . . . . . . . . . . . . . . . . . . . . . . . .

2-5

Расширенный коэффициент

указателя данных и его части

2-14

. . . . . . . .

. . . . . . . . . . . .

2-6

Регистры стартового

адреса кольцевого буфера

2-15

.

. . . . . . . . . . . . . . . . . . . . . . . . . . .

2-7

Регистры длины

кольцевого буфера

2-16

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

2-8

Расширенный регистр

страницы данных и его части

2-17

.

. . . . . . . . . . . . . . . . . . . . . . . .

2-9

Регистр страницы

данных периферии

2-18

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

2-10

Расширенные указатели

стека

2-19

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . .

2-11

Указатели векторов

прерываний

2-23

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-12

Регистры флагов

прерываний

2-25

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . .

2-13

Регистры, разрешающие

прерывания

2-28

. . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-14

Регистры, разрешающие

прерывания отладки

2-31

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-15

Регистры с одиночным

повторением

2-34

. . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . .

2-16

Регистры состояния

2-37

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

3-1

Карта памяти

3-2

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . .

4-1

Расширенные указатели

стека

4-2

. . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-2

Возврат адреса и

циклирование контекста при процессе

с медленным возвратом

4-6

. .

4-3

Использование

RETA

и CFTC

в процессе с быстрым возвратом

4-7

. . . . .

. . . . . . . . . . . .

5-1

Стандартная

последовательность операций для

маскируемых прерываний

5-9

.

. . . . .

5-2

Ход операций для

прерываний критичных по времени

5-11

. . . . . .

. . . . . . . . . . . . . . . . . . .

5-3

Стандартная

последовательность операций для

немаскируемых прерываний

5-14

.

. . .

6-1

k16 Режим абсолютной

адресации

6-4

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

6-2

k23 Режим абсолютной

адресации

6-5

. . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

6-3

I/O Режим абсолютной

адресации

6-5

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

6-4

DP Режим прямой адресации

6-7

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

6-5

SP Режим прямой адресации

6-9

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-6

Регистр-бит Режим

прямой адресации

6-10

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

Рисунки

xi

Оглавление

6-7

PDP Режим прямой адресации

6-11

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

6-8

Доступ к пространству

данных с AR режимом косвенной адресации

6-14

.

. . . . . . . . . . .

6-9

Доступ к битам регистра

с AR режимом косвенной адресации

6-14

. . . . . . . . . . . . . . . . .

6-10

Доступ к пространству

I/O с AR режимом косвенной адресации

6-15

. . . . . . . . . . . . .

. . .

6-11

Доступ к пространству

данных с CDP режимом косвенной адресации

6-24

. . . . . . . . . . .

6-12

Доступ к битам регистра

с CDP режимом косвенной адресации

6-25

. . . . . . . . . . . . . . . .

6-13

Доступ к пространству

I/O с CDP режимом косвенной адресации

6-25

. . . . . . . . . . . . . .

xii

Таблицы

1-1

Функции шин данных и

шин адреса

1-14

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

1-2

Использование шины в

соответствии с типом доступа

1-15

.

. . . . . . . . . . . . . . . . . . . . . . .

1-3

Примеры, иллюстрирующие

исполнение действий конвейера

1-19

. . . . . .

. . . . . . . . . . . .

2-1

Алфавитный список

регистров

2-2

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . .

2-2

Регистры, отображенные

в карте памяти

2-4

. . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3

Расширенные

вспомогательные регистры и их части

2-13

. . . . . . . . . . .

. . . . . . . . . . . . . . .

2-4

Расширенный коэффициент

указателя данных и его части

2-14

. . . . . . . .

. . . . . . . . . . . .

2-5

Регистры стартового

адреса кольцевого буфера и связанные

указатели

2-15

. . . . . . . .

2-6

Регистры длины

кольцевого буфера и связанные указатели

2-16

. . . . . . . . . . . . . . . .

. . .

2-7

Расширенный регистр

страницы данных и его части

2-17

.

. . . . . . . . . . . . . . . . . . . . . . . . .

2-8

Регистры указателя

стека

2-19

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-9

Регистры хода программ

2-21

..

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . .

2-10

Вектора и формирование

адресных векторов

2-24

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

2-11

Описание регистров с

блоковым повторением

2-35

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1

Загрузка байта и

инструкции хранения байта

3-6

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

4-1

Регистры указателя

стека

4-3

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . .

4-2

Конфигурации стека

4-4

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-1

Векторы прерываний,

отсортированные в соответствии с

номером ISR

5-4

.

. . . . . . . . . .

5-2

Векторы прерываний,

отсортированные по приоритету

5-5

. .

. . . . . . . . . . . . . . . . . . . . . . .

5-3

Этапы в стандартном

ходе процесса для маскируемых прерываний

5-10

. . . . . . . . . . .

.

5-4

Этапы в ходе обработки

для прерываний, критичных по времени

5-12

. . . . . . . .

. . . . . . .

5-5

Этапы в стандартном

ходе обработки для немаскируемых

прерываний

5-15

. . . . . . . . . .

5-6

Эффект аппаратного

сброса DSP на регистры DSP

5-16

. . . . . . . . . . . . . . . . . .

. . . . . . . . .

5-7

Эффект программного

сброса на регистры DSP

5-21

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-1

Операнды режима DSP для

AR режима косвенной адресации

6-16

. . . . . . . . . . . . . .

. . .

6-2

Операнды управления

режимом для AR режима косвенной адресации

6-20

.

. . . . . . . .

6-3

Косвенные

операнды двойного AR

6-23

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-4

CDP косвенные операнды

6-26

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

6-5

Коэффициент

косвенных

операндов

(coefficient indirect operands)

6-29

.

. . . . . . . . . . . . . .

6-6

*abs16(#k16) Используется

для доступа к памяти данных

6-30

.

. . . . . . . . . . . . . . . . . . . .

6-7

*(#k23) Используется для

доступа к памяти данных

6-31

. . . . . . . .

. . . . . . . . . . . . . . . . . .

6-8

@Daddr Используется для

доступа к памяти данных

6-31

.

. . . . . . . . . . . . . . . . . . . . . . . .

6-9

*SP(offset) Используется

для доступа к памяти данных

6-32

. . . . . . .

. . . . . . . . . . . . . . . .

6-10

Выбор

косвенного операнда для доступа к

памяти данных

6-33

. . . . . . . . . . . . . . . . .

. . . .

6-11

*abs16(#k16)

Используется для доступа к MMR

6-53

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

6-12

*(#k23)

Используется для доступа к MMR

6-53

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Таблицы

xiii

Оглавление

6-13

@Daddr

Используется для доступа к MMR

6-54

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . .

6-14

Косвенные

операнды для доступа к MMR

6-55

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-15

@bitoffset Используется

для доступа к битам регистра

6-73

. . . . . .

. . . . . . . . . . . . . . . . .

6-16

Косвенные операнды

для доступа к битам регистра

6-74

.

. . . . . . . . . . . . . . . . . . . . . . . . .

6-17

*port(#k16) или port(#k16)

Используется для доступа к пространству

I/O

6-86

. . .

. . . . . . .

6-18

@Poffset Используется для

доступа к пространству I/O

6-87

.

. . . . . . . . . . . . . . . . . . . . . .

6-19

Косвенные операнды

для доступа к пространству I/O

6-88

. . . . . . . . .

. . . . . . . . . . . . . . . .

Архитектура

ЦП

Данная глава описывает архитектуру ЦП

устройства TMS320C55x (C55x) DSP. Она разъясняет

концептуальные детали, касающиеся

четырех функциональных блоков ЦП, и

рассказывает о шинах, несущих инструкции

и данные. Здесь также описываются

параллельные фазы конвейера инструкций

и механизм защиты конвейера (который

препятствует выпадению из установленного

порядка чтения и записи операций).

Тема

Страница

1.1

Обзор

архитектуры ЦП

1-2

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2

Блок

буфера инструкций (I Блок)

1-5

.

. . . . . . . . . . . . . . . . . . . . . .

1.3

Блок

операций с адресами команд (P Блок)

1-7

.

. . . . . . . . . . . . .

1.4

Блок

операций с адресами данных (A Блок)

1-9

.

. . .. . . . . . . . . . .

1.5

Вычислительный

блок (D Блок)

1-11

.

. . . . . . . . . . . . . . . . . . . . . . .

1.6

Шины

адреса и шины данных

1-14

.

. . . . . . . . . . . . . . . . . . . . . . . . .

1.7

Конвейер

инструкций

1-17

.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-1

1-1Глава 1

1-2

1.1

Обзор

архитектуры ЦП

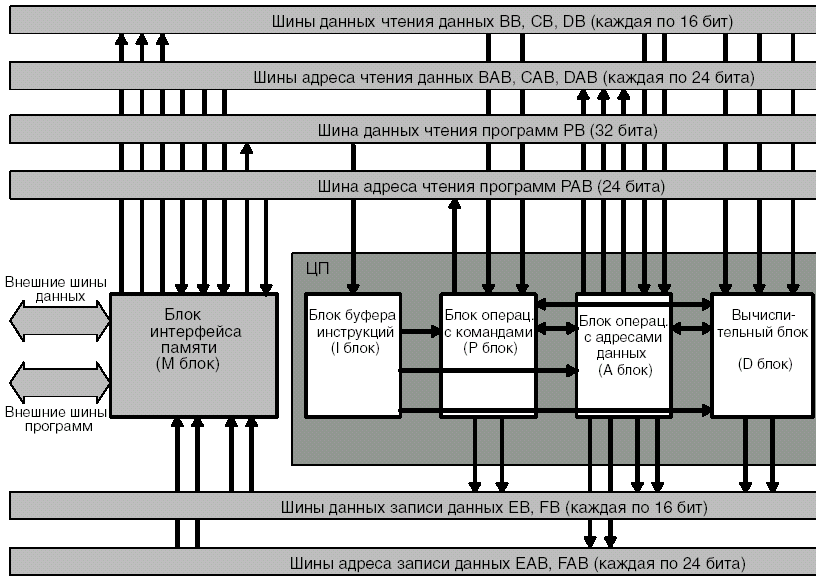

Рисунок 1-1 показывает концептуальную

блок-схему ЦП. Секции с 1.1.1 по 1.1.6 описывают

шины и блоки, представленные на рисунке.

Рисунок

1-1. Схема ЦП

Обзор

архитектуры ЦП

Обзор

архитектуры ЦП

1-3

Архитектура

ЦП

1.1.1

Внутренние

шины адреса и данных

Шины, показанные на

рисунке 1-1:

Шины

данных чтения данных (BB, CB, DB). Данные

три шины несут 16-ти разрядные данные

из пространства данных или пространства

I/O

(ввода/вывода) к функциональным блокам

ЦП.

BB переносит данные из внутренней памяти

в блок D (главным образом в двойной блок

умножителя-накопителя (MAC)). BB не соединена

с внешней памятью. Инструкции, которые

осуществляют считывание трех операндов

в одно время, используют шины BB, CB и DB.

Замечание:

BB не соединена с внешней памятью. Если

инструкция выберет операнд, используя

BB, то операнд должен быть во внутренней

памяти.

CB и DB передают данные в блок P, блок A и

в блок D. Инструкции, которые считывают

два операнда одновременно, используют

шины CB и DB. Инструкции, которые производят

одиночное считывание, применяют шину

DB.

Шины

адреса чтения данных (BAB, CAB, DAB). Эти

три шины пересылают адреса в 24 бита к

блоку интерфейса памяти, который, затем,

передает запрашиваемые значения в шину

данных чтения данных. Все адреса

пространства данных генерируются в

блоке A.

BAB несет адреса для

данных, которые пересылаются из

внутренней памяти в ЦП через BB.

CAB содержит адреса для

данных, которые передаются к ЦП

посредством CB.

DAB транспортирует

адреса для данных, которые переносятся

к ЦП либо только на DB, либо на CB и DB

одновременно.

Шина

данных чтения программ (PB). PB

переносит 32 бита (4 байта) программного

кода к блоку I,

где инструкции декодируются.

Шина

адреса чтения программ (PAB).

PAB пересылает адрес в 24 бита программного

кода, который перемещается к ЦП через

PB.

Шины

данных записи данных (EB, FB). Эти

две шины передают данные в 16 бит из

функциональных блоков ЦП к пространству

данных или пространству I/O

(ввода/вывода).

EB и FB принимают данные из блока P, блока

A и блока D.Инструкции, которые записывают

два 16 - разрядных значения в память,

одновременно используют шины EB и FB.

Инструкции, производящие одиночную

запись, применяют EB. Обзор

архитектуры ЦП

Обзор

архитектуры ЦП

Обзор

архитектуры ЦП

1-4

Шины

адреса записи данных (EAB, FAB). Данные

две шины транспортируют адреса в 24 бита

к блоку интерфейса памяти, который

затем принимает значения, поступившие

от шин данных записи данных. Все адреса

пространства данных генерируются в

блоке A.

EAB

переносит адреса для данных, которые

перемещаются в память посредством либо

только EB,

либо EB

и FB

одновременно.

FAB

передает адреса для данных, которые

пересылаются в память через FB.

1.1.2

Блок

интерфейса памяти (M блок)

Блок M служит связующим

звеном для передачи всех данных между

ЦП и пространством данных или пространством

I/O (ввода/вывода).

1.1.3

Блок

буфера инструкций (I блок)

В

течение каждого цикла ЦП блок I

принимает 4 байта программного кода в

свой буфер инструкций и далее декодирует

один из шести байтов кода, которые были

получены ранее. Затем блок I

пересылает данные в блок P,

блок A

и блок D

для исполнения инструкций. Например,

любые константы, которые были закодированы

в инструкциях (для загрузки регистров,

обеспечивающих число сдвигов, определение

битовых номеров и т.д.), извлекаются в

блоке I

и перемещаются в соответствующий блок.

1.1.4

Блок

операций с адресами команд (P блок)

Блок

P

генерирует все адреса пространства

программ и пересылает их с помощью PAB.

Он также контролирует последовательность

инструкций через такие операции, как

аппаратное зацикливание, условный

переход и исполнение по условию.

1.1.5

Блок

операций с адресами данных (A блок)

Блок

A

содержит всю необходимую логику и все

регистры для генерации адресов

пространства данных, которые переносятся

посредством BAB,

CAB

и DAB.

Он также содержит 16-ти разрядное

арифметическое логическое устройство

(ALU),

которое может осуществлять арифметические,

логические, сдвиговые операции и

операцию насыщения.

1.1.6

Вычислительный

блок (D блок)

Блок D содержит основные

вычислительные блоки ЦП:

40-битное многорегистровое циклическое

сдвиговое устройство, которое обеспечивает

сдвиг в диапазоне от –32 до 31.

40-битное

арифметическое логическое устройство

(ALU), производящее арифметические,

логические операции и операции округления

и насыщения.

Пара блоков умножителей-накопителей

(MAC), осуществляющие 17- разрядное умножение

и 40 - разрядное складывание или вычитание

в одном цикле.

1-5

Архитектура

ЦП

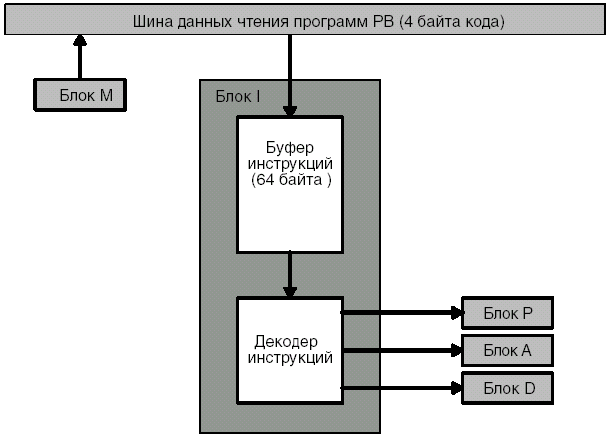

1.2

Блок

буфера инструкций (I блок)

Блок

I

принимает программный код в свой буфер

инструкций и декодирует инструкции.

Затем блок I

передает данные в блок P,

блок A

и блок D

для выполнения инструкций. Рисунок 1-2

показывает концептуальную блок-схему

блока I.

Секции 1.2.1 и 1.2.2 описывают основные

части данного блока.

Рисунок

1-2. Блок буфера инструкций (I блок)

1.2.1

Буфер

инструкций

ЦП

осуществляет 32 - разрядную выборку

единовременно из памяти программ. Шина

данных PB

переносит данные 32 бита из памяти к

буферу инструкций. Буфер может содержать

до 64-х байт недекодированных инструкций.

Когда ЦП готов декодировать инструкции,

6 байт пересылаются из буфера к декодеру

инструкций.

Блок

буфера инструкций (I блок)

Блок

буфера инструкций (I блок)

Блок

буфера инструкций (I блок)

1-6

Для облегчения работы

с конвейерной обработкой инструкций

буфер позволяет следующее:

Исполнение блока кодов, хранящегося

в буфере (инструкция с локальным

повторением).

Предварительная

выборка инструкций, пока условие для

одной из следующих инструкций тестируется:

Условный

переход

Условный

запрос

Условный возврат

1.2.2

Декодер

инструкций

В фазе декодирования

конвейера инструкций декодер инструкций

принимает 6 байт программного кода из

буфера инструкций и декодирует данные

байты. Декодер инструкций:

Определяет границы инструкций так,

чтобы он мог декодировать 8-, 16 -, 24 -, 32

-, 40 - и 48 - разрядные инструкции.

Определяет, был ли ЦП инструктирован

на выполнение двух инструкций параллельно.

Посылает

декодированные команды исполнения и

непосредственные значения к блоку

операций с адресами команд (блок P),

блоку операций с адресами данных (блок

A)

и вычислительному блоку (блок D).

Определенные

инструкции позволяют вам записывать

непосредственные значения прямо в

память или пространство I/O

(ввода/вывода) посредством выделенного

канала данных.

1-7

Архитектура

ЦП

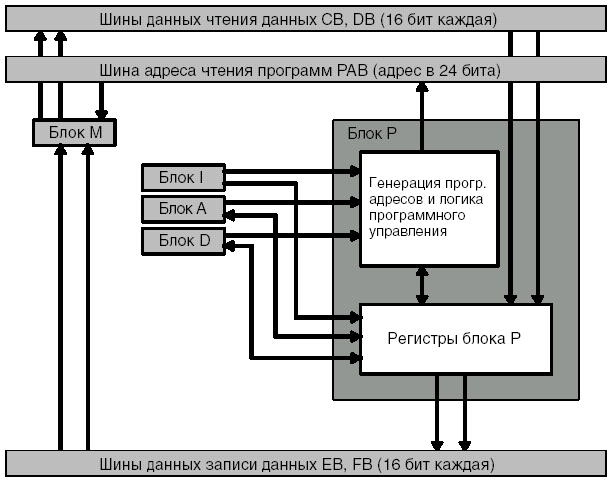

1.3

Блок

операций с адресами команд (P блок)

Блок

P

генерирует все адреса пространства

программ. Он также контролирует

последовательность инструкций. Рисунок

1-3 показывает концептуальную блок-схему

блока P.

Секции 1.3.1 и 1.3.2 описывают основные

части блока P.

Рисунок

1-3. Схема блока операций с адресами

команд (P блок)

1.3.1

Генерация

программных адресов и логика программного

управления

Логика

генерации программных адресов отвечает

за генерацию 24- разрядных адресов для

выборки из памяти программ. Обычно

генерируется последовательность

адресов. Хотя для инструкций, требующих

чтение из непоследовательных адресов,

данная логика может принять непосредственные

данные из блока I

и значения регистра из блока D.

Как только адрес сгенерирован, он

пересылается в память посредством шины

адреса PAB.

Логика

программного управления принимает

непосредственные значения из блока I

и тестирует результаты из блока A

или блока D,

и производит следующие действия:

Тестирует на достоверность условия

для инструкций условного перехода и

сообщает результат в логику генерации

программных адресов.

Запускает обработку прерываний,

когда прерывание запрошено и правильно

разрешено.

Блок

операций с адресами команд (P блок)

Блок

операций с адресами команд (P блок)

Блок

операций с адресами команд (P блок)

1-8

Контролирует повторяемость либо

отдельной инструкции (упрежденной

инструкцией с одиночным повторением),

либо блока инструкций (упрежденной

инструкцией с блочным повторением).

Можно реализовать три уровня циклов

вложением операции блочного повторения

в другую операцию того же типа, и

включением операции с одиночным

повторением в один или оба повторяемых

блока. Все операции повторения прерываемы.

Управляет

инструкциями, исполняемыми параллельно.

Параллельность в C55x

DSP

позволяет одновременное выполнение

программно-контролируемых инструкций

как инструкций обработки данных.

1.3.2

Регистры

блока P

Блок

P

содержит и использует регистры,

приведенные в следующей таблице. Доступ

к регистрам хода программ ограничен.

Счетчик PC

закрыт для записи и считывания. Доступ

к RETA

и CFCT

возможен только со следующим синтаксисом:

MOV

dbI(Lmem),

RETA

и MOV

RETA,

dbI

(Lmem).

Все остальные регистры могут быть

загружены с непосредственными значениями

(из блока I)

и могут сообщаться двунаправленно с

памятью данных, пространством I/O

(ввода/вывода), регистрами блока A

и блока D.

Регистры хода

программ

PC

Счетчик команд

RETA

Регистр

адреса возврата

CFCT

Управляющий

регистр потока контекста

Регистры блочного

повторения

BRC0,

BRC1

Счетчики блочного повторения 0

и 1

BRS1

Регистр

сохранения BRC1

RSA0,

RSA1

Регистры

стартового адреса блочного повторения

0 и 1

REA0,

REA1

Регистры

завершающего адреса блочного повторения

0 и 1

Регистры одиночного

повторения

RPTC

Счетчик с одиночным

повторением

CSR

Регистр

одиночного повторения

Регистры прерываний

IFR0,

IFR1

Регистры флага прерываний 0 и

1

IER0,

IER1

Регистры

разрешения прерываний 0 и 1

DBIER0,

DBIER1

Отладочные

регистры разрешения прерываний 0 и 1

Регистры состояния

STO_55-ST3_55

Регистры состояния 0, 1, 2 и 3

1-9

Архитектура

ЦП

1.4

Блок

операций с адресами данных (A блок)

Блок

A

содержит всю логику и регистры,

необходимые для генерации адресов

пространства данных. Он также имеет

арифметическое логическое устройство

(ALU),

которое осуществляет арифметические,

логические операции и операции сдвига,

и насыщения. Рисунок 1-4 показывает

концептуальную блок-схему блока A.

Секции с 1.4.1 по 1.4.3 описывают основные

части блока A.

Рисунок

1-4. Схема блока операций с адресами

данных (блок А)

Блок

операций с адресами данных (A блок)

Блок

операций с адресами данных (A блок)

Блок

операций с адресами данных (A блок)

1-10

1.4.1

Блок

генерации адресов данных (DAGEN)

DAGEN

генерирует все адреса для считывания

из пространства данных или записи в

него. В таком случае, он может принимать

непосредственные значения из блока I

и значения регистров из блока A.

Блок P

указывает DAGEN

использовать линейную или кольцевую

адресацию для инструкции, которая

применяет режим косвенной адресации.

1.4.2

Арифметическое

логическое устройство блока А (ALU блока

А)

Блок

А содержит 16 - разрядное ALU,

которое принимает непосредственные

значения из блока I

и сообщается двунаправленно с памятью,

пространством I/O,

регистрами блока А, регистрами блока

D

и регистрами блока P.

ALU

блока А производит следующие действия:

Сложение,

вычитание, сравнение, операции булевой

логики, знаковый сдвиг, логический

сдвиг и вычисление абсолютных величин.

Тесты, установки, очищение и дополнение

битов регистров блока А и битов памяти.

Модифицирование

и перемещение значений регистров.

Циклический

сдвиг значений регистров.

Перемещение

достоверных результатов из сдвигового

регистра к регистру блока А.

1.4.3

Регистры

блока А

Блок

А содержит и использует регистры,

представленные в следующей таблице.

Все эти регистры способны принимать

непосредственные данные из блока I

и могут принимать данные из (или

обеспечивать данными) регистров блока

P,

регистров блока D

и памяти данных. В блоке А регистры

имеют двунаправленные связи с DAGEN

и ALU

блока А.

Регистры страницы

данных

DPH,DP

Регистры страницы

данных

PDP

Регистр

страницы данных периферии

Указатели

CDPH,CDP

Регистры коэффициента

указателя данных

SPH,

SP, SSP

Регистры

указателя стека

XAR0-XAR7

Вспомогательные

регистры

Регистры кольцевого

буфера

BK03,

BK47,

BKC

Регистры длины кольцевого

буфера

BSA01,

BSA23, BSA45, BSA67, BSAC

Регистры

стартового адреса кольцевого буфера

Буферные регистры

T0-T3

Буферные регистры

0, 1, 2 и 3

1-11

Архитектура

ЦП

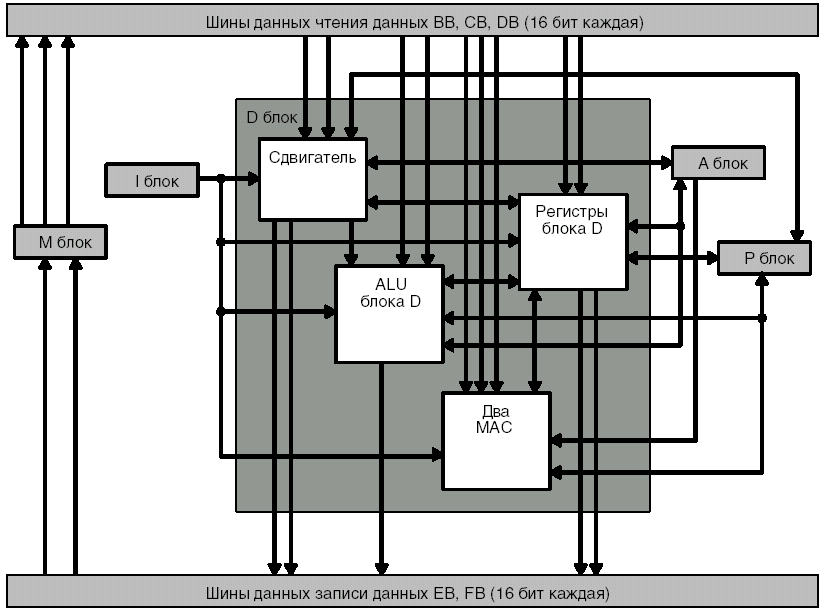

1.5

Вычислительный

блок (D блок)

Блок

D

содержит основные вычислительные блоки

ЦП. Рисунок 1-5 показывает концептуальную

блок-схему блока D.

Секции с 1.5.1 по 1.5.4 описывают главные

составляющие блока D.

Рисунок

1-5. Схема вычислительного блока (блок

D)

Вычислительный

блок (D блок)

Вычислительный

блок (D блок)