Вычислительный

блок (D блок)

1-12

Сдвигатель

блока D

принимает непосредственные значения

из блока I

и сообщается двунаправленно с памятью,

пространством I/O,

регистрами блоков А, D

и P.

К тому же, он передает сдвинутые значения

к ALU

блока D

(как вход для дальнейших вычислений) и

к ALU

блока А (как результат, хранимый в

регистре блока А). Сдвигатель осуществляет

следующие операции:

Сдвигает

значения аккумулятора в 40 бит влево на

величину до 31-го бита или вправо на

величину до 32-х бит. Количество сдвигов

может быть считано из одного из буферных

регистров (T0-T3),

или, оно может быть представлено как

константа в инструкции.

Сдвигает

значения 16 - разрядного регистра, памяти

или пространства I/O

влево на величину до 31-го бита или вправо

на величину до 32-х бит. Количество

сдвигов может быть считано из одного

из буферных регистров (T0-T3)

или может быть представлено, как

константа в инструкции.

Сдвигает 16 -

разрядные непосредственные значения

влево на величину до 15-ти бит. Число

сдвигов представляется, как константа

в инструкции.

Нормализует

значения аккумулятора

Извлекает

и расширяет битовое поле и осуществляет

подсчет битов

Циклически

сдвигает значения регистров

Округляет

и/или насыщает значения аккумулятора

до их хранения в памяти данных.

1.5.2

Арифметическое

логическое устройство блока D

(ALU блока D)

ЦП

содержит 40 - разрядное ALU

в блоке D,

которое принимает непосредственные

значения из блока I

и сообщается двунаправленно с памятью,

пространством I/O,

регистрами блоков А, D

и P.

К тому же, оно принимает результаты из

сдвигового регистра. ALU

блока D

производит следующие действия:

Сложение, вычитание, сравнение,

округление, насыщение, операции булевой

логики и вычисление абсолютных величин.

Осуществляет две арифметические

операции одновременно, когда дуальная

16 - разрядная арифметическая инструкция

выполнена.

Тестирует,

устанавливает, очищает и дополняет

биты регистра блока D.

Перемещает

значения регистров

1.5.3

Два

умножителя-накопителя (MAC)

Два

MAC поддерживают умножение и

сложение/вычитание. В одном цикле каждый

MAC

может осуществить умножение 17 бит

17 бит (дробное или целочисленное) и 40 -

разрядное сложение или вычитание с

необязательным 32-/40 - разрядным насыщением.1.5.1 Сдвигатель

Вычислительный

блок (D блок)

1-13

Архитектура

ЦП

MAC

принимает непосредственные значения

из блока I,

значения данных из памяти, пространства

I/O

и регистров блока А, и сообщается

двунаправленно с регистрами блоков D

и P.

Биты регистра состояния (в блоке P)

зависят от операций MAC.

1.5.4

Регистры

блока D

Блок

D

содержит и использует регистры,

представленные ниже в следующей таблице.

Все эти регистры способны принимать

непосредственные данные из блока I

и могут принимать из (или обеспечивать

данными) регистров блоков P,

A,

сдвигового регистра и памяти данных.

В блоке D

регистры обладают двунаправленной

связью со сдвиговым регистром, ALU

блока D

и MAC.

Аккумуляторы

AC0-AC3

Аккумуляторы 0, 1, 2 и 3

Регистры перехода

TRN0,

TRN1

Регистры перехода 0 и 1

1-14

1.6

Шины

адреса и шины данных

ЦП обеспечен одной 32 - разрядной

программной шиной (PB), пятью 16- разрядными

шинами данных (BB, CB, DB, EB, FB) и шестью 24-

разрядными шинами адреса (PAB, BAB, CAB, DAB,

EAB, FAB). Эта параллельная структура шин

позволяет 32- разрядное чтение программ,

три считывания 16 - разрядных данных и

две записи 16 - разрядных данных в одном

цикле синхронизации. Таблица 1-1 описывает

функции 12-ти шин, а Таблица 1-2 показывает,

какая шина (или шины) применяются при

определенном типе доступа.

Таблица

1-1. Функции шин данных и адресных шин

Шина

или шины

Разрядность

Функция

PAB

24

бита

Шина

адреса чтения программ (PAB)

переносит адрес в 24 бита для считывания

из пространства программ.

PB

32

бита

Шина

данных чтения программ (PB) передает 4

байта (32 бита) программного кода из

памяти программ к ЦП.

CAB,

DAB

24

бита каждая

Каждая

из этих шин адреса чтения данных

пересылает адреса в 24 бита (DAB

для чтения из пространства либо данных,

либо I/O;

CAB

перемещает второй адрес в течение

чтения двойных данных (смотрите Таблицу

1-2)).

CB,

DB

16

бит каждая

Каждая

из этих шин данных чтения данных

переносит 16- разрядное значение данных

к ЦП (DB

из пространства либо данных, либо I/O;

CB

передает второе значение в течение

чтения длинных и двойных данных (смотрите

Таблицу 1-2)).

BAB

24

бита

Эта

шина адреса чтения данных перемещает

адрес в 24 бита для коэффициента чтения.

Многие инструкции, которые используют

режим косвенной адресации, применяют

BAB

для связи коэффициентов значений данных

(и применяют BB

для переноса значений данных).

BB

16

бит

Эта

шина данных чтения данных пересылает

16 - разрядный коэффициент значения

данных из внутренней памяти к ЦП. BB

не соединена с внешней памятью. Данные,

передаваемые на BB,

адресованы через BAB.

Специфичные

инструкции используют BB, CB и DB для

обеспечения в одном цикле трех 16 -

разрядных операндов к ЦП, используя

коэффициентный режим косвенной

адресации. Операнд, выбранный через

BB,

должен быть в банке памяти, отличном

от банков, доступных через CB

и DB.

EAB,

FAB

24

бита каждая

Каждая

из этих шин адреса записи данных

пересылает адреса в 24 бита (EAB

для записи в пространство либо данных,

либо I/O;

FAB

перемещает второй адрес в течение

записи двойных данных (смотрите Таблицу

1-2)).

EB,

FB

16

бит каждая

Каждая

из этих шин данных записи данных

переносит 16 - разрядное значение данных

к ЦП (EB

в пространство либо данных, либо I/O;

FB

передает второе значение в течение

записи длинных и двойных данных (смотрите

Таблицу 1-2)).

Шины

адреса и шины данных

Шины

адреса и шины данных

1-15

Архитектура

ЦП

Замечание:

В случае записи двойных

данных в один и тот же адрес результат

неопределен.

Таблица

1-2. Применение шин при определенном

типе доступа

Тип

доступа

Шины

адреса

Шины

данных

Описание

Загр.

буфера инструк.

PAB

PB

32

- разр. чтение из простр. программ

Чтение

одиноч. данных

DAB

DB

16

- разр. чтение из простр. данных

Чтение

одиноч. MMR

DAB

DB

16 - разрядное чтение

из регистров, отображенных в карте

памяти (MMR)

Чтение

одиноч. I/O

DAB

DB

16

- разр. чтение из пространства I/O

Запись

одиноч. данных

EAB

EB

16

- разр. запись в простр. данных

Запись

одиноч. MMR

EAB

EB

16 - разрядная запись

в регистры, отображенные в карте памяти

(MMR)

Запись

одиноч. I/O

EAB

EB

16

- разр. запись в пространство I/O

Чтение

длинных данных

DAB

CB,

DB

32

- разр. чтение из простр. данных

Запись

длинных данных

EAB

EB,

FB

32

- разр. запись в простр. данных

Чтение

двойных данных

CAB,

DAB

CB,

DB

Два

одновременных 16 - разр. считывания из

простр. данных. Чтение первого операнда

осуществл. через DAB

и DB.

Второго – через CAB

и СB.

Замечание:

ЦП может считывать из MMR

только через шины D.

Запись

двойных данных

EAB,

FAB

EB,

FB

Две

одновременных 16 - разр. записи в простр.

данных. Запись первого операнда

осуществл. через FAB

и FB.

Второго – через EAB

и EB.

Замечание:

ЦП может записывать в MMR

только через шины E.

Чтение одиноч.

данных || записи одиноч. данных

DAB,

EAB

DB,

EB

Следующие

две операции производятся параллельно:

Чтение

одиночных данных: 16 - разр. чтение из

простр. данных (через DAB

и DB).

Запись

одиноч. данных: 16 - разр. запись в простр.

данных (через EAB

и EB).

Шины

адреса и шины данных

Шины

адреса и шины данных

Шины

адреса и шины данных

1-16

Таблица

1-2. Применение шин при определенном

типе доступа (продолжение)

Тип

доступа

Описание

Шины

данных

Шины

адреса

Чтение

длинных данных || записи длинных данных

DAB,

EAB

CB,

DB, EB, FB

Следующие

два действия происходят в параллель:

Чтение

длинных данных: 32- разр. чтение из простр.

данных (через DAB,

CB

и DB).

Запись

длинных данных: 32- разр. запись в простр.

данных (через EAB,

EB

и FB).

Чтение

одиноч. данных

||

чтению коэффициента данных

DAB,

BAB

DB,

BB

Следующие

две операции осуществляются параллельно:

Чтение

одиноч. данных: 16 - разр. чтение из простр.

данных (через DAB

и DB).

Чтение

коэф. данных: 16 - разр. чтение из внутренней

памяти, используя режим косвенной

адресации (через BAB

и BB).

Чтение

двойных данных || чтению коэффициента

данных

CAB,

DAB, BAB

CB,

DB, BB

Следующие

два действия производятся в параллель:

Чтение

двойных данных: Два одновременных 16 -

разр. чтения из простр. данных. Чтение

первого операнда происходит через DAB

и DB.

Второго – через CAB

и CB.

Чтение

коэф. данных: 16 - разр. чтение из внутренней

памяти, используя режим косвенной

адресации (через BAB

и BB).

Замечание:

ЦП может считывать из MMR

только через шины D.

1-17

Архитектура

ЦП

1.7

Конвейер

инструкций

C55x

ЦП использует конвейерную обработку

инструкций. Секция 1.7.1 описывает

конвейер, а секция 1.7.2 объясняет, как

ЦП препятствует конфликтам, которые

могут возникнуть в конвейере. TMS320C55x

DSP Руководство программиста

(SPRU376) содержит дополнительную информацию

о работе конвейера.

1.7.1

Фазы

конвейера

Конвейер инструкций

C55x является защищенным конвейером,

который имеет два раздельных сегмента:

Первый

сегмент относится к конвейерной выборке,

которая осуществляет выбоку 32 - разрядных

пакетов инструкций из памяти и помещает

их в буфер инструкций (IBQ),

и затем обеспечивает второй сегмент

48 - разрядными пакетами инструкций.

Выборка конвейера иллюстрирована на

рисунке 1-6.

Второй сегмент относится к конвейерному

исполнению, которое декодирует инструкции

и осуществляет доступ к данным, и

вычисления. Исполнение конвейера

показано на рисунке 1-7. Таблица 1-3

(страница 1-19) демонстрирует примеры

для понимания процессов в ключевых

фазах исполнения конвейера.

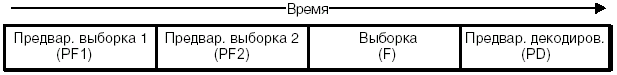

Рисунок

1-6. Первый сегмент конвейера

Time

Фазы

конвейера

Описание

PF1

Программная

выборка адресов в память

PF2

Ожидание

памяти для ответа

F

Выборка

пакета инструкций из памяти и перемещение

в IBQ.

PD

Инструкции

предварительного декодирования в IBQ

(определение конца и начала инструкций,

и параллельных инструкций)

Конвейер

инструкций

Конвейер

инструкций

1-18

Рисунок

1-7. Второй сегмент конвейера

Time

Фазы

конвейера

Описание

D

Чтение

шести байт из буфера инструкций

Декодирование

одной или пары инструкций

Отправление

инструкций к соотв. функц. блокам ЦП

Чтение

STx_55

бит, связанных с генерацией адресных

данных:

ST1_55(CPL)

ST2_55(ARnLC)

ST2_55(ARMS)

ST2_55(CDPLC)

AD

Чтение/модифиц.

регистров участв. в генер. адресных

данных

Например:

-

ARx и T0 в *ARx+(T0)

-

BK03 если AR2LC = 1

-

SP в течение выталкивания из стека и

проталкивания в него -

SSP, тот же, что и для SP, если в 32- разр.

стековом режиме

Производит

операции, используемые ALU

блока А. Например:

-

Использование инструкции AADD

-

Обмен регистрами блока А с инструкцией

SWAP - Запись констант в регистры

блока А (BKxx,

BSAxx,

BRCx, CSR и т.д.).

Декремент

ARx

для инструкций условного перехода,

которые переходят на ARx,

а не на 0.

(Исключение)

Оценка состояния инструкции XCC

(выполнение (блок AD)

атрибутов в алгебраическом синтаксисе).

AC1

Для

операций считывания из памяти посылает

адреса на соответствующей шине адреса

ЦП.

AC2

Позволяет

запоминать один цикл для ответа на

запрос чтения

R

Чтение

данных из памяти и регистры MMR-адресуемые

Чтение

регистров блока А , когда исполняется

специфическая инструкция блока D,

которая предварительно выбирает

регистры блока А в фазу R,

предпочтительнее, чем чтение их в фазе

X

Оценка

состояния инструкций условного перехода.

Не все оценки состояний производятся

в фазе R.

Исключения маркируются как “(Исключение)”

в таблице.

Конвейер

инструкций

Конвейер

инструкций

1-19

Архитектура

ЦП

Рисунок

1-7. Второй сегмент конвейера (продолжение)

Фазы

конвейера

Описание

X

Чтение/модифиц.

регистров, которые не адресованы MMR

Чтение/модифиц.

индивидуальных бит регистров

Установление

условий

(Исключение)

Оценка состояния XCCPART инструкции, пока

инструкция не согласуется с записью в

память (в данном случае условие

оценивается в фазе R).

(Исключение)

Оценка условия инструкции RPTCC.

W

Запись

данных в MMR

или в пространство I/O

(регистры периферии).

Запись данных

в память. Из перспективы ЦП операция

записи завершается в фазе конвейера.

W+

Запись данных

в память. Из перспективы памяти операция

записи завершается в фазе конвейера.

Таблица

1-3. Примеры исполнения действий конвейера

Синтаксис

Пояснения

AMOV

#k23, XARx

XARx

инициализируется с константой в фазе

AD

MOV

#k, ARx

ARx

не является MMR-адресованным. ARx

инициализируется с константой в фазе

X.

MOV

#k, mmap(ARx)

ARx

является MMR-адресованным. ARx инициализируется

с константой в фазе W.

AADD

#k, ARx

Со

специальной инструкцией ARx инициализируется

с константой в фазе AD.

MOV

#k, *ARx+

Запись

в память осуществляется в фазе W+

MOV

*ARx+, AC0

ARx

читается и обновляется в фазе AD.

AC0 загружается в фазе X.

ADD

#k, ARx

ARx

читается в начале фазы X

и модифицируется в конце фазы X.

ADD

ACy, ACx

Действия

чтения и записи ACx и Acy происходят в фазе

X.

Конвейер

инструкций

Конвейер

инструкций

Конвейер

инструкций

1-20

Таблица

1-3. Примеры выполнения действий конвейера

(продолжение)

Синтаксис

Пояснения

MOV

mmap(ARx), ACx

ARx

является MMR-адресованным так же, как и

чтение в фазе R.

ACx

модифицируется в фазе X.

MOV

ARx, ACx

ARx не является

MMR-адресованным так же, как и чтение в

фазе X . ACx модифицируется в фазе X.

BSET

CPL

Бит

CPL устанавливается в фазе X.

PUSH,

POP, RET or AADD #K8, SP

SP читается и

модифицируется в фазе AD. SSP зависим,

если выбран 32- разр. режим стека.

XCCPART

overflow(ACx) || MOV *AR1+, AC1

Условия

оцениваются в фазе X.

Замечание: AR1

прирастает независимо от верности

условия.

XCCPART

overflow(ACx) || MOV AC1, *AR1+

Условие

оценивается в фазе R.

Замечание: AR1

прирастает независимо от верности

условия.

XCC

overflow(ACx) || MOV *AR1+, AC1

Условие

оценивается в фазе AD. Замечание: AR1

прирастает только, если условие верно.

1.7.2

Защита

конвейера

Множество

инструкций выполняются одновременно

в конвейере, и различные инструкции

вносят изменения в память, пространство

I/O

и в значения регистров в течение

разнообразных фаз завершения. В

незащищенных конвейерах это может

привести к конфликтам – чтение и запись

на одном и том же месте, вышедшего из

преназначенного порядка. Конвейер C55x

обладает механизмом, который автоматически

противостоит конфликтам в конвейере.

Данный механизм добавляет неактивные

циклы между инструкциями, которые могут

привести к конфликтам.

Большинство циклов

защиты включаются на основе двух правил:

Если инструкцию предполагается

записать в ячейку, с которой еще не

считана предыдущая инструкция,

дополнительные циклы вносятся таким

образом, чтобы сначала производилось

считывание.

Если инструкцию предполагается

считать из ячейки, в которую еще не

записана предыдущая инструкция,

дополнительные циклы вносятся так,

чтобы сначала осуществлялась запись.

TMS320C55x

DSP Руководство программиста

(SPRU376) предлагает подсказки по минимизации

числа вносимых циклов, необходимых для

защиты конвейера.