- •Питання для іспиту з дисципліни

- •“Комп’ютерна схемотехніка” для спеціальності 5.05010201

- •Особливості процесу виконання команди кр580вм80.

- •Поняття про цикл процесу виконання команди в мп.

- •Алгоритм циклічного обчислювального процесу.

- •Команди звернення до підпрограми.

- •Поняття про логічні адреси при формуванні 20-розрядної адреси у 16-розрядному процесорі.

- •Перерахуємо всі 10 типів:

- •Регістр прапорців мп і 8086, призначення прапорців.

- •Команди умовних викликів підпрограми. Приклади.

- •Практична частина

Розглянуто на засіданні циклової комісії фундаментальних дисциплін Протокол № від ______2010р. Голово комісії ___________О.І.Лабаз

Питання для іспиту з дисципліни

“Комп’ютерна схемотехніка” для спеціальності 5.05010201

Особливості процесу виконання команди кр580вм80.

Виконання кожної команди виробляється мікропроцесором у суворо певної послідовності дій, що визначається кодом команди, і синхронізується сигналами Ф1 і Ф2 тактового генератора. Цикл команди - цей час виконання команди. Упродовж цього терміну: команда вибирається з пам'яті, дешифрируется код команди, формуються управляючі сигнали для виконання команди, завершується вплив управляючих сигналів. Цикл команди розбивається на машинні цикли - цей час, необхідну звернення до пам'яті або до пристроям введення - виведення. Цикл команди складається з стількох машинних циклів, скільки інтерпретацій пам'яті або до УВВ знадобиться для виконання цієї команди. Команди цього мікропроцесора можуть утримувати від 1 до 5 машинних циклів. Натомість кожен машинний цикл складається з тактів - найменший проміжок часу, необхідний виконання одного елементарного дії микропроцессоре. Такт дорівнює 1 періоду тактових імпульсів тактового генератора. Машинний цикл може полягати від 3 до 5 тактів. Перші три такту потрібні в організацію обміну з пам'яттю, а другий і третій такти - до виконання внутрішніх операцій на микропроцессоре. Відлік тактів тягнеться з позитивних фронтів імпульсної послідовності Ф1. За виконання будь-який команди спочатку зчитується перший байт команди з пам'яті. Прості команди виконуються за машинний цикл; складні команди - за 5 машинних циклів з вісімнадцятьма тактами.

Алгоритм лінійного-обчислювального процесу.

Л

Початок

інійно-обчислювальний процес передбачає послідовне виконання команд програм і має вигляд:

Кінець

При цьому програмний лічильник формує адресу наступної команди шляхом збільшення свого змісту на одиничку

Поняття про мнемокод.

Мнемокод ідентифікує команди Асемблера. Використовується скорочення англійських слів, які передають особливості передаваної команди. Наприклад:

ADD+ , a SAT-

Тригери регістра ознак, вміст який використовується в ролі умов в командах умовних викликів підпрограми.

У ролі умов в командах умовних викликів підпрограми використовується вміст чотирьох тригерів регістра ознак: тригерів Tz, Ts, Tp, Tc.

Tz – тригер 0, Tz=1, якщо результат 0.

Ts – тригер знаку встановлюється в стан , який відповідає знаковому розряду результату.

Tp – тригер парності Tp=1, якщо в результаті парна кількість 1.

Tc – тригер переносу містить переноси з старшого розряду при виконанні арифметичних операцій.

Команди цього типу при виконанні умови приводять до зміни вмісту програмного лічильника (РС) – замість адреси наступної за порядком команди в програмний лічильник записується адреса переходу або початкова адреса підпрограми, яка вказана в другому та третьому байтах команди, тобто дії описані вище; якщо вказана умова не виконується, то виконується наступна за порядком команда.

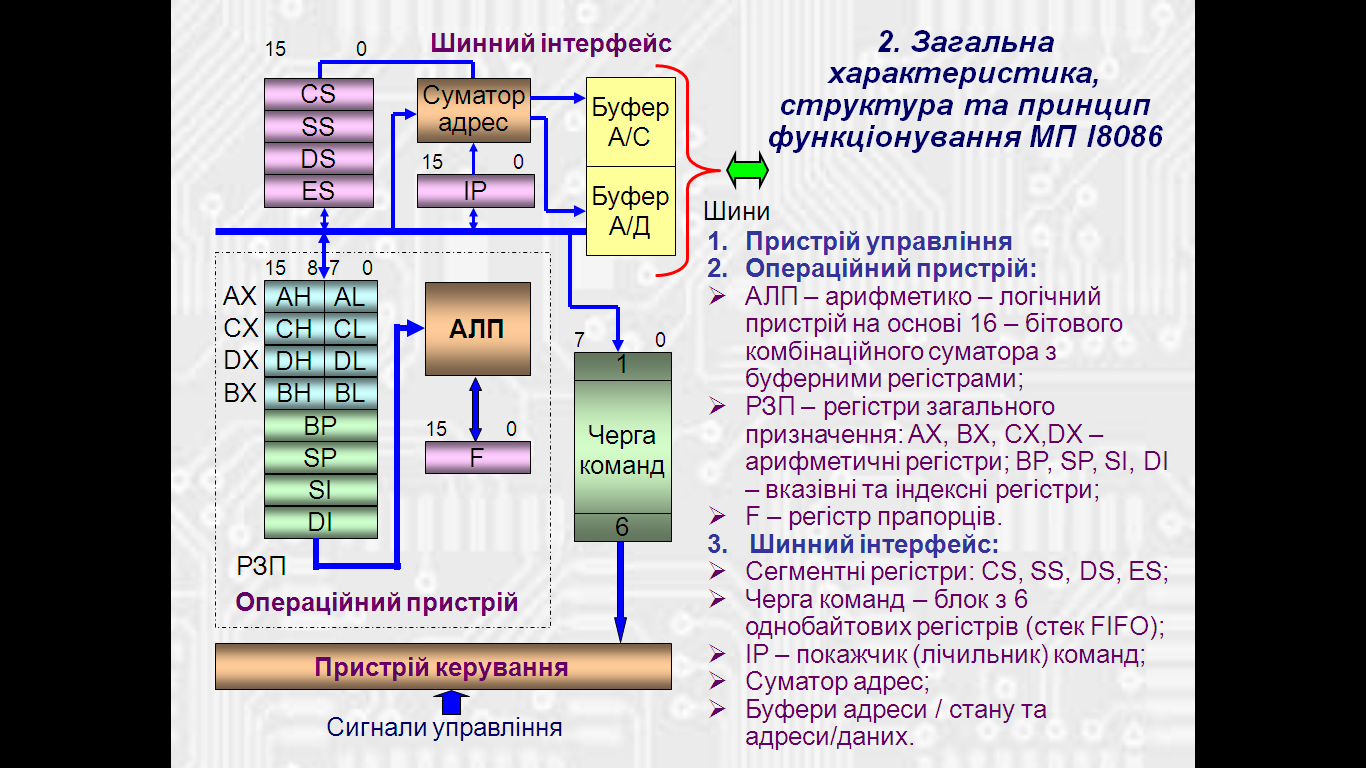

Особливості структури МП і8086.

МП і8086 – це 16-ти розрядний МП з конвеєрною архітектурою. Конвеєрний режим забезпечується паралельною роботою двох пристроїв , з яких складається мікропроцесор – операційного пристрою та шинного інтерфейсу.

Операційний пристрій виконує команду, а шинний інтерфейс взаємодіє з зовнішньою шиною: виставляє адреси, зчитує коди команд, операнди, записує результати виконання команд у пам'ять чи пристрої В/B.

Особливості сегментної організації пам’яті МП і8086.

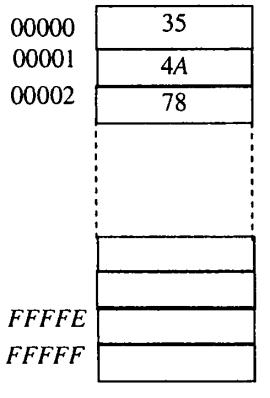

У МП i8086 застосовано сегментну організацію пам'яті, яка характеризується тим, що програмно доступною є не вся пам'ять, а лише деякі сегменти, тобто області пам'яті. Усередині сегмента використовують лінійну адресацію.

Рис. 1. Програмна модель пам'яті

Упровадження

сегментної організації можна пояснити

таким чином. Мікропроцесор i8086 являє

собою 16-розрядний процесор, тобто він

має 16-розрядну внутрішню шину, 16-розрядні

регістри і суматори. Прагнення розробників

ВІС адресувати якомога більший масив

пам'яті зумовило використання 20-розрядної

шини даних. Для порівняння: 16-розрядна

шина адреси дозволяє адресувати

=

64 кбайт; 20-розрядна -

=

64 кбайт; 20-розрядна -

=

1 Мбайт.

=

1 Мбайт.

Особливості команд пересилання даних із регістрів у регістри МП і8086.

Мнемокод команди пересилання має вигляд:

MOV dest, src

Dest – операнд призначення

Src – операнд-джерело

Якщо мова йде про пересилання з регістру в регістр то мнемокод має вигляд:

MOV reg, reg

Приклад:

Передати дані з регістру CL у регістр BL.

MOV

BL,

CL

BL CL

CL

Після виконання команди MOV вміст регістрів одного і другого буде однаковий BL=11000001 і CL=11000001.

Переслати вміст комірки памяті DS:[200DH] у регістр CX.

MOV CX, [200DH] CX DS[200DH]

Вміст 16-ти розрядної комірки памяті має пересилатися у 16-ти розрядний регістр. В команді вказана команда молодшого байта слова. А старший байт слова знаходиться в комірці з адресою на одиницю більша, ніж адреса у вказаній команді, тобто з адресою DS[200DH].

Завантажити сегментний регістр DS початковим значенням 4000H . Оскільки безпосередньо завантажити сегментний регістр значенням 4000h неможна. Необхідно ці значення записати у РЗП, а потім передати це значення у сегментний регістр

MOV BX, 4000h BX 4000h

MOV DS, BX DS BX

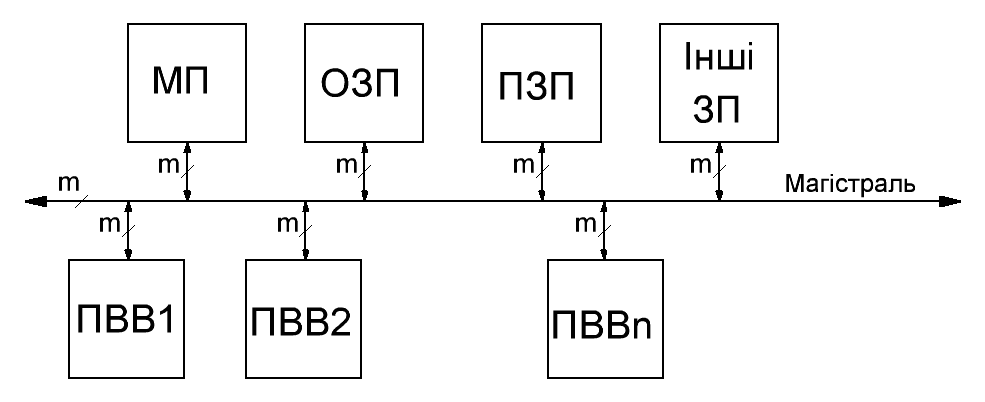

Магістральний спосіб організації введення-виведення.

Особливістю універсальних мікропроцесорів є відсутність апаратних засобів обміну даними з зовнішніми пристроями, таких як буфери для короткотривалого зберігання даних, що вводяться чи виводяться, схем ідентифікації пристроїв введення/виведення тощо. Отже, при побудові МПС треба передбачити спеціальні апаратні засобу, що будуть забезпечувати спряження мікропроцесора з зовнішніми пристроями. Сукупність апаратних засобів та програмного забезпечення, що їх обслуговує, називають інтерфейсом введення/виведення.

Переважно зовнішні пристрої працюють значно повільніше ніж МПС. Отже, при потребі, МПС може обслуговувати значну кількість зовнішніх пристроїв. Якщо зовнішні пристрої підключаються паралельно до шини введення/виведення МПС, то таку шину називають системною шиною, спільною шиною або магістраллю. . Такий спосіб організації введення/виведення отримав назву магістрального (рис.15.1).

Рис.15.1 Магістральний спосіб організації введення/виведення