- •2. Основи програмування і налагодження контролерів avr

- •2.1. Програми avr Assembler V.1.0

- •2.1.1. Відкриття асемблерних файлів

- •2.1.2. Інтегрований редактор

- •2.1.3. Написання програми

- •2.1.4. Асемблування програми

- •2.2. Вивчення пакету avr Studio

- •2.2.2. Вікно процесора

- •2.2.4. Вікно порту

- •2.2.5. Вікно 8-бітного таймера-лічильника

- •2.2.6. Регістри енергонезалежної пам’яті eeprom

- •2.2.7. Команди точок останова (Breakpoint commands)

- •2.2.8. Команди керування виконанням програми

- •2.2.10. Вибір контролера

- •2.2. Система команд та їх характеристика

- •2.2.1. Арифметичні і логічні команди

- •Команда add - Скласти без переносу

- •Команда adc - Скласти з переносом

- •Команда sub - відняти без переносу

- •Команда subi - Відняти константу

- •Команда sbc - Відняти з переносом

- •Команда sbci – Відняти константу з переносом

- •Команда and - Виконати логічне “і”

- •Команда andi - Виконати логічне “і” з константою

- •Команда or - Виконати логічне “або”

- •Команда ori - виконати логічне “або” з константою

- •Команда eor - Виконати виключаюче “або”

- •Команда com - Виконати доповнення до одиниці

- •Команда neg - Виконати доповнення до двох

- •Команда sbr - Встановити біти в регістрі

- •Команда cbr - Очистити біти в регістрі

- •Команда inc - Інкрементувати

- •Команда dec - декрементувати

- •Команда tst - Перевірити на нуль або мінус

- •Команда clr - очистити регістр

- •Команда ser - Встановити всі біти регістра

- •Операція

- •2.2.2. Команди розгалуження Команда rjmp – Відносний перехід

- •Операція:

- •Команда rcall – Відносний виклик підпрограми

- •Операція

- •Команда ret - Повернення із підпрограми

- •Операція

- •Команда reti – Повернення із переривання

- •Операція

- •Команда cpse - Порівняти і пропустити, якщо рівні

- •Команда cp - Порівняти

- •Команда cpc – Порівняти з урахуванням переносу

- •Команда cpi – Порівняти з константою

- •Команда sbrc – Пропустити, якщо біт в регістрі очищений

- •Команда sbrs – Пропустити, якщо біт в регістрі встановлений

- •Команда sbic – Пропустити, якщо біт в регістрі вводу-виводу очищений

- •Команда sbis – Пропустити, якщо біт в регістрі вводу-виводу встановлений

- •Команда brbs – Перейти, якщо біт в регістрі статусу встановлений

- •Команда brbc – Перейти, якщо біт в регістрі статусу очищений

- •Команда breq – Перейти, якщо рівно

- •Команда brne – Перейти, якщо не рівно

- •Команда brcs – Перейти, якщо прапорець переносу встановлений

- •Команда brcc – Перейти, якщо прапорець переносу очищений

- •Команда brsh – Перейти, якщо рівно або більше (без знаку)

- •Команда brlo – Перейти, якщо менше (без знаку)

- •Команда brmi – Перейти, якщо мінус

- •Команда brpl – Перейти, якщо плюс

- •Команда brge – Перейти, якщо більше або дорівнює (з урахуванням знаку)

- •Команда brlt – Перейти, якщо менше чим (зі знаком)

- •Команда brhs – Перейти, якщо прапорець половинного переносу встановлений

- •Команда brhc – Перейти, якщо прапорець половинного переносу очищений

- •Команда brts – Перейти, якщо прапорець t встановлений

- •Команда brtc – Перейти, якщо прапорець t очищений

- •Команда brvs – Перейти, якщо переповнення встановлено

- •Команда brvc – Перейти, якщо переповнення очищене

- •Команда brie – Перейти, якщо глобальне переривання дозволене

- •Команда brid – Перейти, якщо глобальне переривання заборонено

- •2.2.3. Команди пересилки Команда ld - Загрузити непрямо з созп в регістр з використанням індексу z

- •Команда st - записати непрямо з регістру в созп з використанням індексу z

- •Команда mov - копіювати регістр

- •Команда ldi - загрузити константу

- •Команда in - Загрузити дані з порту вводу-виводу в регістр

- •Команда out - Записати дані з регістра в порт вводу-виводу

- •Операція:

- •2.2.4. Команди роботи з бітами Команда sbi - Встановити біт в регістр вводу-виводу

- •Команда cbi - Очистити біт в регістрі вводу-виводу

- •Команда lsl - Логічний зсув вліво

- •Команда lsr - Логічний зсув вправо

- •Команда rol - Зсунути вліво через перенос

- •Команда ror - Зсунути вправо через перенос

- •Команда asr - Арифметичний зсув вправо

- •Команда swap - Обмін нібблів місцями

- •Команда bset - Встановити біт в регістрі статусу (sreg)

- •Команда bclr - Очистити біт в регістрі статусу (sreg)

- •Команда bst - Переписати біт із регістра в прапорець t регістра статусу

- •Команда bld - Загрузити вміст t прапорця регістра статусу (sreg) в біт регістра

- •Команда sec - Встановити прапорець переносу

- •Операція

- •Команда clc - Очистити прапорець переносу в регістрі статусу (sreg)

- •Команда sen - Встановити прапорець від’ємного значення

- •Команда cln - Очистити прапорець від’ємного значення в регістрі статусу (sreg)

- •Команда sez - Встановити прапорець нульового значення

- •Операція

- •Команда clz - Очистити прапорець нульового значення

- •Команда sei - Встановити прапорець глобального переривання

- •Операція

- •Команда cli - Очистити прапорець глобального переривання в регістрі статусу (sreg)

- •Команда ses - Встановити прапорець знаку

- •Команда cls - Очистити прапорець знаку

- •Команда sev - Встановити прапорець переповнення

- •Команда clv - Очистити прапорець переповнення

- •Команда set - Встановити прапорець t

- •Команда clt - Очистити t прапорець

- •Команда seh - Встановити прапорець половинного переносу

- •Операція

- •Команда clh - Очистити прапорець половинного переносу в регістрі статусу (sreg)

- •Команда nop - Виконати холосту команду

- •Команда sleep - Встановити режим sleep

- •Команда wdr - Збросити сторожовий таймер

- •2.2.5. Приклади написання програм

- •2.3. Програмні і апартні засоби підтримки розробок для мікроконтролерів avr

- •2.3.1. Стартові набори розроблювача

- •2.3.2. Стартовий набір stk500

- •2.3.3. Плата розширення stk501

- •2.3.4. Плата розширення stk502

- •2.3.5. Плата розширення stk503

- •2.3.6. Плата розширення stk504

- •2.3.7. Внутрісхемний програматор atavrisp

- •2.3.8. Внутрісхемні емуляторы

- •2.3.9. Внутрісхемний емулятор atjtagice mkIi (atjtagice2)

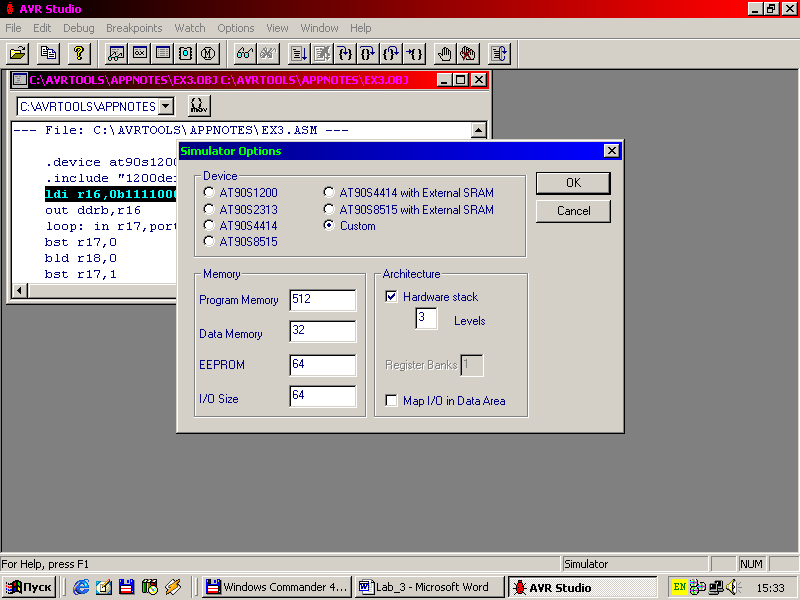

2.2.10. Вибір контролера

В AVR Studio існують симулятори всіх контролерів серії AT90S*. Для вибору контролера заходимо в меню Options >> Simulator Options (рис.2.11).

Рис.2.11

В меню Device вибираємо потрібний контролер. Якщо вибрати варіант Custom, то можна задати свої параметри контролера. В меню Program Memory задаємо об’єм програмної пам’яті, в меню Data Memory - об’єм пам’яті даних, в меню EEPROM - об’єм енергонезалежної пам’яті і в меню I/O Size - об’єм пам’яті вводу-виводу.

2.2. Система команд та їх характеристика

Усі команди AVR-контролерів можна умовно розділити на чотири групи:

арифметичні і логічні команди;

команди розгалуження;

команди пересилки;

команди роботи з бітами.

В табл.2.1. приведено вся система команд 8-розрядних AVR-контролерів.

Таблиця 2.1

Мнемоніка |

Операнди |

Описання |

Дія |

Прапорці |

Цикл |

АРИФМЕТИЧНІ І ЛОГІЧНІ КОМАНДИ |

|||||

ADD |

Rd, Rr |

Скласти два регістра |

Rd ← Rd + Rr |

Z, ,N,V,H |

1 |

ADC |

Rd, Rr |

Скласти з переносом |

Rd ← Rd + Rr + C |

Z,C,N,V,H |

1 |

SUB |

Rd, Rr |

Відняти два регістра |

Rd ← Rd - Rr |

Z,C,N,V,H |

1 |

SUBI |

Rd, K |

Відняти константу |

Rd ← Rd - K |

Z,C,N,V,H |

1 |

SBC |

Rd, Rr |

Відняти з переносом |

Rd ← Rd - Rr - C |

Z,C,N,V,H |

1 |

SBCI |

Rd, K |

Відняти константу з переносом |

Rd ← Rd – K - C |

Z,C,N,V,H |

1 |

AND |

Rd, Rr |

Логічне “І” двох регістрів |

Rd ← Rd AND Rr |

Z, N, V |

1 |

ANDI |

Rd, K |

Логічне “І” регістра з константою |

Rd ← Rd AND K |

Z, N, V |

1 |

OR |

Rd, Rr |

Логічне “АБО” двох регістрів |

Rd ← Rd OR Rr |

Z, N, V |

1 |

ORI |

Rd, K |

Логічне “АБО” регістра з константою |

Rd ← Rd OR K |

Z, N, V |

1 |

EOR |

Rd, Rr |

Виключаюче “АБО” двох регістрів |

Rd ← Rd XOR Rr |

Z, N, V |

1 |

COM |

Rd |

Доповнення до 1 (зворотній код) |

Rd ← $FF - Rd |

Z, C, N, V |

1 |

NEG |

Rd |

Доповнення до 2 (додатковий код) |

Rd ← $00 - Rd |

Z,C,N,V,H |

1 |

SBR |

Rd, K |

Установка біта(-ів) в регістрі |

Rd ← Rd OR K |

Z, N, V |

1 |

CBR |

Rd, K |

Скидання біта(-ів) в регістрі |

Rd ← Rd AND (FFh - K) |

Z, N, V |

1 |

INC |

Rd |

Збільшити на 1 |

Rd ← Rd + 1 |

Z, N, V |

1 |

DEC |

Rd |

Зменшити на 1 |

Rd ← Rd – 1 |

Z, N, V |

1 |

TST |

Rd |

Перевірити на 0 або мінус |

Rd ← Rd AND Rd |

Z, N, V |

1 |

CLR |

Rd |

Очистити регістр (всі біти обнуляються) |

Rd ← Rd XOR Rd |

Z, N, V |

1 |

SER |

Rd |

Установити регістр (всі біти установлюються в 1) |

Rd ← $FF |

Не змінює |

1 |

КОМАНДИ РОЗГАЛУДЖЕННЯ |

|||||

RJMP |

k |

Відносний перехід |

PC ← PC+k+1 |

Не змінює |

2 |

RCALL |

k |

Відносний виклик підпрограми |

PC ← PC+k+1 |

Не змінює |

3 |

RET |

|

Вихід із підпрограми |

PC ← STACK |

Не змінює |

4 |

RETI |

|

Вихід із переривання |

PC ← STACK |

I |

4 |

CPSE |

Rd, Rr |

Зрівняти, якщо рівні, пропуск наступної команди |

if(Rd=Rr) PC←PC+2 або 3 |

Не змінює |

1/2 |

CP |

Rd, Rr |

Зрівняти два регістра |

Rd – Rr |

Z,N,V,C,H |

1 |

CPC |

Rd, Rr |

Зрівняти два регістра з переносом |

Rd – Rr – C |

Z,N,V,C,H |

1 |

CPI |

Rd, K |

Зрівняти два регістра з константою |

Rd – K |

Z,N,V,C,H |

1 |

SBRC |

Rr, b |

Якщо біт в регістрі скинутий, пропуск наступної команди |

if(Rr(b)=0) PC←PC+2 або 3 |

Не змінює |

1/2 |

SBRS |

Rr, b |

Якщо біт в регістрі встановлений, пропуск наступної команди |

if(Rr(b)=1) PC←PC+2 або 3 |

Не змінює |

1/2 |

SBIC |

P, b |

Якщо біт в регістрі вводу-виводу скинутий, пропуск наступної команди |

if(P(b)=0) PC←PC+2 або 3 |

Не змінює |

1/2 |

SBIS |

P, b |

Якщо біт в регістрі вводу-виводу встановлений, пропуск наступної команди |

if(P(b)=1) PC←PC+2 або 3 |

Не змінює |

1/2 |

BRBS |

s, k |

Перехід на мітку якщо встановлений прапорець s |

if(SREG(s)=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRBC |

s, k |

Перехід на мітку якщо скинутий прапорець s |

if(SREG(s)=0) PC←PC+k+1 |

Не змінює |

1/2 |

BREQ |

k |

Перехід на мітку якщо рівно |

if(Z=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRNE |

k |

Перехід на мітку якщо не рівно |

if(Z=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRCS |

k |

Перехід на мітку якщо встановлений перенос |

if(C=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRCC |

k |

Перехід на мітку якщо скинутий перенос |

if(C=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRSH |

k |

Перехід на мітку якщо рівно або більше |

if(C=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRLO |

k |

Перехід на мітку якщо менше |

if(C=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRMI |

k |

Перехід на мітку якщо мінус |

if(N=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRPL |

k |

Перехід на мітку якщо плюс |

if(N=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRGE |

k |

Перехід на мітку якщо рівно або більше, зі знаком |

if(N XOR V=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRLT |

k |

Перехід на мітку якщо менше нуля, зі знаком |

if(N XOR V=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRHS |

k |

Перехід на мітку якщо встановлений прапорець H |

if(H=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRHC |

k |

Перехід на мітку якщо скинутий прапорець H |

if(H=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRTS |

k |

Перехід на мітку якщо встановлений прапорець T |

if(H=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRTC |

k |

Перехід на мітку якщо скинутий прапорець Т |

if(H=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRVS |

k |

Перехід на мітку якщо встановлений прапорець V (переповнення) |

if(H=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRVC |

k |

Перехід на мітку якщо скинутий прапорець V |

if(H=0) PC←PC+k+1 |

Не змінює |

1/2 |

BRIE |

k |

Перехід на мітку якщо дозволено переривання |

if(I=1) PC←PC+k+1 |

Не змінює |

1/2 |

BRID |

k |

Перехід на мітку якщо заборонено переривання |

if(I=1) PC←PC+k+1 |

Не змінює |

1/2 |

КОМАНДИ ПЕРЕСИЛКИ |

|||||

LD |

Rd, Z |

Загрузити регістр безпосередньо |

Rd ← (Z) |

Не змінює |

2 |

ST |

Z, Rr |

Записати регістр безпосередньо |

(Z) ← Rr |

Не змінює |

2 |

MOV |

Rd, Rr |

Пересилка з одного регістра в другий |

Rd ← Rr |

Не змінює |

1 |

LDI |

Rd, K |

Загрузити константу |

Rd ← K |

Не змінює |

1 |

IN |

Rd, P |

Ввід із порту |

Rd ← P |

Не змінює |

1 |

OUT |

P, Rr |

Вивід в порт |

P ← Rr |

Не змінює |

1 |

КОМАНДИ РОБОТИ З БІТАМИ |

|||||

SBI |

P, b |

Установити біт в регістрі вводу-виводу |

I/O (P, b) ← 1 |

Не змінює |

2 |

CBI |

P,b |

Скинути біт в регістрі вводу-виводу |

I/O (P, b) ← 0 |

Не змінює |

2 |

LSL |

Rd |

Логічний зсув вліво |

Rd (n+1)←Rd (n), Rd (0)←0 |

Z, C, N, V |

1 |

LSR |

Rd |

Логічний зсув вправо |

Rd (n)←Rd (n+1), Rd (7)←0 |

Z, C, N, V |

1 |

ROL |

Rd |

Зсув вліво через C |

Rd (0) ←C, Rd (n+1)←Rd (n), C←Rd (7) |

Z, C, N, V |

1 |

ROR |

Rd |

Зсув вправо через C |

Rd (7) ← C, Rd (n)←Rd (n+1), C← Rd (0) |

Z, C, N, V |

1 |

ASR |

Rd |

Арифметичний зсув вправо |

Rd (n) ← Rd (n+1), n = 0..6 |

Z, C, N, V |

1 |

SWAP |

Rd |

Обмін нібблів (тетрадами) |

Rd (3-0)←Rd(7-4), Rd 7-4) ← Rd(3-0) |

Не змінює |

1 |

BSET |

s |

Встановити прапорець |

SREG(s) ← 1 |

SREG(s) |

1 |

BCLR |

s |

Скинути прапорець |

SREG(s) ← 0 |

SREG(s) |

1 |

BST |

Rr, b |

Запам’ятати біт в T |

T ← Rr (b) |

T |

1 |

BLD |

Rd, b |

Прочитати біт із T |

Rd (b) ← T |

Не змінює |

1 |

SEC |

|

Встановити перенос |

C ← 1 |

C |

1 |

CLC |

|

Скинути перенос |

C ← 0 |

C |

1 |

SEN |

|

Встановити прапорець N |

N ← 1 |

N |

1 |

CLN |

|

Скинути прапорець N |

N ← 0 |

N |

1 |

SEZ |

|

Встановити прапорець Z |

Z ← 1 |

Z |

1 |

CLZ |

|

Скинути прапорець Z |

Z ← 0 |

Z |

1 |

SEI |

|

Дозволити переривання |

I ← 1 |

I |

1 |

CLI |

|

Заборонити переривання |

I ← 0 |

I |

1 |

SES |

|

Встановити прапорець S |

S ← 1 |

S |

1 |

CLS |

|

Скинути прапорець S |

S ← 0 |

S |

1 |

SEV |

|

Встановити прапорець V |

V ← 1 |

V |

1 |

CLV |

|

Скинути прапорець V |

V ← 0 |

V |

1 |

SET |

|

Встановити прапорець T |

T ← 1 |

T |

1 |

CLT |

|

Скинути прапорець T |

T ← 0 |

T |

1 |

SEH |

|

Встановити прапорець H |

H ← 1 |

H |

1 |

CLH |

|

Скинути прапорець H |

H ← 0 |

H |

1 |

NOP |

|

Немає операції |

|

Не змінює |

1 |

SLEEP |

|

Зупинка (сплячий режим) |

|

Не змінює |

3 |

WDR |

|

Скидання охоронного таймеру |

|

Не змінює |

1 |

Регістри та їх операнди:

Rd – регістр призначення (і джерело) в регістровому файлі;

Rr – регістр джерело в регістровому файлі;

K – константа;

k – мітка;

b – біт в регістровому файлі або біт в регістрі вводу-виводу;

s – біт в регістрі статусу;

X, Y, Z – регістри непрямої адресації (X=R27:R26, Y=R29:R28, Z=R31:R30);

Р – адрес порту вводу-виводу;