- •10.17. Обратная связь в усилителях

- •10.18. Влияние отрицательной обратной связи на основные параметры усилителя

- •10.19. Усилители с отрицательной обратной связью

- •10.20. Усилители мощности

- •10.21. Генераторы синусоидальных колебаний

- •10.22. Классификация электронных импульсных и цифровых устройств

- •10.23. Нелинейный режим работы операционного усилителя. Компаратор

- •10.24. Ключевой режим работы транзистора

- •10.25. Логические элементы

- •10.26. Электронные импульсные устройства с временно устойчивыми состояниями

- •10.27. Электронные импульсные устройства с устойчивыми состояниями. Триггеры

- •Itanium 9300 Tukwila

10.27. Электронные импульсные устройства с устойчивыми состояниями. Триггеры

Триггерами называются электронные импульсные устройства с двумя устойчивыми состояниями, которым соответствуют различные значения напряжений на информационных выходах. Они применяются в счетчиках импульсов напряжения, делителях частоты следования импульсов напряжения и т.д.

По способу управления различают асинхронные и синхронные триггеры.

В асинхронных триггерах переключение из одного устойчивого состояния в другое осуществляется действием определенной совокупности импульсов напряжения на управляющих входах.

В синхронных триггерах такое переключение возможно только при совпадении во времени определенной совокупности импульсов напряжения на управляющих входах и импульса напряжения на входе синхронизации.

Триггеры реализуются на основе логических элементов и выпускаются в виде интегральных схем. Поэтому далее ограничимся рассмотрением функциональных возможностей различных типов триггеров, пользуясь их условными обозначениями. Наибольшее практическое применение имеют асинхронные RS- и синхронные D- и JK-триггеры.

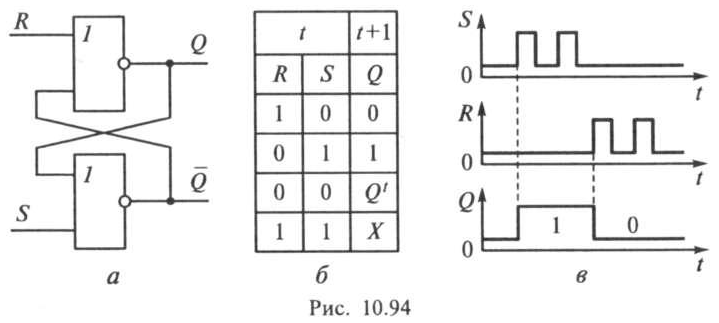

RS-триггер

(Reset

— Set,

т.е. сброс — установка) реализуется на

основе логических элементов ИЛИ — НЕ

на два входа (рис. 10.94, а),

где обозначены прямой Q

и

инверсный

![]() информационные

выходы. Работу RS-триггера

иллюстрируют таблица истинности на

рис. 10.94, б,

где указаны значения сигналов на

управляющих входах R

и

S

в

некоторый момент времени t

и

соответствующие им значения на выходе

Q

в

момент времени t

+ 1 после окончания переходного процесса,

и временная диаграмма (рис. 10.94, в).

информационные

выходы. Работу RS-триггера

иллюстрируют таблица истинности на

рис. 10.94, б,

где указаны значения сигналов на

управляющих входах R

и

S

в

некоторый момент времени t

и

соответствующие им значения на выходе

Q

в

момент времени t

+ 1 после окончания переходного процесса,

и временная диаграмма (рис. 10.94, в).

Состояние триггера сохраняется (Q=Q') при совокупности сигналов на входах R = 0 и S = 0 и не определено при R = 1 и S= 1. Последнее состояние запрещено.

RS-триггер

с инверсными значениями сигналов на

входах

![]() и

и

![]() реализуется

на основе логических элементов И — НЕ.

Его схема, таблица истинности и временнáя

диаграмма приведены на рис. 10.95, а

— в.

Состояние

триггера сохраняется при значениях

сигналов на его входах

=

1 и

=

1 и не определено при

= 0

и

=

0. Последнее состояние запрещено.

реализуется

на основе логических элементов И — НЕ.

Его схема, таблица истинности и временнáя

диаграмма приведены на рис. 10.95, а

— в.

Состояние

триггера сохраняется при значениях

сигналов на его входах

=

1 и

=

1 и не определено при

= 0

и

=

0. Последнее состояние запрещено.

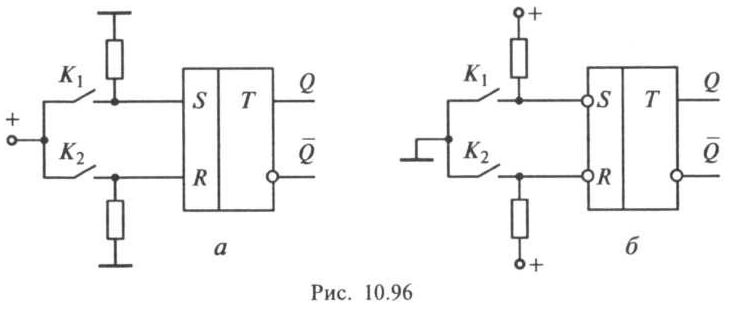

Условные обозначения RS-триггеров с прямыми и инверсными входами приведены на рис. 10.96, а и б. Кратковременным замыканием ключа К1 или К2 устанавливаются состояния триггеров Q = 1 или Q = 0.

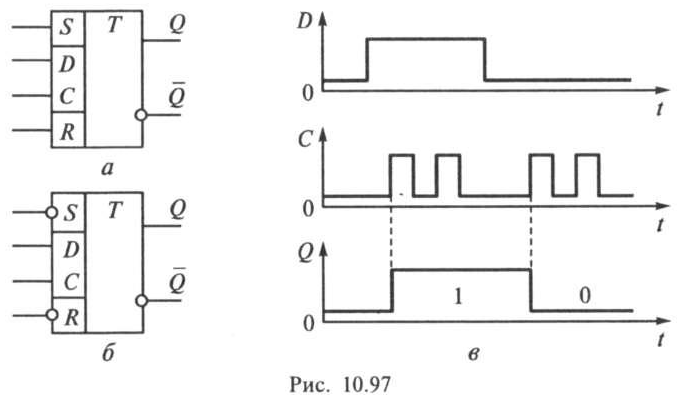

D-триггер имеет прямые (рис. 10.97, а) или инверсные (рис. 10.97, б) установочные входы R и S, один управляющий вход D и вход синхронизации С. Входы R и S называются установочными потому, что служат для предварительной установки D-триггера в состояние Q = 1 или Q = 0 аналогично представленному на рис. 10.96.

Сигнал на управляющем входе D = 1 или D = 0 устанавливает триггер в устойчивое состояние с одноименным значением на прямом информационном выходе Q = 1 или Q = 0 только при одновременном действии импульса положительной полярности на входе синхронизации. Обычно переключение триггера происходит в течение времени действия переднего фронта импульса синхронизации (рис. 10.97, в).

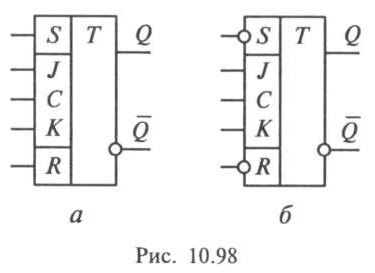

J К-триггер

имеет

ряд преимуществ по сравнению с RS-

и D-триггерами.

Его условные обозначения с прямыми или

инверсными установочными входами R

и S

приведены на рис. 10.98, а

и

б,

где

обозначено: J

и К

—

управляющие

входы, С

—

вход

синхронизации.

К-триггер

имеет

ряд преимуществ по сравнению с RS-

и D-триггерами.

Его условные обозначения с прямыми или

инверсными установочными входами R

и S

приведены на рис. 10.98, а

и

б,

где

обозначено: J

и К

—

управляющие

входы, С

—

вход

синхронизации.

Р ассмотрим

правила работы JК-триггера,

положив, что его исходное состояние

установлено.

ассмотрим

правила работы JК-триггера,

положив, что его исходное состояние

установлено.

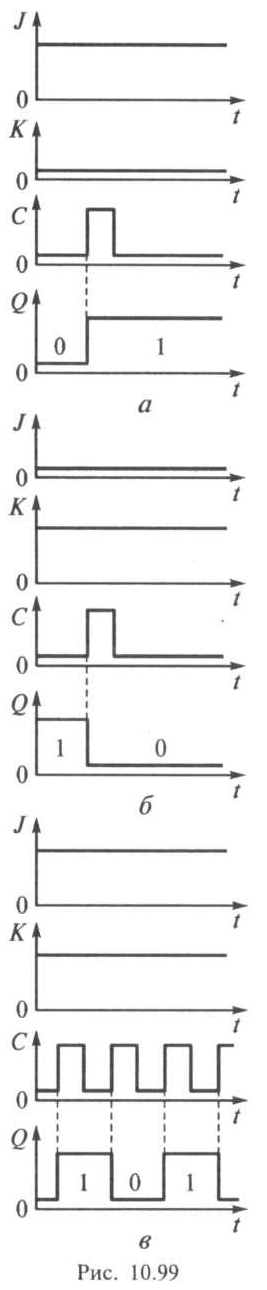

Если J = 1 и К = 0, то в течение времени действия переднего фронта импульса синхронизации положительной полярности триггер установится в состояние Q = 1 (рис. 10.99, а).

Если J = 0 и К = 1, то в течение времени действия переднего фронта импульса синхронизации положительной полярности триггер установится в состояние Q = 0 (рис. 10.99, б).

Е

сли

J

= 1 и К

=

1,

то независимо от своего исходного

состояния Q

триггер

будет переключаться в течение времени

действия переднего фронта импульса

синхронизации положительной полярности.

При этом частота изменения напряжения

на выходе триггера будет в 2 раза меньше

частоты импульсов синхронизации (рис.

10.99, в).

сли

J

= 1 и К

=

1,

то независимо от своего исходного

состояния Q

триггер

будет переключаться в течение времени

действия переднего фронта импульса

синхронизации положительной полярности.

При этом частота изменения напряжения

на выходе триггера будет в 2 раза меньше

частоты импульсов синхронизации (рис.

10.99, в).Если J = 0 и К = 0, то исходное состояние Q триггера под действием импульса синхронизации не изменится.

На практике часто встречаются двухступенчатые JК-триггеры (условное обозначение ТТ ) с прямыми или инверсными установочными входами R и S (рис. 10.100, а и б). Правила их работы отличаются от описанных выше тем, что изменение состояния триггера происходит не в течение времени действия переднего фронта импульса синхронизации, а в течение времени действия его заднего фронта.

На основе логических элементов и импульсных устройств строятся цифровые логические автоматы.

Названия микросхем в зависимости от степени интеграции, разные для цифровых и аналоговых микросхем (указано количество элементов для цифровых схем):

малая интегральная схема (МИС) — до 100 элементов в кристалле,

средняя интегральная схема (СИС) — до 1000 элементов в кристалле,

большая интегральная схема (БИС) — до 10000 элементов в кристалле,

сверхбольшая интегральная схема (СБИС) — до 1 миллиона элементов в кристалле,

ультрабольшая интегральная схема (УБИС) — до 1 миллиарда элементов в кристалле,

гигабольшая интегральная схема (ГБИС) — более 1 миллиарда элементов в кристалле.

В настоящее время название УБИС и ГБИС практически не используется (например, последние версии процессоров Itanium, 9300 Tukwila, содержат два миллиарда транзисторов), и все схемы с числом элементов, превышающим 10 000, относят к классу СБИС, считая УБИС его подклассом.

Itanium (произносится: Айтэниум) — микропроцессор, разработанный совместно компаниями Intel и Hewlett-Packard. Впервые был представлен 29 мая 2001 года. По состоянию на весну 2011 года процессорам присваиваются четырехзначные номера, подобно Intel Xeon.