- •Нальчик

- •В.Ч. Кудаев

- •Лабораторная работа 1 Логические элементы

- •1. Теоретические основы лабораторной работы

- •1.1. Основы булевой алгебры

- •1.2. Технические характеристики универсального лабораторного стенда

- •2. Задание на лабораторную работу

- •2.1. Для лэ, соответствующих вашему варианту (табл. 2):

- •2.2. Реализовать логическую функцию, соответствующую вашему варианту, используя заданный тип лэ (табл. 3). Снять таблицу истинности лэ или соединения лэ (схемы), реализующих требуемую функцию.

- •3. Контрольные вопросы

- •Лабораторная работа 2 Проектирование комбинационных цифровых устройств в заданном базисе логических элементов

- •1. Теоретические основы лабораторной работы

- •1.1. Формы представления алгоритмов функционирования кцу

- •. Алгоритм перехода от таблицы истинности логической функции к ее записи в виде сднф

- •1.3. Алгоритм перехода от таблицы истинности логической функции к ее записи в виде скнф

- •1.4. Минимизация логических функций

- •1.5. Алгоритм минимизации логических функций, заданных в сднф при помощи карт Карно

- •1.6. Минимизация частично определенных и инверсных логических функций

- •1.7. Преобразование минимальных форм логических функций к виду, реализуемому лэ заданного функционально полного набора

- •1.8. Минимальные формы в монофункциональных базисах

- •1.9. Проектирование схемы кцу в заданном базисе лэ

- •1.10. Проектирование многовыходных кцу

- •2. Задание на лабораторную работу

- •3. Содержание отчета

- •4. Контрольные вопросы

- •Лабораторная работа 3 Проектирование и исследование дешифраторов

- •1. Теоретические основы лабораторной работы

- •1.1. Линейные дешифраторы

- •1.2. Пирамидальные дешифраторы

- •1.3. Особенности проектирования неполных дешифраторов

- •1.4. Применение дешифратора в качестве универсального логического элемента

- •2. Задание на лабораторную работу

- •3. Содержание отчета по лабораторной работе

- •4. Контрольные вопросы

- •Лабораторная работа 4 Двоичные сумматоры

- •1. Теоретические основы лабораторной работы

- •1.1. Правила выполнения арифметических операций

- •1.2. Двоичные сумматоры

- •1.3. Двоичные вычитатели

- •1.4. Двоичные сумматоры-вычитатели

- •2. Задание на лабораторную работу

- •4. Контрольные вопросы

- •Лабораторная работа 5 Цифровые компараторы

- •1. Теоретические основы лабораторной работы

- •2. Задание на лабораторную работу

- •3. Контрольные вопросы

- •Лабораторная работа 6 Мультиплексоры и демультиплексоры

- •1. Теоретические основы лабораторной работы

- •1.1. Мультиплексоры

- •1 0 1 2 3 0 1 2 3 0 1 2 3 .2. Демультиплексоры

- •1.3. Применение мультиплексоров и демультиплексоров

- •2. Задание

- •3. Контрольные вопросы

- •Лабораторная работа 7 Синтез и исследование триггеров

- •1. Теоретические основы лабораторной работы

- •1.1. Цифровые устройства последовательностного типа

- •1.2. Триггеры

- •1.3. Схемотехника триггеров

- •2. Задание

- •3. Содержание отчета

- •4. Контрольные вопросы

- •Лабораторная работа 8 Регистры

- •1. Теоретические основы лабораторной работы

- •1.1. Параллельный регистр

- •1.2. Последовательный регистр

- •2. Задание

- •4. Контрольные вопросы

- •Лабораторная работа 9 Цифровые счетчики импульсов

- •1. Теоретические основы лабораторной работы

- •1.1. Суммирующие двоичные счетчики

- •1.2. Вычитающие двоичные счетчики

- •1.3. Реверсивные двоичные счетчики

- •1.4. Счетчики с произвольным значением модуля счета

- •2. Домашнее задание

- •3. Задание на лабораторную работу

- •4. Содержание отчета

- •5. Контрольные вопросы

- •Принятые сокращения

- •Литература

- •Содержание

- •360004, Г. Нальчик, ул. Чернышевского, 173

- •3 60004, Г. Нальчик, ул. Чернышевского, 173.

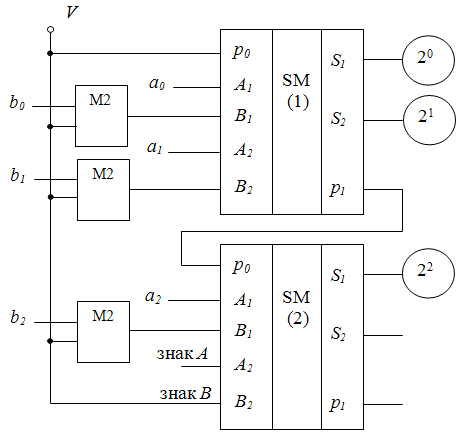

1.4. Двоичные сумматоры-вычитатели

Теперь, когда мы знаем, что двоичные сумматоры можно использовать как для сложения, так и для вычитания, спроектируем схему универсального устройства – сумматора-вычитателя, положив в ее основу схему вычитателя (рис. 4б), в которой вместо четырех одноразрядных сумматоров используем – две ИС 2-разрядных сумматоров К155ИМ2, а вместо инверторов – ЛЭ «М2». В преобразованном виде эта схема приведена на рис. 5. Чтобы эта схема работала как двоичный сумматор, достаточно на управляющий вход V подать уровень логического 0. При этом через ЛЭ «М2» числовые разряды b2b1b0 двоичного числа В проходят без инверсии. Кроме того, логический 0 с управляющего входа V поступает на вход переноса младшего разряда двоичного сумматора. Таким образом, при V=0 схема складывает двоичные числа А и В.

Рис. 5. Функциональная схема сумматора-вычитателя

Чтобы схема работала как вычитатель на управляющем входе V нужно установить уровень логической 1. В этом случае ЛЭ «М2» действуют как инверторы числовых разрядов b2, b1, b0. Кроме того, логическая 1 с управляющего входа V поступает на вход переноса младшего разряда двоичного сумматора. В результате получаем, что двоичное число В будет представлено в дополнительном коде и, следовательно, схема осуществляет операцию вычитания А-В. На выходе S2 сумматора SM2 при V=1 (вычитании) формируется знак результата (разности), а при V=0 (суммировании) – числовой разряд суммы с весом 23.

2. Задание на лабораторную работу

2.1. Используя ЛЭ, расположенные стенде, спроектировать схему и исследовать работу (снять таблицу истинности) полусумматора.

Пояснения к выполнению п. 2.1

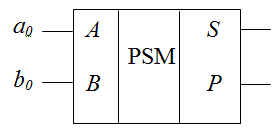

Рис. 6. Условное изображение полусумматора

Полусумматор (рис. 6) – это цифровое устройство, осуществляющее суммирование младших разрядов а0 и b0 двоично кодированных чисел А и B и имеющее два выхода – S, на котором формируется сумма младшего разряда и p, на котором формируется перенос (1 или 0) в следующий старший разряд.

2.2. Исследовать работу (снять таблицу истинности) одноразрядного сумматора (рис. 2).

2.3. Исследовать работу (снять таблицу истинности) 2-разрядного сумматора К155ИМ2.

Пояснения к выполнению п. 2.3

Произвольно выбрав 4–5 комбинаций значений 2-разрядных чисел А= а1 а0 и B= b1 b0, получите соответствующие им результаты суммирования. Результаты сведите в таблицу:

|

а1 а0 |

b1 b0 |

S2 S1 S0 |

1 |

. . |

. . |

. . . |

. . . |

. . . |

. . . |

. . . |

2.4. Исследовать работу 4-разрядного сумматора-вычитателя.

Пояснения к выполнению п. 2.4

Собрать схему сумматора-вычитателя (рис. 5) и выполнить арифмети-ческие операции, соответствующие вашему варианту (см. табл.).

№ Варианта (бригады) |

Выполняемые операции |

||

1 |

2 |

3 |

|

1 |

A+B=6+1 |

A-B=6-1 |

A-B=1-6 |

2 |

A+B=5+2 |

A-B=5-2 |

A-B=2-5 |

3 |

A+B=4+3 |

A-B=4-3 |

A-B=3-4 |

4 |

A+B=7+2 |

A-B=7-2 |

A-B=2-7 |

5 |

A+B=5+7 |

A-B=5-7 |

A-B=7-5 |