- •Методические указания

- •"Архитектура компьютеров"

- •Задание

- •Исходные данные для проектирования

- •Содержание пояснительной записки

- •Постановка задач проекта

- •Разработка гипотетического микропроцессора

- •Календарный план выполнения проекта

- •Литература

- •Коды режимов адресации для арифметических операций i80386

- •Режимы работы мп i80386

Режимы работы мп i80386

1 Сброс и инициализация

При появлении на входе RESET положительного импульса микропроцессор прекращает выполнение текущей команды или выходит из состояния "Индикация останова" и устанавливается в исходное состояние. Если на падающем фронте RESET вход BUSY находится в состоянии низкого уровня, микропроцессор выполняет самопроверку. На тестирование приблизительно половины оборудования i80386 затрачивается 219 тактов. Результат самопроверки (сигнатура) заносится в регистр ЕАХ. Если самопроверка прошла успешно, содержимое регистра равно OOOOOOOOh.

В табл. 1.1 показано содержимое регистров микропроцессора перед выполнением первой команды.

Таблица 1.1

Регистр |

Значение |

ЕАХ |

00000000h |

ЕВХ |

xxxxxxxxh |

ЕСХ |

xxxxxxxxh |

EDX |

xxxx03uuh |

ESI |

xxxxxxxxh |

EDI |

xxxxxxxxh |

ЕВР |

xxxxxxxxh |

ESP |

xxxxxxxxh |

EIP |

0000FFF0h |

EFLAGS |

00000002h |

CRO |

000000u0h |

Дескриптор CS: базовый адрес |

FFFF0000h |

ограничитель |

FFFFh |

CS |

F000h |

DS |

0000h |

SS |

0000h |

ES |

0000h |

FS |

0000h |

GS |

0000h |

Обозначения в таблице:

x - биты устанавливаются произвольно;

u - биты устанавливаются в зависимости от условий:

в регистре DX младшие 8 разрядов содержат двоичное число, отражающее номер модификации микропроцессора (устанавливается фирмой); старшие 8 разрядов содержат идентификатор компонента i80386, равный 03h;

в регистре CRO бит ЕТ устанавливается в соответствии с типом сопроцессора.

В персональных ЭВМ типа IBM PC 386/AT, как правило, предусматривается возможность установки сопроцессора 180387 или 180287. Определив наличие сопроцессора 180387 по низкому уровню сигнала на входе ERROR во время падающего фронта сигнала RESET, микропроцессор i80386 устанавливает бит ЕТ. Наличие сопроцессора 180287 определяется программным способом с помощью команд:

FNINIT (программный сброс сопроцессора, инициализация регистров управления), FSTSW АХ (загрузка содержимого регистра состояния в регистр АХ i80386). Если в младших 8 разрядах регистра АХ будет хотя бы одна единица, то сопроцессора 180287 в ПЭВМ нет.

Предлагается следующая программа, реализующая определение наличия сопроцессора 180287:

FNINIT ; Инициализация 180287

FSTSW AX ; Загрузка в регистр АХ значения ; регистра состояния 180287

OR AL, AL ; Определение наличия единиц в; младшем байте регистра состояния

JNZ Ml ; Проверка условия

SMSW АХ ; Загрузка MSW в регистр АХ

OR AL, 02h ; Установка бита МР

LMSW АХ ; Загрузка MSW значением АХ

JMP M2 ; Переход в программу - ,

Ml: SMSW АХ ; Загрузка MSW в регистр АХ

OR AL, 04h ; Установка бита ЕМ

LMSW АХ ; Загрузка MSW значением АХ

M2: ; Продолжение программы

После сброса МП формирует адрес первой команды - физический адрес FFFFFFFOh. Если первой командой является команда внутрисегментного перехода (вызова), то будет выполняться программа, расположенная в верхней 64-Кбайтной зоне 4-Гбайтного физического адресного пространства до тех пор, пока не встретится команда межсегментного перехода (вызова). При выполнении этой команды разряды А20-А31 шины адреса устанавливаются в нуль для циклов обращения к сегментам программ. При этом физическое адресное пространство микропроцессора сжимается до одного Мбайта.

В персональных ЭВМ типа IBM PC 386/AT базовая система в/в (BIOS), записанная в ПЗУ, располагается в верхних адресах (зарезервировано 128 Кбайт) первого Мбайта физического адресного пространства (см. рис. 1.1). Первая команда межсегментного перехода должна быть расположена в адресном пространстве BIOS (производится переадресация при считывании ее из памяти).

Рис. 1.1 - Адресное пространство памяти ПЭВМ PC 386/AT

После сброса и выполнения команды межсегментного перехода МП i80386 начинает работать в реальном режиме, почти идентичном режиму работы 18086.

2. Реальный режим

Согласно концепции развития архитектуры семейства микропроцессоров i80x86 (обеспечение совместимости снизу-вверх) реальный режим дает возможность выполнять программы, созданные для МП 18086/8088. Поэтому он широко используется в персональных компьютерах PC AT/386, работающих под управлением операционной системы MS-DOS. Однако в МП i80386 имеются дополнительные возможности, обеспечивающие более быстрое выполнение программ в реальном режиме, которые показаны в разделе 2.2.

2.1 Адресация памяти

В реальном режиме страничное преобразование адреса запрещено, и линейные адреса соответствуют физическим.

Сегменты имеют длину 64 Кбайта и могут перекрываться. 32-разрядный физический адрес формируется из двух компонент (см. рис.2.1):

- 16-разрядного эффективного адреса;

- содержимого соответствующего сегментного регистра, сдвинутого влево на ' 4 разряда (20-разрядного адреса).

Эффективный адрес в общем случае вычисляется как сумма трех 16-разрядных составляющих: базы, смещения и индекса. .

Способы адресации в 16-разрядном режиме показаны в табл. 2.1

Поле R/M определяет либо один из восьми регистров общего назначения, либо один из способов адресации (в зависимости от поля MOD).

В поле REG двухоперандной команды находится номер одного из восьми регистров, содержащего второй операнд; в однооперандных командах это поле используется для расширения поля кода операции.

Поле MOD значением 11 задает регистровую адресацию (оба операнда - в регистрах), в остальных трех случаях используется для выбора трех групп (каждая по восемь) способов адресации.

Табл. 2.2 определяет поля MOD и R/M во всех 16-разрядных способах адресации. Нужно заметить, что для адресации памяти используются только регистры ВХ, SI, DI и ВР (регистр SP неявно используется для адресации памяти командами PUSH, POP, PUSHA, POPA. CALL и INT n).

Рис. 2.1 - Формирование физического адреса в реальном режиме

Таблица 2.1 - Способы адресации в 16-разрядном режиме

NN пп |

Наименование способа адресации |

Компоненты адреса |

Пример |

1 |

Непосредственная |

Константа |

MOV AX, 0002h |

2 |

Прямая |

d (смещение) |

MOV BX, [25A6h] |

3 |

Регистровая |

AX, BX, CX, DX, SI, DI, SP |

MOV BX, AX |

4 |

Косвенная регистровая |

[BX],[BP],.[SI],[DI], |

MOV AX. [ВХ1 |

5 |

Базовая или индексная со смещением |

[ВХ, ВР, SI, Dl]+d |

MOV AX, [BP+12] |

6 |

Базовая индексная без смещения |

BP+DI], [BX+SI], BP+Sl], [BX+Dl] |

MOV BX, [BP+SI] |

7 |

Базовая индексная со смещением |

BP+DI]+d,[BP+SI]+d, BX+Sll+d.lBX+Dll+d |

MOV AX, [BP+SI+20] |

Таблица 2.2. - Поля MOD и R/M во всех 16-разрядных способах адресации

REG |

Операнд 1 |

MOD |

R/M |

Операнд 2 |

000 |

Регистр EAX/AX/AL |

00 |

000 |

Память DS[BX+SI] |

001 |

Регистр ECX/CX/CL |

00 |

001 |

Память DS:[BX+DI] |

010 |

Регистр EDX/DX/DL |

00 |

010 |

Память SS:[BP+SI] |

Oil |

Регистр EBX/BX/BL |

00 |

011 |

Память SS:[BP+DI] |

100 |

Регистр ESP/SP/AH |

00 |

100 |

Память DS:[SI]

|

101 |

Регистр ЕВР/ВР/СН |

00 |

101 |

Память DS:[DI]

|

110 |

Регистр ESI/SI/DH |

00 |

110 |

Память DS dl6 |

111 |

Регистр EDI/DI/BH |

00 |

111 |

Память DS:[ВХ] |

|

|

01 |

000 |

Память DS:[BX+SI+d8]

|

|

|

01 |

001 |

Память DS:[BX+DI+d8]

|

|

|

01 |

010 |

Память SS:[BP+SI+d8]

|

|

|

01 |

011 |

Память SS:[BP+DI+dS]

|

|

|

01 |

100 |

Память DS:[SI+d8]

|

|

|

01 |

101 |

Память DS:[DI+d8]

|

|

|

01 |

110 |

Память SS:[BP+d8]

|

|

|

01 |

111 |

Память DS:[BX+d8]

|

|

|

10 |

000 |

Память DS:[BX+SI+dl6]

|

|

|

10 |

001 |

Память DS:[BX+DI+dl6]

|

|

|

10 |

010 |

Память SS:[BP+SI+dl6]

|

|

|

10 |

011 |

Память SS:[BP+DI+dl6]

|

|

|

10 |

100 |

Память DS:[SI+dl6]

|

|

|

10 |

101 |

Память DS:[DI+dl6]

|

|

|

10 |

110 |

Память SS:[BP+dl6]

|

|

|

10 |

111 |

Память DS:[BX+dl6]

|

|

|

11 |

000 |

Регистр EAX/AX/AL |

|

|

11 |

001 |

Регистр ECX/CX/CL |

|

|

11 |

010 |

Регистр EDX/DX/DL |

|

|

11 |

011 |

Регистр EBX/BX/BL |

|

|

11 |

100 |

Регистр ESP/SP/AH |

|

|

11 |

101 |

Регистр ЕВР/ВР/СН |

|

|

11 |

110 |

Регистр ESI/SI/DH |

|

|

11 |

111 |

Регистр EDI/DI/BH |

Команда обращается за операндами в соответствии с байтом MOD R/M, следующим за кодом операции и имеющим следующий формат:

Когда способ адресации задает только базовый регистр, он может использовать любой из регистров - DX, SI, DI или ВР. Если в формировании адреса участвуют базовый и индексный регистры, то такими парами могут быть BX+SI, BX+DI, BP+SI, BP+DI. Смещение может быть задано 16-разрядным или 8-разрядным (со знаком).

Возможны различные комбинации компонент адреса при использовании байта MOD R/M.

2.2. Команды и префиксы реального режима

В реальном режиме команды МП i80386 оперируют над 8- и 16-разрядными операндами, обеспечивая совместимость с МП 18086 на уровне объектных кодов.

В систему команд МП i80386 входят, кроме команд i8086, дополнительные команды, доступные в реальном режиме:

Не все команды i80386 разрешены в реальном режиме: девять команд защищенного режима в случае их использования в реальном режиме вызывают исключительную ситуацию:

LTR, STR, LLDT, SLDT, ARPL, LSL, LAR, VERR, VERW.

Все префиксы i80386, показанные на рис. 2.9, доступны в реальном режиме. Префиксы размера операнда и размера адреса, в частности, могут добавить новые возможности в реальном режиме, позволяя использовать 32-разрядные операнды и адреса.

Префикс размера операнда позволяет манипулировать 32-разрядными операндами. Например, использование префикса размера операнда позволяет i80386 в реальном режиме выполнять арифметические операции над 32-разрядными операндами и обрабатывать строки по 32 разряда за одну операцию (ADD ЕАХ, ЕВХ).

Доступный в реальном режиме префикс размера адреса обеспечивает доступ к 32-разрядным способам адресации, рассмотренным в разделе 2.5.3 (MOV AX, [ЕВХ]). Правильное использование префикса размера адреса в реальном режиме требует большой осторожности, потому что необходимо избегать формирования больших эффективных адресов - больше 65535: в реальном режиме граница сег-

мента фиксирована и равна 65535.

Поэтому 32-разрядный размер адреса и данных предпочтительно использовать для защищенного режима работы i80386, в котором размеры сегмента и пространства линейных адресов много больше, чем в реальном режиме.

Следует также обратить внимание на то, что в МП 18086 максимальное значение физического адреса составляет FFFFFh (1 Мбайт). В МП i80386 в реальном режиме максимальное значение физического адреса - сумма селектора и смещения:

селектор (сдвинутый): F F F F(0)

смещение: F F F F

адрес: 1 О F F E F (1,064 Мбайта)

Таким образом, может возникнуть ситуация, когда адрес пересечет границу первого Мбайта памяти. В программах, написанных для МП i8086/88, используется факт "заворачивания" адреса вокруг границы сегмента. Чтобы обеспечить их правильное выполнение в персональных ЭВ М на базе МП i80386, осуществляется аппаратная блокировка адресной линии А20 (А20=0) с помощью порта в контроллере клавиатуры, состоянием которого можно управлять программно.

3 Защищенный режим

В защищенном режиме аппаратные средства МП i80386 позволяют защитить операционную систему от несанкционированного доступа со стороны программ пользователя, а также изолировать задачи друг от друга. Обеспечивается автоматическое переключение с одной задачи на другую за сравнительно короткое время. По сравнению с реальным режимом значительно увеличено линейное адресное пространство (до 4 Гбайт).

В защищенном режиме может быть использована как сегментная, так и страничная организация памяти.

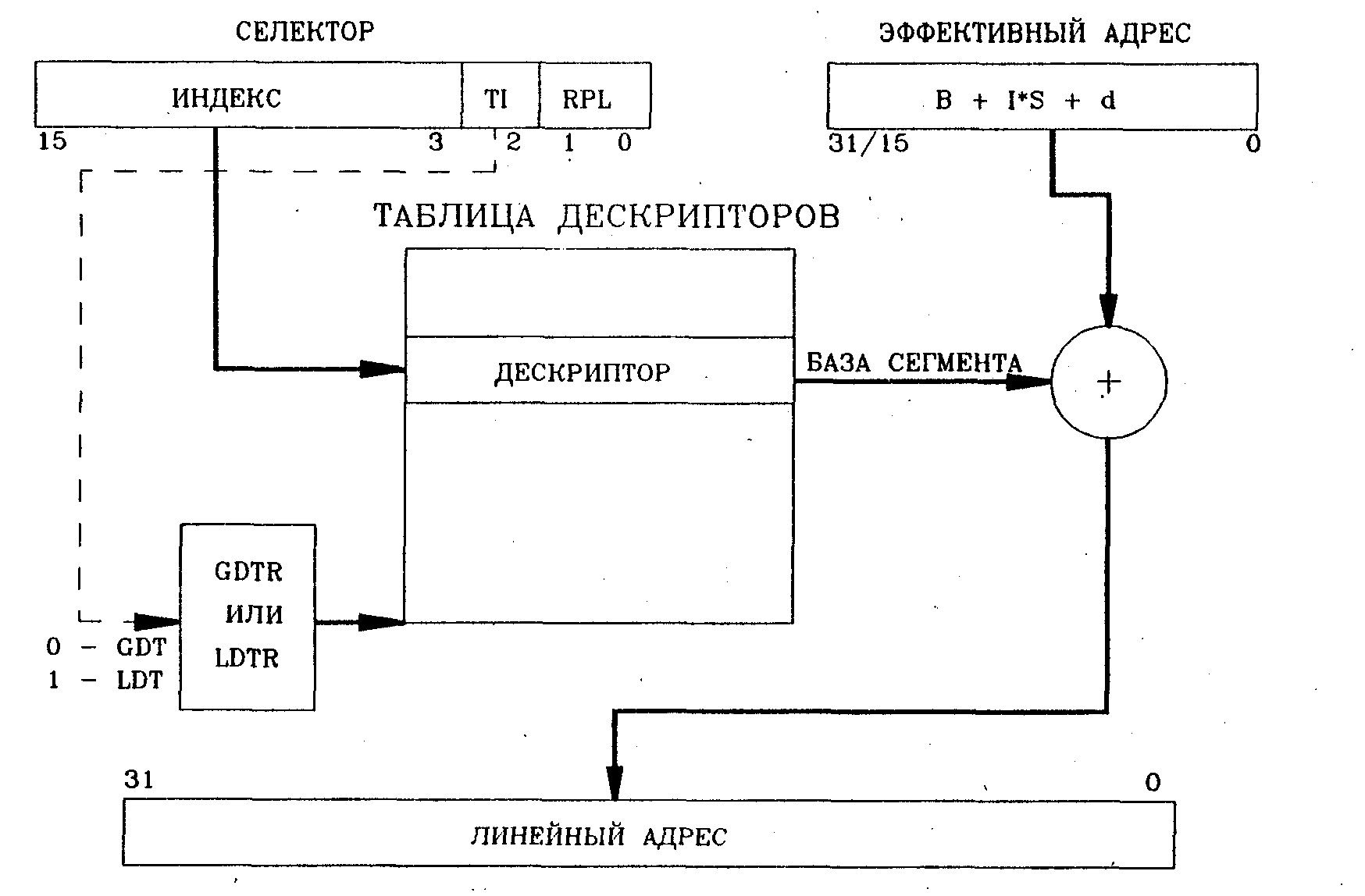

Схема формирования физического адреса приведена на рис. 3.1

3.1 Сегментная организация памяти

3.1.1 Формирование физического адреса

В защищенном режиме для формирования линейного адреса используются две компоненты (см. рис. 3.1):

Рис. 3.1 - Схема формирования физического адреса

Рис. 3.2 - Схема формирования линейного адреса

- 16-разрядный селектор для определения линейного базового адреса сегмента;

- 16- или 32-разрядный эффективный адрес.

Селектор сегментного регистра содержит три поля:

- RPL - запрашиваемый уровень привилегии;

- TI - индикатор таблицы;

- ИНДЕКС.

Поле RPL используется для реализации защиты сегментов. Индекс селектора и поле TI позволяют определить соответствующий дескриптор, который может быть расположен в глобальной таблице дескрипторов GDT (Т1=0) или в локальной таблице дескрипторов LDT (TIM). При изменении селектора в сегментном регистре (например, при выполнении команды межсегментного перехода) дескрипторавтоматически загружается из таблицы в регистр дескриптора. Дескрипторы имеют длину 8 байтов и содержат 24- или 32-разрядный базовый адрес, размер которого зависит от режима адресации. Назначение остальных полей дескриптора показано в разделе 3.1.2.

Базовый адрес сегмента, содержащегося в дескрипторе, суммируется с эффективным адресом; в результате образуется линейный адрес.

Процесс формирования эффективного адреса зависит от режима, способа адресации и наличия в команде байта SIB (в случае 32-разрядного режима адресации) .

Микропроцессор i80386 поддерживает 16-разрядный, совместимый с МП i80286, и 32-разрядный режимы адресации.

При 16-разрядном режиме адресации используются те же способы адресации и компоненты для формирования эффективного адреса, что и в реальном режиме работы.

Если определен 32-разрядный режим адресации при отсутствии в команде байта SIB, в качестве компонентов эффективного адреса используется содержимое одного из регистров общего назначения (ЕАХ, ЕСХ, EDX, ЕВХ, ЕВР, ESI, EDI) и смещение.

Эффективный адрес вычисляется в соответствии со значением байта MOD R/M, следующего за кодом операции и имеющего формат:

Поле R/M определяет либо один из восьми регистров общего назначения, либо один из способов адресации (в зависимости от поля MOD (см. табл. 3.1).

В поле REG двухоперандной команды находится номер одного из восьми регистров, содержащего второй операнд; в однооперандных командах это поле используется для расширения кода операции.

Поле MOD задает вид адресации операндов:

MOD=11 - регистровая адресация (оба операнда находятся в регистрах); в остальных трех случаях MOD определяет разрядность смещения при адресации операнда в памяти:

00 - смещение отсутствует,

01 - смещение 8-разрядное,

10 - смещение 32-разрядное.

Значение R/M = 100 указывает, что за байтом MOD R/M следует байт SIB.

Таблица 3.1. Значения MOD R/M

REG |

Операнд 1 |

MOD |

R/M |

Операнд 2 |

000 001 010 O1l 100 101 110 111 |

Регистр EAX/AX/AL Регистр ECX/CX/CL Регистр EDX/DX/DL Регистр EBX/BX/BL Регистр ESP/SP/AH Регистр ЕВР/ВР/СН Регистр ESI/SI/DH Регистр EDI/DI/BH |

00 00 00 00 00 00 00 00 |

000 001 010 011 100 101 110 111 |

Память DS:[EAX] Память DS:[ECX] Память DS:[EDX] Память DS:[EBX] SIB Память DS:[d32] Память DS:[ESI] Память DS:[EDI]

|

• |

01 01 01 01 01 01 01 01 |

000 001 010 011 100 101 110 111 |

Память DS:[EAX + d8] Память DS:[ECX + d8] Память DS:[EDX + d8] Память DS:[EBX + d8] SIB Память SS:[EBP + d8] Память DS:[ESI + d8] Память DS:[EDI + d8] |

|

Продолжение таблицы 3.1

• |

10 10 10 10 10 10 10 10 |

000 001 010 011 100 101 110 111 |

Память DS:[EAX + d32] Память DS:[ECX + d32] Память DS:[EDX + d32] Память DS:[EBX + d32] SIB Память SS:[EBP + d32] Память DS:[ESI + d32] Память DS:[EDI + d32] |

11 11 11 11 11 11 11 11 |

000 001 010 011 100 101 110 111 |

Регистр EAX/AX/AL Регистр ECX/CX/CL Регистр EDX/DX/DL Регистр EBX/BX/BL Регистр ESP/SP/AH Регистр ЕВР/ВР/СН Регистр ESI/SI/DH Регистр EDI/DI/BH |

Формат байта SIB:

Поле BASE (В) определяет базовый регистр. Поле INDEX (I) определяет индексный регистр.

Поле SS (S) определяет масштаб (1, 2,4 или 8), на который умножается содержимое индексного регистра. Способы адресации приведены в таблице 3.2. Кодировка байта SIB показана в табл. 3.3.

Таблица 3.2 - Способы адресации в 32-разрядном режиме

N |

Способ адресации |

Компоненты адреса |

Пример |

|

1 |

Непосредственная |

Константа |

MOV ЕАХ. 00000002h |

|

2 |

Прямая |

d |

ADD ЕВХ, [00025364h] |

|

3 |

Регистровая |

ЕАХ, ЕВХ, ЕСХ, EDX, ESI, EDI, ESP |

SUB ЕВХ, ЕАХ |

|

4 |

Косвенная регистровая |

[ЕАХ], [ЕВХ] [ЕСХ], [EDX] [ESI], [EDI] [ESP] |

MOV ЕАХ, [ЕВХ] |

|

5 |

Базовая со смещением |

[B]+d |

СМР ЕАХ, [EBP+12A2451Bh] |

|

6 |

Базовая индекс ная без смещения |

[B+I*S] |

MOV ЕВХ, [EBP+ESI*4] |

|

7 |

Базовая индекс ная со смещением |

[B+I*S]+d |

MOV ЕАХ, [EBP+ESI*8+35h] |

|

Таблица 3.3 – Кодировка байта SIB

REG |

Операнд 1 |

MOD |

BASE |

Операнд 2 |

000 |

Регистр EAX/AX/AL |

00 |

000 |

Память DS:[ЕАХ+(ss*iii)]

|

001 |

Регистр ECX/CX/CL |

00 |

001 |

Память DS:[ЕСХ+(ss*iii)]

|

010 |

Регистр EDX/DX/DL |

00 |

010 |

Память DS:[ЕDХ+(ss*iii)]

|

011 |

Регистр EBX/BX/BL |

00 |

011 |

Память DS:[ЕBХ+(ss*iii)]

|

100 |

Регистр ESP/SP/AH |

00 |

100 |

Память DS:[ЕSP+(ss*iii)]

|

101 |

Регистр ЕВР/ВР/СН |

00 |

101 |

Память DS:[d32+(ss*iii)]

|

110 |

Регистр ESI/SI/DH |

00 |

110 |

Память DS:[ЕSI+(ss*iii)]

|

111 |

Регистр EDI/DI/BH |

00 |

111 |

Память DS:[EDI+(ss*iii)]

|

|

01 |

000 |

Память DS:[ЕАХ+(ss*iii)+d8]

|

|

|

01 |

001 |

Память DS:[ЕСХ+(ss*iii)+d8]

|

|

|

01 |

010 |

Память DS:[ЕDХ+(ss*iii)+d8]

|

|

|

01 |

011 |

Память DS:[ЕBХ+(ss*iii)+d8]

|

|

|

01 |

100 |

Память DS:[ЕSP+(ss*iii)+d8]

|

|

|

01 |

101 |

Память DS:[d32+(ss*iii)+d8]

|

|

|

01 |

110 |

Память DS:[ЕSI+(ss*iii)+d8]

|

|

|

01 |

111 |

Память DS:[EDI+(ss*iii)+d8]

|

|

|

10 |

000 |

Память DS:[ЕАХ+(ss*iii)+d32]

|

|

|

10 |

001 |

Память DS:[ЕСХ+(ss*iii)+d32]

|

|

|

10 |

010 |

Память DS:[ЕDХ+(ss*iii)+d32]

|

|

|

10 |

011 |

Память DS:[ЕBХ+(ss*iii)+d32]

|

|

|

10 |

100 |

Память DS:[ЕSP+(ss*iii)+d32]

|

|

|

10 |

101 |

Память DS:[d32+(ss*iii)+d32]

|

|

|

10 |

110 |

Память DS:[ЕSI+(ss*iii)+d32]

|

|

|

10 |

111 |

Память DS:[EDI+(ss*iii)+d32]

|

|

|

11 |

000 |

Регистр EAX/AX/AL |

|

|

11 |

001 |

Регистр ECX/CX/CL |

|

|

11 |

010 |

Регистр EDX/DX/DL |

|

|

11 |

011 |

Регистр EBX/BX/BL |

|

|

11 |

100 |

Регистр ESP/SP/AH |

|

|

11 |

101 |

Регистр ЕВР/ВР/СН |

|

|

11 |

110 |

Регистр ESI/SI/DH |

|

|

11 |

111 |

Регистр EDI/DI/BH |

|

Таблица 3.3 (продолжение).

MOD |

SS |

INDEX |

00,01, 10,11 |

SS Масштабный множитель |

iii Индексный регистр |

|

SS |

Масштабный множитель |

||||

|---|---|---|---|---|---|---|

|

00 01 10 11 |

х 1 х 2 х 4 х 8 |

||||

|

|

|

||||

|

|

|

||||

INDEX |

Индексный регистр |

000 001 010 011 100 101 110 111 |

ЕАХ ЕСХ EDX ЕВХ

ЕВР ESI EDI |

3.1.2 Таблицы и дескрипторы сегментов

В i80386 определены 3 типа таблиц дескрипторов:

- таблица глобальных дескрипторов (GDT);

- таблица локальных дескрипторов (LDT);

- таблица дескрипторов прерываний (IDT).

Каждая таблица может содержать до 8192 8-байтных дескрипторов.

Для определения таблиц МП содержит соответствующие регистры (GDTR, LDTR, IDTR). Загрузка этих регистров производится командами защищенного режима LGDT, LLDT и LIDT.

Таблицы GDT и LDT могут содержать дескрипторы и вентили, IDT только

вентили (см. табл. 3.4).

Таблица 3.4. Распределение дескрипторов и вентилей

Тип дескриптора, вентиля |

Таблица дескрипторов |

||

GDT |

LDT |

IDT |

|

Дескрипторы сегментов программ Дескрипторы сегментов данных Дескрипторы сегментов состояния задач Вентили вызова Вентили задач Вентили прерываний Вентили ловушек |

* * * * * |

* *

* * |

* * * |

* - таблица может содержать данный дескриптор или вентиль

Дескрипторы сегментов - специальные 8-байтовые структуры (два двойных слова, далее обозначенные адресами О и 4), содержащие базовый адрес, размер и атрибуты сегментов. Определены четыре типа дескрипторов сегментов:

- дескрипторы сегментов программ;

- дескрипторы сегментов данных;

- дескрипторы сегментов состояния задач;

- дескрипторы таблиц локальных дескрипторов.

С учетом различных типов сегментов (совместимые с сегментами микропроцессора i80286, 32-разрядные - i80386) дескрипторы могут быть для 16- или 32-разрядного режима (см. рис. 3.3 - 3.6).

Дескриптор содержит следующие поля:

- База сегмента - 24/32-разрядное значение.

- Предел сегмента (limit) - 20-разрядное поле, определяющее максимальное смещение (offset) сегмента; может иметь байтовую или страничную гранулярность (4096 byte granular).

- G (Granularity) показывает гранулярность предела сегмента: 0=0 - байтовая гранулярность, предел может быть определен с точностью до байта (максимальный размер сегмента 1 Мбайт); G=1 - страничная гранулярность, предел определяется с точностью до страницы (максимальный размер сегмента 4 Гбайта).

- D (Default) указывает разрядность операндов и эффективных адресов: при D==0 допустимы 16-разрядные операнды и режимы 16-разрядной "адресации; при D=1 - 32-разрядные. Поэтому все существующие сегменты программ i80286 выполняются на i80386 в предположении, что D=0. По умолчанию 32-разрядный режим использует 32-разрядный размер операндов и 32-разрядные адреса, а 16-разрядный режим - 16-разрядный размер операндов и 16-разрядные адреса. Интерпретация бита D изменяется, если в команде используются префиксы размера данных и адреса (см. табл. 3.5).

- Е (Expansion Direction) определен только для сегментов данных и показывает, где содержится сегмент - в диапазоне адресов от базы сегмента вверх до его границы включительно (Е=0), или от максимального смещения (offset) вниз до границы, не включая ее (Е=1). Большинство сегментов данных имеет Е=0 ("Расширение вверх"). Сегмент данных, который поддерживает динамически расширяемый стек, должен иметь Е=1 ("Расширение вниз"). Стек данных растет вниз в направлении младших адресов памяти.

- В (Big, разряд 22) используется только для сегментов данных и влияет на сегменты, расширяемые вниз, и показывает максимальное смещение сегмента. При В=0 максимальное смещение расширяемого вниз сегмента данных имеет значение OOOOFFFFh, при В=1 - FFFFFFFFh.

В (Busy, разряд 9) используется только в дескрипторах сегментов состояния задач. В=1 означает, что данная задача в настоящее время выполняется другим процессором.

Рис. 3.3 - Дескрипторы сегмента программ

Рис. 3.4 - Дескрипторы сегмента данных

Рис. 3.5 - Дескрипторы сегмента состояния задачи

Рис. 3.6 - Дескриптор таблицы локальных дескрипторов (LDT)

Таблица 3.5 Интерпретация бита D

Значение D в дескрипторе сегмента |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

Наличие префикса размера операнда |

|

|

* |

* |

|

|

* |

* |

Наличие префикса размера адреса |

|

* |

|

* |

|

* |

|

* |

Размер операнда |

8/16 |

8/16 |

8/32 |

8/32 |

8/32 |

8/32 |

8/16 |

8/16 |

Размер адреса |

16 |

32 |

16 |

32 |

32 |

16 |

32 |

16 |

* - данный префикс присутствует в команде

Далее описываются поля, определяющие права доступа - условия доступа к сегментам, в том числе уровни привилегии и защиту от записи или чтения. Если нарушаются условия доступа к сегментам, i80386 генерирует ИС13 или ИС12 (при обращении к сегменту стека).

- Р (Present) указывает на присутствие (Р==1) или отсутствие (РЮ) сегмента в физической памяти. В персональной ЭВМ реализован принцип виртуальной памяти. При выполнении программы в оперативной памяти находятся только некоторые ее сегменты, а остальные хранятся на диске. Если происходит обращение к сегменту, который в данный момент отсутствует в памяти (Р=0), то операционная система осуществляет подкачку (свопинг) нужного сегмента с диска в оперативную память ПЭВМ.

- DPL (Descriptor Privilege Level) показывает уровень привилегии сегмента (от 0 до 3):

DPL |

Уровень привилегии |

00 01 10 11 |

0 - наиболее привилегированный (ядро ОС) 1 2 3 - наименее привилегированный (пользователь) |

Уровень привилегии текущего сегмента программ (DPL) определяет текущий уровень привилегии (CPL).

Введение уровней привилегии позволяет защитить программы операционной системы и ответственную информацию (общую базу данных) от несанкционированного доступа программ пользователя.

- A (Accessed) показывает, было ли обращение к сегменту. При обращении к сегменту бит автоматически устанавливается в 1. Операционная система, периодически анализируя его состояние в дескрипторах сегментов, может определить частоту обращения к сегменту.

- R (Readable) определен только для сегмента программ. Показывает, разрешено чтение сегмента (R=1) или не разрешено (R'=0). Обычно сегменты программ доступны только для выборки команд, и R=0; попытка произвести чтение из сегмента вызывает исключительную ситуацию.

- С (Conforming) используется только в сегментах программ. Если С=1, то сегмент программ считается подчиненным, и текущий уровень привилегии задачи (CPL) не изменяется при передаче управления этому сегменту.

- W (Writable) определен только для сегментов данных. Показывает, разре-

шена запись в сегмент (W==1) или не разрешена (W=0). Бит W предотвращает несанкционированные изменения в данных, что используется, например, для сегментов, содержащих важную информацию о статусе системы, или для общедоступной базы данных. Можно повысить эффективность системы виртуальной памяти за счет сокращения количества обращений к диску, если при замещении сегмента в оперативной памяти, в который запрещена запись, не возвращать его на диск.

3.1.2. Вентили

. Вентили - специальные восьмибайтовые структуры данных, необходимые в защищенном режиме для определения точек входа в сегменты программ. В i80386 определены четыре типа вентилей:

- вентили вызова (call gates);

- вентили ловушек (trap gates);

- вентили прерываний (interrupt gates);

- вентили задач (task gates).

Формат всех типов вентилей идентичен. Дескрипторы вентилей вызова, ловушек и прерываний содержат селектор и смещение, определяющие точку входа в сегмент программ, и права доступа; дескрипторы вентилей задач содержат только селектор, а смещение (EIP) считывается из сегмента состояния задачи (TSS).

Вентили вызова могут быть расположены только в GDT и LDT. Переход к сегменту программ на текущем уровне привилегии через вентиль вызова можно осуществить командой межсегментного перехода (JMP) или вызова (CALL); переход на более высокий уровень привилегии можно выполнить только командой межсегментного вызова (CALL). Таким образом, вентиль вызова обеспечивает доступ к сегментам, находящимся на более высоком уровне привилегии.

Вентили прерываний и ловушек могут располагаться только в IDT. Через них обрабатываются аппаратные, программные прерывания и исключительные ситуации. Формат и назначение вентилей прерываний и ловушек приведен в разделе 2.4.3.

Вентили задач могут содержаться в GDT, LDT или IDT. Переключиться на другую задачу через вентиль, расположенный в GDT или LDT, можно командой CALL или JMP. В случае размещения в IDT переключение задач может быть вызвано аппаратным или программным прерыванием, а также исключительной ситуацией.

3.2 Страничная организация памяти

Страничная организация памяти (в отличие от сегментированной, которая образует сегменты программ и данных различной длины) устанавливает фиксированный размер областей программ и данных. Расположенный на кристалле страничный диспетчер памяти обеспечивает следующие возможности:

- предоставляет пользователю возможность работать с большим адресным пространством (виртуальной памятью);

- обеспечивает защиту операционной системы и программного обеспечения пользователя;

- реализует быструю трансляцию адреса.

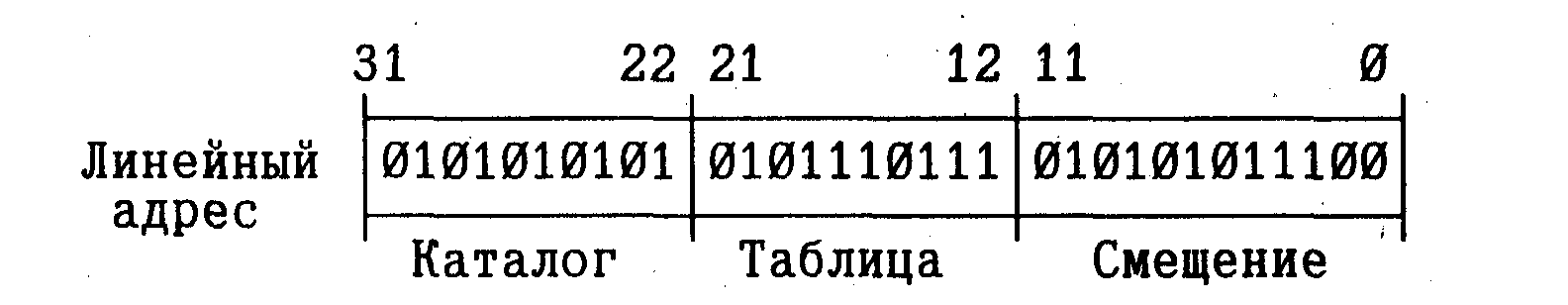

Линейное адресное пространство памяти (4 Гбайта) при страничной организации разбито на 1048576 страниц по 4096 байт каждая. Фиксированный размер всех страниц позволяет загружать любую требуемую виртуальную страницу в любую физическую страницу, что делает страничную организацию предпочтительным способом реализации виртуальной памяти.

Страничная трансляция адреса включается в защищенном режиме установкой в 1 разряда 31 регистра управления CRO и выключается его сбросом.

i80386 использует два уровня таблиц для трансляции адреса: каталог страниц и таблицу страниц.

Для определения начала каталога страниц в памяти в регистр CR3 заносится физический адрес. Для того, чтобы каталог был выровнен на границе страницы, младшие 12 разрядов CR3 должны быть установлены в нуль. Каждая строка каталога указывает на страницу, содержащую таблицу страниц. В свою очередь, каждая строка таблицы страниц указывает на страницу физической памяти.

Каталог таблиц страниц содержит 1024 строки, каждая из которых указывает на таблицу страниц и содержит перечень ее атрибутов (см. рис. 3.7).

Строка каталога и строка таблицы страниц имеют одинаковый формат и содержит следующие поля:

Рис. 3.7 - Пример трансляции линейного адреса в физический

- Адрес таблицы страниц (адрес страницы) определяет старшие 20 разрядов физического базового адреса таблицы страниц (страницы). Поскольку таблица страниц выровнена по границе страницы в физической памяти (т.е. по 4096-байтовой границе), младшие 12 разрядов ее базового адреса - нули.

- Для OS-3 разряда, выделенные под использование операционной системой (OS) и автоматически не изменяющиеся. Дополнительно к трем разрядам для хранения всей информации о таблицах страниц (страницах) операционная система может создать отдельный массив в памяти.

- Бит D указывает, производилась ли запись в какую-либо из 1024 страниц (в соответствующую страницу), обслуживаемых данной строкой (D=1), или нет (D=0). D=1 означает, что копия по крайней мере одной из страниц, хранящаяся на диске, устарела, и программа супервизора должна записать соответствующую страницу на диск перед заменой ее в памяти.

- Бит А показывает, производилось ли обращение (чтение или запись) по крайней мере к одной из 1024 страниц (к данной странице) (А=1) или нет (А=Ю). Служит для набора операционной системой статистики об использовании страниц.

- Бит U/S ("Пользователь/Супервизор") в общем случае указывает статус защиты, который присвоен 1024 страницам (присвоенный странице), описываемым соответствующей таблицей страниц. Полная интерпретация представлена в табл. 3.6.

Таблица 3.6 Защита, обеспечиваемая битами U/S и R/W

U/S |

R/W |

Доступ, разрешенный из уровня пользователя (CPL=3) |

Доступ, разрешенный из уровня супервизора (DPL=2, 1 или 0) |

0 0 1 1 |

0 1 0 1 |

Не разрешен Не разрешен Только чтение Чтение и запись |

Чтение и запись Чтение и запись Чтение и запись Чтение и запись |

- Бит R/W в общем случае обеспечивает защиту от записи для 1024 страниц (страницы), описываемых соответствующей таблицей страниц. Для полной интерпретации этот бит должен быть рассмотрен совместно с битом U/S (см. табл. 2.19).

Бит Р ("Наличие") указывает, находится ли в физической памяти соответствующая таблица страниц (страница) (Р=1) или нет (Р=0).

Таблица страниц содержит 1024 строки.

Разряды, заполненные нулями, должны быть сформированы во время создания таблицы страниц в памяти. Они не изменяются микропроцессором и зарезервированы для будущего применения.

В строке каталога таблиц страниц разряды U/S и R/W используются в качестве атрибутов защиты всех страниц в таблице страниц каталога. В строке таблицы страниц разряды U/S и R/W обеспечивают подобную защиту для страницы.

Правила доступа к сегментам также применяются ко всем обращениям в память. В итоге используются самые ограничивающие правила, независимо от того, являются ли они правилами обращения к сегментам или к страницам. Нужно заметить, что защита по принципу "исключительно выполнение" задается только правилами сегментного доступа.

Например, если данные размещены в сегменте данных, который можно только читать, а страница сегмента разрешена для чтения и записи, то доступ к данным разрешен только для чтения. Другой пример: если сегмент программы уровня 3 содержит страницы, помеченные как "уровень супервизора", то при CPD=3 могут быть выполнены только те страницы, которые помечены как "пользовательский уровень".

Любое обращение к памяти, выполняемое i80386, должно пройти контроль защиты на уровне сегментной и на уровне страничной адресации. Контрольные процедуры проверяют, что CPL имеет адекватный уровень привилегии для доступа к сегменту с заданным DPL и к странице с заданным уровнем U/S.

Механизм страничной организации i80386 может быть легко использован для организации виртуальной памяти. Страничную виртуальную организацию памяти поддерживает бит Р. В системе с виртуальной памятью он должен точно отображать местонахождение виртуальной страницы (в памяти, на диске).. Операционная система должна следить за состоянием битов Р. МП i80386 не изменяет, но автоматически проверяет его состояние в каталоге таблиц страниц и в таблице страниц при каждом обращении в память. Если и в каталоге, и в таблице Р=1, то страница находится в оперативной памяти, и производится трансляция адреса. Если в каталоге или в таблице Р=0, обращение к памяти не выполняется, ситуация квалифицируется как ошибка страницы, и микропроцессор генерирует исключительную ситуацию. Выполнение команды, вызвавшей исключительную ситуацию, может быть возобновлено после того, как нужная страница будет загружена в физическую память, а в таблицу трансляции будет помещен адрес физической страницы и установлен бит Р.

Когда механизм страничной адресации используется для обеспечения виртуальной памяти, большая часть линейного адресного пространства в физической па-мяти отсутствует. Однако некоторые программы и данные должны всегда находиться в оперативной памяти.

В системе со страничной памятью в ОП должен оставаться каталог таблиц страниц, к которому, как к таблице первого уровня, обращаются, когда требуются таблицы страниц.

В ОП должна находиться программа, которая переносит необходимые страницы в физическую память. В противном случае ни одна страница не сможет быть перенесена в физическую память без того, чтобы не вызвать исключительную ситуацию "Ошибка страницы" (ИС14), программа обслуживания которой также должна быть в памяти.

В оперативной памяти должны быть IDT (там расположены вентили вызова программ обработки исключительной ситуации), GDT (содержит дескрипторы сегментов программы обслуживания и данных), TSS (содержит указатель стека для уровня привилегии О), сам стек и таблицы страниц, используемые при трансляции адреса для IDT, GDT, TSS, стека уровня О и сегментов программы обслуживания и данных. Все эти структуры можно расположить в одной таблице страниц.

Для ускорения процесса трансляции адреса i80386 имеет быструю кэш-память, содержащую последние (по времени использования) результаты трансляции адреса и называемую буфером ускорения трансляции TLB (Translation Lookaside Buffer). TLB хранит 32 значения оттранслированных номеров страниц, соответствующих 32-м номерам виртуальных страниц. При этом приблизительно в 98-99 % случаях обращения в память трансляция адреса страницы может быть заменена быстрой ассоциативной выборкой из TLB.

^ В i80386 предусмотрены средства, обеспечивающие тестирование TLB с помощью двух регистров - TR6 и TR7, подробное описание которых дано в разделе 2.1.2.4.

Перед тестированием нужно отключить механизм страничной трансляции (сбросить бит PG в регистре CRO).

Тестирование начинается с подготовки TLB: командой MOV TR7, Rn в регистр TR7 загружается физический адрес (при этом PL=1, a REP равен номеру блока), а в регистр TR6 командой MOV TR6, Rn - линейный адрес (при С=Ю) и соответствующие атрибуты проверки.

Для инициализации режима поиска в TLB в регистр TR6 загружается линейный адрес, по которому осуществляется проверка (при 0=1). Анализ содержимого регистров (TR6 и TR7) позволяет сделать вывод о правильности функционирования TLB (при PL=1).