- •1) Логические элементы. Таблицы соответствия, переключательные функции.

- •2) Кнф и днф переход от одной формы к другой

- •4) Карты Карно

- •5) Rs триггер на элементах и-не

- •6) Rs триггер на элементах или-не

- •7) Синхронный двухтактный rs – триггер

- •11) Регистры последовательный и параллельный

- •12) Трехразрядный последовательный регистр

- •13) Универсальный регистр

- •14) Суммирующий счетчик с последовательным переносом

- •15)Вычитающий счетчик с последовательным переносом

- •16) Трехразрядный реверсивный счетчик на 2-х тактном т-триггере

- •17) Счетчик со сквозным переносом

- •18) Кольцевой счетчик

- •19) Дешифраторы

- •20) Прямоугольный дешифратор.

- •21) Каскадный дешифратор.

- •22) Шифраторы

- •23) Сумматоры

- •24) Полусумматор

- •25) Мультиплесоры

- •26) Демультиплексоры

- •27) Зу эвм. Иерархическая структура памяти эвм

- •28) Зу с непосредственной адресацией

- •29) Сверхоперативное зу с непосредственной адресацией

- •30) Ассоциативное зу

- •31) Созу с ассоциативной адресацией

- •32) Комбинационное алу магистрального типа

- •33) Накапливающее алу

- •34)16-Разрядное универсальное алу

- •35) Алу для сложения чисел с фиксированной запятой

- •36) Алу для умножения чисел с фиксированной запятой.

- •37)Четыре способа умножения чисел с фиксированной запятой в алу

- •38) Центральное устройство управления процессором

- •39) Основные характеристики системы прерывания и диаграмма прерываний

- •40) Блок прерываний процессора

- •41) Блок синхронизации процессора.

18) Кольцевой счетчик

Счетчик – это узел ЭВМ предназначенный для счета входных сигналов, и хранения кода подсчитанных сигналов

Используется для выдачи циклического хода. При разрыве обратной связи счетчики могут быть использованы как суммирующие счетчики с последовательным переносом.

Ф ункциональная

схема трехразрядного кольцевого счетчика

на JK

– триггерах.

ункциональная

схема трехразрядного кольцевого счетчика

на JK

– триггерах.

Входы S – независимые входы предварительной установки счетчика.

R – исходная установка счетчика в нулевое состояние.

t1 – начальный момент времени.

Т – входной счетный сигнал.

Q – выходы.

После установки всех разрядов в 0-ое состояние, по входам х1…х3 можно установить любой двоичный код счета.

S – установка счетчика либо в нулевое

либо в единичное состояние.

– установка счетчика либо в нулевое

либо в единичное состояние.

Х1…Х4 – установка кода.

С – вход синхронизации.

+1,-1 – счетные входы, соответственно для суммирующего и

вычитающего режима.

0…3 – информационные выходы.

Р – выход переноса.

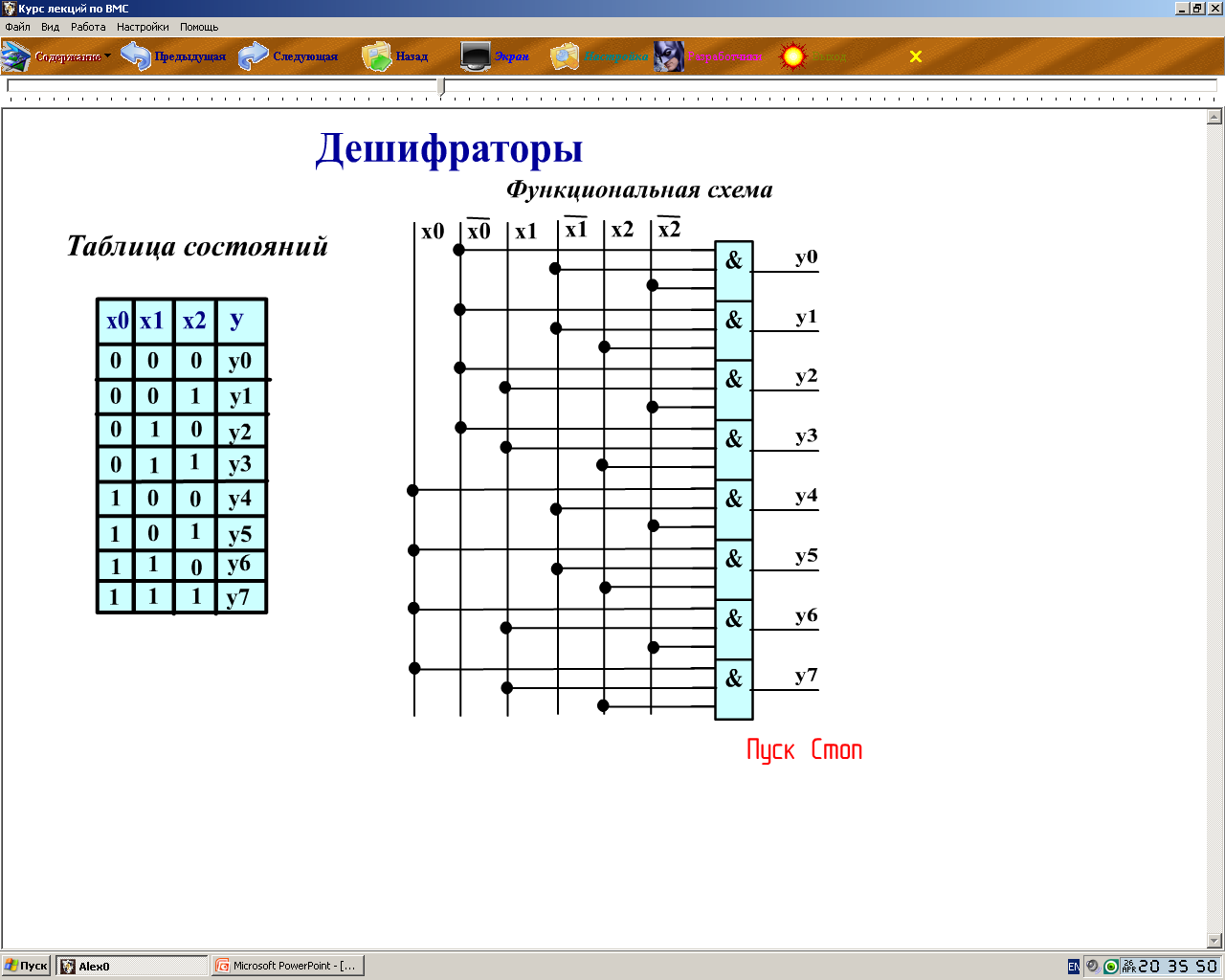

19) Дешифраторы

!!!Дешифратор(кодер)- узел ЭВМ, который имеет n-входов и 2n выходов. Определенные комбинации входных сигналов соответственно единичный сигнал на одной из выходных шин. Дешифраторы бывают: матричные(базовые)-2 входа 4 выхода, пирамидальные(3 входа-8 выходов) и прямоугольные-(4 входа- 16 выходов).

Д. могут быть построены на элементах И. и могут перейти на элементы ИЛИ-НЕ.

X0 |

X1 |

X2 |

y |

0 |

0 |

0 |

y0 |

0 |

0 |

1 |

y1 |

0 |

1 |

0 |

y2 |

0 |

1 |

1 |

y3 |

1 |

0 |

0 |

y4 |

1 |

0 |

1 |

y4 |

1 |

1 |

0 |

y6 |

1 |

1 |

1 |

y7 |

20) Прямоугольный дешифратор.

(4 входа, 16 выходов)

Дешифратор(кодер)- узел ЭВМ, который имеет n-входов и 2n выходов.

В прямоугольных - осуществляется ступенчатая дешифрация. Входное слово разбивается на группы разрядов и каждая из групп обрабатывается матричным дешифратором. На второй ступени дешифрации (конечной или промежуточной) образуется произведение сигналов, поступающих из первой ступени. Пример прямоугольного дешифратора представлен на рис. 2.

Рис. 2 Прямоугольный дешифратор на 4 входа

Особенностью пирамидальных дешифраторов является легкость наращивания количества входов, недостатком – аппаратная избыточность.

Кроме того, известны дешифраторы, переводящие код 1248 в код семи сегментного индикатора, обеспечивающего свечение соответствующих сегментов на поле индикатора. На индикаторе при этом появляется десятичное число от 0 до 9.

21) Каскадный дешифратор.

Дешифраторы - Это комбинационные схемы с несколькими входами и выходами, преобразующие код, подаваемый на входы в сигнал на одном из выходов. На выходе дешифратора появляется логическая единица, на остальных — логические нули, когда на входных шинах устанавливается двоичный код определённого числа или символа, то есть дешифратор расшифровывает число в двоичном, троичном или k-ичном коде, представляя его логической единицей на определённом выходе. Число входов дешифратора равно количеству разрядов поступающих двоичных, троичных или k-ичных чисел. Число выходов равно полному количеству различных двоичных, троичных или k-ичных чисел этой разрядности.

Для n-разрядов на входе, на выходе 2n, 3n или kn. Чтобы вычислить, является ли поступившее на вход двоичное, троичное или k-ичное число известным ожидаемым, инвертируются пути в определённых разрядах этого числа. Затем выполняется конъюнкция всех разрядов преобразованного таким образом числа. Если результатом конъюнкции является логическая единица, значит на вход поступило известное ожидаемое число.

Из логических элементов являющихся дешифраторами можно строить дешифраторы на большое число входов. Каскадное подключение таких схем позволит наращивать число дифференцируемых переменных.